Устройство для определения параметров ошибок дискретного канала связи

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение точности определения параметров ошибок дискретных каналов связи с изменяющимися во времени х-ками, а также уменьшение времени вхождения в синхронизм с входным сигналом дискретного канала связи. Устр-во содержит эл-ты И 2 и 7. датчик 3 эталонных сигналов, блок 4 сравнения, блок 6 фазирования, счетчики 8 и 9 ошибок, счетчик 13 времени, делитель 14 частоты, блок 16 вычисления (БВ) распределений ошибок методом последовательного суммирования, триггер 17 и БВ 19 распределений ошибок методом экспоненциального сглаживания. Цель достигается введением БВ 16 и 19, определяющих наличие распределения ошибок, что позволяет однозначно выбрать оптимальный код для данного канала связи. 2 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„74861 (51)4 Н 04 ? 11/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Фис.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4273858/24-09 (22) 02.07.87 (46) 23.04.89. Бюл. Р 15 (71) Всесоюзный научно-исследовательский институт радиовещательного приема и акустики им. А.С.Попова и

Ленинградский электр от ехнический и нститут связи им.проф.M.À,Áoí÷-Бруевича (72) И.П. Григорьев, P. Э. Гут, И. С.Израилит, М.Я.Лесман, М.Д.Миневич и В.И.Норкин (53) 621.396.664(088.8) (56) Авторское свидетельство СССР

Р 535743, кл. Н 04 В 3/46, 1974.

Авторское свидетельство СССР

9 786031, кл. Н 04 L 1/10, 1978. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТР0В ОШИБОК ДИСКРЕТНОГО КАНАЛА

СВЯЗИ (57) Изобретение относится к технике связи. Цель изобретения — повышение точности определения параметров ошибок дискретных каналов связи с изменяющимися во времени х-ками, а также уменьшение времени вхождения в синхронизм с входным сигналом дискретного канала связи. Устр-во содержит эл-ты И 2 и 7, датчик 3 эталонных сигналов, блок 4 сравнения, блок 6 фазирования, счетчики 8 и 9 ошибок, счетчик 13 времени, делитель 14 частоты, блок 16 вычисления (БВ) распределений ошибок методом последовательного суммирования, триггер 17 и HB 19 распределений ошибок методом экспоненциального сглаживания. Цель достигается введением БВ 16 и 19, определяющих наличие распределения ошибок, что позволяет однозначно выбрать оптимальный код для данного канала связи. 2 з.п.ф-лы, 2 ил.

1474861

Изобретение относится к технике связи и может быть использовано для определения характеристик каналов связи, Пель изобретения — повышение точности определения параметров ошибок дискретных каналов связи с изменяющимися во времени характеристиками.

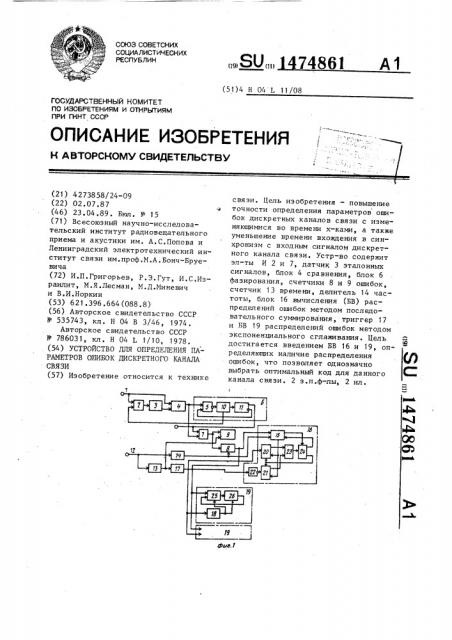

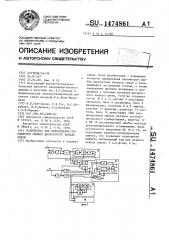

На фиг. 1 представлена структурная электрическая схема устройства для определения параметров ошибок дискретного канала связи; на фиг.2— примеры выполнения ряда блоков устройства. 15

Устройство содержит подключенный к выходу 1 дискретного канала связи первый элемент И 2, датчик 3 эталонных сигналов, блок 4 сравнения, элемент И-HE 5, входящий в состав блока 6 фазирования, второй элемент И ?, первый 8 и второй 9 счетчики ошибок, счетчик 10 совпадений и триггер 11 блокировки, входящие в состав блока 6 фазирования, подключенный к вхо-25 ду 12 тактовых импульсов устройства счетчик 13 времени, делитель 14 частоты, узел 15 управления, входящий в состав блока 16 вычисления распределений ошибок методом последователь-30 ного суммирования, триггер 17, узел 18 управления, входящий в состав блока 19 вычисления распределений ошибок методом экспоненциального сглажиBBHHH второй 20 H nepBbIA 21 3епоМН нающие узлы, инвертор 22, элемент

ИЛИ 23, узел 24 последовательного суммирования, входящие в состав блока 16 вычисления распределений ошибок методом последовательного сумми- 40 рования, узел 25 суммирования результата, узел 26 взвешивания ошибок, входящие в состав блока 19 вычисления распределений ошибок методом экспоненциального сглаживания. 45

Первый счетчик 8 ошибок (фиг.2) содержит счетчик 27 и регистр 28 памяти, узел 1S управления содержит счетчик 29 и триггер 30, второй запоминающий узел 20 — дешифратор 31, элемент ИЛИ 32, ячейки 33 памяти и

50 элемент ИЛИ 34, элемент И 35 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 36 входят в состав узла 24 последовательного суммир ования.

Наличие раснр еделения, называемого

P (m, n)-характеристикой, позволяет однозначно выбрать оптимальный для данного канала связи код, т.е. является необходимым и достаточным для этого условием.

Устройство работает следующим образом.

Контрольная цифровая последовательность с выхода 1 дискретного канала связи подается на вход блока 4 сравнения и через элемент И 2 на вход десятиразрядного датчика 3 эталонных сигналов. С первого разряда датчика 3 эталонных сигналов (вырабатывающего копию контрольной последовательности, но с произвольным расположением ее на оси времени) сигналы поступают на второй вход блока 4 сравнения, который управляет работой блока 6 фазирования. Это управление производится по следующему алгоритму.

Если сигнал, пришедший по каналу связи, совпадает с сигналом, пришедшим с первого разряда датчика 3 эталонных сигналов, то состояние счетчика 10 совпадений увеличивается на единицу, в противном случае счетчик

10 обнуляется, а входной сигнал пе«: реписывается в первый разряд датчи-. ка 3 эталонных сигналов. В результате, при отсутствии ошибок в сигнале, пришедшем по каналу связи в течение любых 10 последовательных тактов (т.е. равных числу разрядов датчика 3 эталонных сигналов), датчик 3 устанавливается в состояние, при котором он выдает с выхода своего первого разряда сигнал, синхронный с принимаемым а счетчик 10 совпадений находится в состоянии, соответствующем числу неискаженных посылок, пришедших после последней ошибки. При записи неискаженных посылок счетчик

10 совпадений выдает сигнал на элемент И 2, запрещающий поступление сигналов канала связи на вход датчика 3 эталонных сигналов. Далее, когда счетчик 10 совпадений находится в состоянии, соответствующем определенному числу неискаженных посылок (для частного случая конкретной реализации равному 32), то принима.ется решение о начале синхронизации и включается триггер 11 блокировки, отключающий вход счетчика 10 совпадений подачей запрещающего сигнала через элемент И-НЕ 5 и открывающий через элемент И 7 вход счетчика 8 ошибок в кодовой комбинации для поступающих сигналов с блока 4 сравнения и разрешающий работу счетчика

14 74 861

9 полного количества ошибок. В конце отмеренного количества тактов входной частоты, определяемого делителем

14 частоты на и содержимое счетчика

8 ошибок в кодовой комбинации переписывается в регистр перезаписи, входящий в состав счетчика 8, последний обнуляется и тем самым подготовлен к новому подсчету числа ошибок в следующей кодовой комбинации длиной и. В зависимости от числа ошибок (числа m) регистр перезаписи определяет соответствующий адресный вход запоминающих узлов (ЗУ) 20 и 21 блока. 16 вычисления распределений ошибок Р(ш, n)-характеристик) методом последовательного суммирования. Два запоминающих узла используются для того, чтобы за сеанс измерения, определяемый счетчиком 13 времени, с помощью триггера 17 и инвертора 22 осуществлять поочередное переключение ЗУ 20 и 21 либо в режим вычисления Р(ш, n)-характеристик, либо в 25 режим хранения и выдачи вычисленного значения P(m, и)-характеристик. Каждый цикл измерения ЗУ 20 и 21 меняют режим работы, что позволяет производить одновременно подсчет текущего значения P(m, п)-характеристики и, например, отображение на инцикаторной панели значения P(m, n)-характеристик за предыдущий сеанс измерений. Для конкретности положим, что триггер 17 установил ЗУ 20 в режим

35 вычисления P(m, n)-характеристик, а

ЗУ 21 — в режим хранения предыдущего вычисления. Тогда сигналом, соответствующим числу ошибок в кодовои комбинации, счетчик 8 каждые и тактов выдает разрешение на перезапись содержимого, хранящегося по этому адресу ЗУ 20, в узел 24 последовательного суммирования, где записанное число инкрементируется (добавляется единица) и переписывается по тому же адресу в ЗУ 20. Если при операции инкрементирования возник перенос, то по сигналу узла 15 управления адрес

ЗУ 20, определенный счетчиком 8, увеличивается на единицу и описанная процедура с узлом 24 последовательного суммирования повторяется.

Таким образом, в ЗУ 20 оказывается записанным количество ошибок m в кодовой комбинации длиной n, а за весь сеанс измерения, определяемый счетчиком 13 времени по определенным группам адресов ЗУ 20, — вычисленные P(m, п)-характеристики °

Одновременно с вычислением P(m, п )-характеристик методом последовательного суммирования в блоках 19 происходит вычисление P(m, n )-характеристик методом экспоненциального сглаживания, которое происходит непрерывно каждые п тактов.

При этом по сигналу счетчика 8 из узла 25 суммирования результата извлекается ранее вычисленное значение

P(m, n )-характеристик Б;,, которое поступает на вход узла 26 взвешивания ошибок в обратном коде, где инкрементируется с целью получения дополнительного кода числа S ... необходимого для того, чтобы произвести вычитание, которое заменяется сложением с числом в дополнительном коде. Следующим тактовым импульсом, вырабатываемым узлом 18 управления, разрешается умножение числа S; на

2 1 в узле взвешивания ошибок, что означает просто сдвиг на 1 разрядов числа S в сторону старших разрядов. С приходом третьего тактового импульса узла 18 управления на узел

25 суммирования результата значение числа Х (равное 0 или 1), записанное в счетчике 8, поступает в узел

26 взвешивания ошибок, где происходит суммирование Х;+ 2 S;,-S., и умножение на 2 . Поскольку деление на j эквивалентно сдвигу всего числа на j разрядов в сторону младших разрядов, то это деление осуществляется записью в узел 25 суммирования результата вычисленной суммы со сдвигом на j разрядов. С приходом четвертого тактового импульса на узел 25 в нем устанавливается значение очередного вычисления Р(ш, n)характеристик — S „

Как и при любых статистических измерениях, .точность определения

P(m, n)-характеристик тем больше, чем дольше время анализа, определяемое счетчиком 13 времени. .Показания счетчика 9 полного коли чества ошибок могут быть использова,ны для определения средней вероятности ошибок, что, особенно в случаях, когда изменение характеристик канала незначительно, представляет определенный интерес.

При изменении заданных параметров (вида эталонной последовательности, 5 . 147486 е длины кодовой комбинации и, времени сеанса измерения, величины р= 2 числа ш в Р(ш, n)-характеристике) устройство изменяется только количественно, но по-прежнему реализует5 ся в рамках структурной электрической схемы фиг. 1. В частности, с изменением вида эталонной последовательности, т.е. описывающего ее многочлена, может понадобиться больше или меньше регистров сдвига в датчике 3, с изменением и меняется число разрядов делителя 14. Необходимость в измерении не одной, а нескольких P(m, n )-характеристик в случае вычисления методом последовательного суммирования определяет емкость

ЗУ 20 и 21, соответствующие адресные входы которых соединены с соот- 20 ветствующими выходами регистра счетчика 8, а в случае вычисления P(m, n)-характеристик методом экспоненциального сглаживания приводит к необходимости иметь не один, а несколько блоков 19 вычисления, каждый их которых соединен с соответствующим выходом регистра перезаписи счетчика 8, причем остальные входы этих блоков запареллелены. Наконец, изменение величины j приводит к увеличению числа обрабатываемых разрядов узла 25 суммирования результата и узла 26 взвешивания ошибок.

Формула изобретения

1 ° Устройство для определения параметров ошибок дискретного канала связи, содержащее последовательно соединенные датчик эталонных сигналов и блок сравнения, второй вход которого является входом сигнала с выхода дискретного канала связи, блок фазирования, первый элемент -И, последовательно соединенные второй элемент И и первый счетчик ошибок, счетчик времени, вход которого соединен с входом делителя частоты и является входом сигнала источника тактовых импульсов, триггер, о т л и ч а ю— щ е е с я тем, что, с целью повышения точности определения параметров ошибок дискретных каналов с изменяющимися во времени характеристиками, введены блок вычисления распределений ошибок методом последовательного суммирования, первый вход которого соединен с выходом первого счетчика

1 ошибок, второй вход соединен с выходом делителя частоты и другим входом первого счетчика ошибок, третий и четвертый входы соединены с выходом триггера, блоки вычисления распределений ошибок методом экспоненциального сглаживания, первые входы которых соединены с выходом первого счетчика ошибок, вторые входы которых соединены с выходом триггера, при этом первый вход первого элемента И соединен с.вторым входом блока сравнения, второй вход соединен с первым выходом блока фазирования, а выход подключен к входу датчика эталонных сигналов, выход блока сравнения подключен к входу блока фазирования и к первому входу второго элемента И, второй вход, которого соединен с вторым выходом блока фазирования, а выход подключен к первому входу вторorо счетчика ошибок, второй вход которого соединен с выходом счетчика времени, подключенным к входу триггера.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок вычисления распределений ошибок методом последовательного суммирования содержит последовательно соединенные инвертор, первый запоминающий узел, элемент ИЛИ, узел последовательного суммирования, узел управления и второй запоминающий узел, при этом первый выход узла управления подключен к второму входу первого запоминающего узла, третий вход которого и второй вход второго запоминающего узла соединены с вторым выходом узла последовательного суммирования, выход второго запоминающего узла подключен к другому входу элемента ИЛИ, второй выход узла управления подключен к второму входу узла последовательного суммирования, первый и второй входы узла управления являются первым и вторым входами блока вычисления распределений ошибок методом последовательного суммирования, третьим и четвертым входами которого являются соответственно третий вход второго запоминающего узла и вход инвертора.

3. Устройство по пп. 1 и 2, о тл и ч а ю щ е е с я тем, что, с целью. уменьшения времени вхождения в

Р синхронизм с входным сигналом дискретного канала связи, блок фазиро1474861

От

Ое

Составитель А. Сеселкин

Редактор И. Шмакова Техред Л.Олийнык Корректор Э. Лончакова

Заказ 1912/57 Тираж 627 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д.-4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина,101 вания выполнен в виде последовательно соединенных элемента И-НЕ, счетчика совпадений и триггера блокировки, при этом первый вход элемента

И-НЕ является входом триггера блокировки, прямой выход которого является вторым выходом блока фазирования, а второй выход счетчика совпадений является первым выходом блоха фазирования,