Устройство для восстановления работы процессора

Иллюстрации

Показать всеРеферат

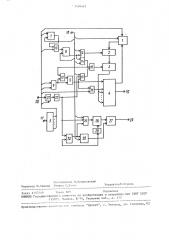

Изобретение относится к вычислительной технике ,в частности, к устройствам для восстановления работы процессора, может быть применено в процессорах малой и средней производительности с реализованным режимом диагностики и является усовершенствованием изобретения по а.с. N 1179342. Цель изобретения - повышение достоверности за счет обеспечения возможности распознавания причин, вызвавших ошибку при обработке данных в процессоре, и автоматического перевода процессора в режим диагностирования для локализации отказа. Устройство для восстановления работы процессора содержит блок локальной памяти, три регистра, коммутатор, дешифратор микрокоманд, восемь схем И, пять триггеров, таймер, счетчик, элемент задержки. В режиме обработки команд при наличии ошибки устройство повторяет выполнение микрокоманды, исполненной с ошибкой. При многократной ошибке устройство автоматически вызывает диагностическую программу, которая генерирует специальные коды для локализации неисправности. 1 ил.

Ффъ

СОЮЗ СОВЕТСНИХ

СОЫИАЛИСТИ4ЕСНИХ

РЕСПУБЛИН

А2 (gy) 4 G 06 F 11/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГННТ СССР (61) 1179342 (21) 432!426/24-24 (22) 14.09.87 (46) 30,04,89. Бил, ¹ 16

{72) А.И.Заяц и С.В.Яковлев (53) 681.3(088,8) (56) Авторское свидетельство СССР

¹ 1179342, кл. G F 11/00, 1984. (54) УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ

РАБОТЫ ПРОЦЕССОРА (57) Изобретение относится к вычислительной технике, в частности к устройствам для восстановления работы процессора, и может быть применено в процессорах малой и средней производительности с реализованным режимом диагностики и является усовершенствованием изобретения по а.с. № 11i .342. Цель изобретения — повыИзобретение относится к вычислительной технике и может быть применено в процессорах дри диагностировании.

Цель изобретения — обес.печение воэможности распознавания причин, вызвавших ошибку при обработке данных, и агтомятичесYoiо перев да устройства в режим (IH;IT".-:.nс чровяния для локали,ÿïèè с>ткязя.

На чертеже приведена " òpóêòópíàÿ схема предлягае".Inго ус.тройс:твя для воссTяноп«iения p:1б!) сI I !ID: »!ГГ t)pя .

УстройстRo cn:;n и, б к 1 локяль—

НОй П ЧМЯ И I>:,,I î;»I, >с II(: «П i РЕ— с гистр 3 понт, ..::. :с ;" :. ат; и

„,,ЯЦ„„1476467 шение достоверности зя счет обеспечения возможности ряспс.зн-:âÿí Iÿ причин, вызвавших ошибку при обработке данных в процессоре, и явтомятического переводя процессора в режим диагностирования для локализации отказа. Устройство для восстановления работы процессора содержит блок локальной памяти, -.pè регистра, коьж;— татар, дешифратор микрокомянд, восемь схем И, пять триггеров, таймер, счетчик, элемент задержки. В режиме обработки команд при наличии ошибки устройство повторяет выполнение мнкрокоманды, испол..енной с стщбкой

При многократной ошибке устройство автоматически Bblÿi:íàåò диагностическую прогрям.у, которая генерирует специальные копы для локализации неисправности. 1 ил.

Вил

4-ь дешифратор 5 микрокомянд, пеовый триггер 6, второй триггер 7, третий триггер Я,четвертый триггер 9, первый

10, второй 11, третий 1":., четвертый

13, пятый 14 и шестой 15 элементы

И, первый элемент ИЛИ 16, гхоп 17 микрокоманд устройства, I-,"ä 18 син— хронизапии устройства, >Ri. о.-.ну в п!Hну

) 9, с Tpoòë!.I.RR ° вхо -т 70 (>I: »i ки pic ройства, регистр 21 ош о:;, гторой элемент ИЛИ 2?, пять й;.рпг "cp 23, ) седьмой злемен-. И "-, твй р 25 счетчик 26. вс.симой -,е ., П 7, элемечт 28 RëR ;; I> ;I!I., гыхс.".. " ч"-ова ди— агностик. . с Грей я 3, !» I : и 3 преднязня е» ц.-... р; зр I,Rn.:.« .;ас о гь>

1476467 таймера по сигналу ошибки, зафиксированной в регистре 2!.

Седьмой элемент И 24 обеспечивает прохождение импульса с выхода элемента ИЛИ 22 при наличии ошибки в ре5 гистре 21.

Таймер 25 определяет время„ в течение которого осуществляется подсчет количества ошибок, зафиксирован- !0 ных в регистре 21.

Счетчик 26 производит подсчет количества ошибок, возникающих при обработке команд, за время определения таймером 25. 15

Восьмой элемент И 27 коммутирует на выход 29 сигнал, обеспечивающий вызов микрокоманды, автоматически переводящей устройство в режим диагностирования, 20

Устройство работает следующим образом.

Под управлением микрокоманд, код которых поступает на дешифратор 5 микрокоманд, каждая микрокоманда за- 25 дает два операнда в блоке 1 локальной памяти и функцию выполняемую над ними. Запись результата производится по адресу одного из операндов.

Устройство работает в двух режимах: обработки команд и диагностическом.

Режимы работы задаются установкой первого RS-триrrepa 6 при дешифра— ции микрокоманды. Режим обработки команд осуществляется установкой пер- вого RS-триггера 6 в нулевое состоя— ние, это вызывает установку в нулевое состояние четвертого триггера

9, в результате разрешается подача импульса записи в регистр 3 повто- 40 рения через шестой элемент и микро.программно управлять коммутатором 4.

В режиме обработки команд для возможного восстановления работоспособности процессора требуется сохранять 45 адрес операнда, для этого в первой фазе выполнения каждой микрокоманды операнд из блока 1 локальной памяти записывается в буферный регистр 2 по сигналу с выхода четвертого элемента И 13, содержимое буферного регистра 2 записывается в регистр 3 повторения во второй фазе выполнения микрокоманды, совмещенной с первой фазой слецуюшей микрокоманды, т..е. после записи операнда в регистр 3 со— держимое буферного регистра 2 обно— вляется. Информация в регистр 3 повторения записывается по сигналу с выхода шестого элемента И 15, поступающего на вход разрешения записи в регистр 3 повторения через первый элемент ИЛИ 16. Если не произошло ошибок в ходе выполнения микрокоманды, то аналогичным образом обеспечивается реализация следующих микрокоманд.

Если в результате выполнения микрокоманды обнаружена ошибка, то уста— навливается в единичное состояние один из разрядов регистра 21 ошибок по сигналу, поступающему на вход 20 ошибки устройства. При этом сигнал с выхода второго элемента ИЛИ 22 блокирует поступление стробирующих сигналов на вход разрешения записи в регистр 3 повторения через шестой элемент И 15 и первый элемент ИЛИ 16.

Таким образом, в регистре 3 повторения сохраняется операнд, относящийся к микрокоманде, выполненной со сбоем.

В это же время сигнал ошибки с выхода второго элемента ИЛИ 22 устанавливает в единичное состояние пятый триггер 23 и строб.с входа синхронизации устройства запускает таймер, а в счетчике 26 осуществляется подсчет поступающих на его счетный вход стробирующих импульсов, Для восстановления содержимого блока 1 локальной памяти выполняется микрокоманда записи содержимого регистра 3 повторения в блок 1 локальной памяти, после чего производится установка регистра 21 ошибок в нулевое состояние, В результате этого снимается блокировка стробов, подаваемых на вход разрешения записи регистра

3, и затем повторно выполняется микрокоманда, ранее выполненная со сбоем. Если .при повторном выполнении не произошло ошибки, то устройство продолжает работу как описано выше.

В отсутствии ошибок счетчик 26 не осуществляет подсчет, а с выхода переполнения таймера после отсчета заданного времени сигнал обнуляет счетник 26 и триггер 23 и на выходе 29 сигнал отсутствует.

Если ошибка при выполнении микрокоманды вызвана отказом, то при неоднократном выполнении этой микрокоманды после восстановления содержимого блока 1 локальной памяти с входа

20 в регистр 21 будет заносится ошибка, При этом на выходе переполнения счетчика 26 появится сигнал, который

1476467

20 после поступления сигнала с выхода таймера 25 снимается с выхода 29, обеспечивая автоматический вызов микрокоманды .диагностирования на вход 17 микрокоманд, После ее дешифрации первый триггер 6 переводится в единичное состояние и устройство переводится в режим диагностирования, который обеспечивает отыскание и локализацию отказа в проце ссоре.

В процессе выполнения диагностических процедур требуется имитировать ситуации, которые в режиме обработки команд являются запрещенными, например ошибки блоков процессора.

Для этого генерируются специальные сигналы, поступающие по выходной шине 19 устройства в узлы и блоки про— цессора.

Код диагностического воздействия формируется в блоке 1 локальной памяти и подается на второй выход коммутатора 4 при выполнении специально вызванной микрокоманды диагностирования. При дешифрации этой команды первый RS-триггер 6 и D-триггер

7 устанавливаются в единичное состояние. Требуемый код считывается из блока 1 локальной памяти и заносится в буферный регистр 2 по сигналу с вы— хода четвертого элемента И 13 при нулевом состоянии третьего Р-триггера

8, Во второй фазе выполнения этой микрокоманды производится установка третьего D-триггера 8 в единичное состояние, которое блокирует изменение содержимого буферного регистра 2 путем блокировки подача строба через четвертый элемент И 13 и разрешает прием информации в регистр 3 повто— рения из буферного регистра 2 путем выдачи строба через пятый элемент И 14 и первый элемент ИЛИ 16 на вход разрешения записи в регистр 3 повторения.Кроме этого, производится установка четвертого триггера 9 в единичное состояние, которое блокирует подачу строба на вход разрешения записи регистра 3 повторения через шестой элемент И 15 и первый элемент

ИЛИ 16, блокирует возможность микро25

50 программно управлят . коммутатором 4, закрывая второй элемент И 11, и выдает управлякший сигнал для выдачи через коммутатор 4 соnepжимого регистра 3 повторения, Информация на выходной шине 19 устройства в диагнбстическом реяиме сохраняется до тех пор пока не будет выполнена аналогичная микрокоманда, изменяющая содержимое регистра 3 повторения. Ес— ли в ходе диагностчрования выявлена причина сбоя (отказа), то в регистр

21 ошибка не записывается и устройство специальной микрокомандой переводится в режим обработки команд путем установки RS-триггера 6 в нулевое состояние.

Формула изобретения

Устройство для восстановления работы процессора по авт. св. К- 1179342, о т л и ч а ю ш е е с я тем, что, с целью повышения достоверности за счет обеспечения возможности распознавания причин, вызвавших ошибку при обработке данных, и автоматического перевода устройства в режим диагностирования для локализации отказа, в него введены пятый триггер, седьмой и восьмой элементы И, счетчик, таймер и элемент задержки, причем единичньп вход пятого триггера соединен с выходом второго элемента

ИЛИ и первым входом седьмого элемента И, второй и третий входы которого соединены соответственно с входом синхронизации устройства и выходом пятого триггера, выход которого соединен с разрешающим входом таймера, счетный вход которого соединен с входом синхронизации устройства, выход переполнения таймера подключен к вхо- ду установки в "0" пятого триггера, к первому входу восьмого элемента И и к входу элемента задержки, выход которого подключен к входу обнуления счетчика, счетный вход которого соединен с выходом седьмого элемента И, выход переполнения счетчика соединен с вторым входом восьмого элемента И, выход которого является выходом вызова диагностики устройства, j 476467

Сос гавцтел», R.Êóëèêîâñêèé

Редактор Ю.Середа «Техред !1..Iл:п.к

Корректор Н.Король

Заказ 2157/49 Гирек б6 Э Подписное

ВНИКНИ Государственного комитета по изобретениям и открытиям при и Гкит СССР

113ЦЗ Москва, Ж--35, Раушакая наб., д. 4/5 д оизводственно- цз,,а" пь < в ° омон ыг Патент, Г. жгоро i, у . p

lt l1, у r »л». Гагарина 101