Вычислительный узел цифровой сетки

Иллюстрации

Показать всеРеферат

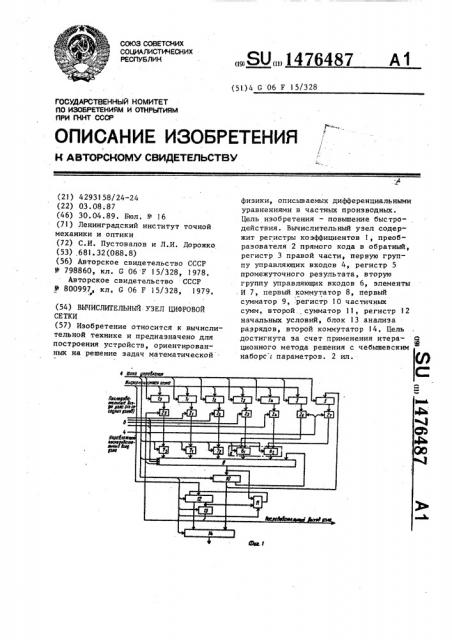

Изобретение относится к вычислительной технике и предназначено для построения устройств, ориентированных на решение задач математической физики, описываемых дифференциальными уравнениями в частных производных. Цель изобретения - повышение быстродействия. Вычислительный узел содержит регистры коэффициентов 1, преобразователи 2 прямого кода в обратный, регистр 3 правой части, первую группу управляющих входов 4, регистр 5 промежуточного результата, вторую группу управляющих входов 6, элементы И 7, первый коммутатор 8, первый сумматор 9, регистр 10 частичных сумм, второй сумматор 11, регистр 12 начальных условий, блок 13 анализа разрядов, второй коммутатор 14. Цель достигнута за счет применения итерационного метода решения с Чебышевским набором параметров. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU„„1476487 (51.) 4 G 06 F 15/328

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4293158/24-24 (22) 03.08.87 (46) 30.04.89. Бюл. V- 16 (71) Ленинградский институт точной механики и оптики (72) С.И. Пустовалов и Л.,И. Дорожко (53) 681 32(088.8) (56) Авторское свидетельство СССР

Ф 798860, кл. G 06 F 1 5/328, 1 978, Авторское свидетельство СССР

9 800997, кл. С 06 F 15/328, 1979, (54) ВЬИИСЛИТЕЛЬНЬ1Й УЗЕЛ ЦИФРОВОЙ

СЕТКИ (57) Изобретение относится к вычислительной технике и предназначено для построения устройств, ориентированньпс на решение задач математическойфизики, описываемых дифференциальными уравнениями в частных производных.

Цель изобретения — повьппение быстродействия. Вычислительный узел содержит регистры коэффициентов 1, преобразователя 2 прямого кода в обратный, регистр 3 правой части, первую группу управляющих входов 4, регистр 5 промежуточного результата, вторую группу управляющих входов 6, элементы . И 7, первый коммутатор 8, первый сумматор 9,:регистр 10 частичных сумм, второй. сумматор 11, регистр 12 начальных условий, блок 13 анализа разрядов, второй коммутатор 14. Цель достигнута за счет применения итера- а ф ционного метода решения с чебьппевским наборе параметров. 2 ил.

1476487 где i,j — индекс строки и столбца 40 сеточной области; а, (i-l, j), а„(i+1, j),аа (>. j-l).i а (i, j+1) — коэффициенты; у (1 l j) y (i+1 j) ye.(iij-l) у (1э j+1) э

yg(i, j) — значения очередного приближения функции в данном и соседних узлах (на k-ой инерции);

50 итерационные параметры (чебьппевский набор параметров); коэффициент узла (зависят от вида уравнения, способа решения уравнения); аппроксимированная правая часть; е(1,j)Изобретение относится к вычислительной технике и предназначено для построения устройств, ориентированных на решение задач математической

5 физики, описываемых дифференциальными уравнениями в частных производных, Цель изобретения — повышение быст родействия.

На фиг. l представлена структурная схема устройства; на фиг. 2 — алгоритм формирования управляющих сигналов, Вычислительный узел содержит с перпервого о пятый регистры l,-l 15 коэффициентов, с первого пб седьмой преобразователи 2,-2 „ прямого кода в обратный, регистр 3 правой части, первую группу управляющих входов 4;. регистр 5 промежуточного результата, 20 вторую группу управляющих входов 6; первый — третий элементы И 7,-7, первый коммутатор 8, первый сумматор 9, регистр 10 частичных сумм, второй сумматор 11, регистр 12 на- 25 чальных условий, блок 13 анализа разрядов и второй коммутатор 14.

Узел предназначен для решения дифференциальных уравнений .в частных производных итерационным методом с 30 чебышевским набором параметров (как явным, так и неявным).

Вычисления производятся по формуле:

У < 1 . (1 е 3 ) =У (1 ю.1 ) + "ь.1 " < 1(1- е j ) + 35

+ q„f a, (i-1, j ) y < (i-1, j ) +a, (i+ 1, j )

"У (+1 j)+a<(i j-l)y<(i j-1)+

+а (i, j+1)y (i, j+1)+q(i, j), (1) у (i 1) — последующее приближение

k+,1 функции (на (k+1)-й итерации) в данном узле.

Если принять

v (i 1 j ) = . (i э,1 ) У 1с (1 D +

+a q (i-l, j ) у (i-l,1)+а т (i+1 в j )» ,у (1+1., j)+a (i, j-1)у (i j-1)+

+а (1,)+1)у (1,5+1) э то

4 (3)

Из этого следует, что работу устройства можно разделить на два этапа: на первом этапе производится вычисление .(2), а на втором — значение функции в (i, j ) ì узле (3) íà (k+1) и итерации.

На первом этапе по инициативе сигналов из управляющего автомата коэффициенты, хранящиеся в регистрах коэффициентов, умножаются на значения функций в соответствующих узлах решетки в соответствии с алгоритмом сокращенного умножения путем поразрядного сложения содержимого регистров коэффициентов, преобразованного преобразователями кодов в соответствии с управляющими сигналами от блоков анализа разрядов данного и соседних узлов, с содержимым регистра частичных произведений. За и тактов (п-разрядность регистров) получается очередная сумма частичных произведений, После этого содержимое сдвигового регистра, в котором хранится у (1,j), уменьшается в два раза, и определяется значение очередной суммы частичных произведений.

3a п циклов умножения в регистре частичных сумм формируется значение

ur(i,j), которое переносится в ре:гистр 5, На втором, этапе производится умножение (2) и y(i,j) на Г „,, который является общим для всех узлов цифровой сетки и хранится в регистре итерационных параметров, вынесенном в управляющий автомат. Умножение производится аналогично, элементы И не пропускают информацию на многовходовый сумматор, а коммутаторы пропускают соответствующие коды содержи мого регистров 3 и 5, При умножении на старший разряд i ...,полученное произведение на сумматоре 11 суммируется со значением у (1,j), в регистре 12 получается значение очередного приближения (3), которое через

1476487 для чего по сигналу Y обнуляется регистр 10 частичных сумм, Блок 13 анализирует два младших разряда регистра 12 и вырабатывает управляющие сигналы, значения которых зависят от значений этих разрядов в соответствии с алгоритмом сокращенного умножения.

Эти управляющие сигналы поступают на последовательный выход узла, который соединен с соответствующими управляющими входами соседних узлов, на управляющие входы преобразователя кодов и на управляющий вход многовходового сумматора 9. Преобразователи 2,-2 кодов настраиваются на пропуск соответствующего кода содержимого регистров 1 коэффициентов, По сигналу У, т значения переноса всех разрядов многовходового сумматора 9 устанавливаются в "0" или "1", при этом при пропуске соответствующим преобразователем 2 кода прямого кода признак переноса устанавливается в "0", при пропуске обратного кода — в "1".

Сигнал У настраивает элементы ,И 7 и коммутатор 8 на пропуск содержимого регистров коэффициентов в соответствии со значениями управляющих сигналов из блока 13 и управляющих входов узла, Полученная сумма младших разрядов регистра 10 частич" ных сумм и регистров 1 коэффициентов поступает на вход старшего разряда регистра 10 частичных сумм, По сигналу Уд происходит сдвиг регистра 10 частичных сумм на 1 разряд вправо и запись полученной суммы в его старший разряд. По сигналу У происходит циклический сдвиг регистров 1 коэффициентов, На выходе сумматора 9 получается сумма следующих разрядов. Таким образом, через и сдвигов (тактов) в регистре,10 частичных сумм 10 получается сумма частичных произведений умножения коэффициентов на младший разряд регистра 12 и,аналогичных регистров соседних узлов.

По сигналу У в регистре 10 частичных сумм происходит алгебраический сдвиг вправо на один разряд для уменьшения частичного произведения в 2 раза. По сигналу У, регистр 12 циклически сдвигается на 1 разряд вправо для умножения на следующий разряд, После умножения на последний (старший ) разряд регистра 12 в регикоммутатор 14 может передаваться в ЭВМ;

Управляющие и осведомительные сигналы вычислительного узла:

Y, - обнуление регистра частичных

5 сумм 10;

Y, — установка признаков перекоса в сумматоре 9 в соответствии с сигналами второй группы уп-.10 равляющих сигналов;

Y — циклический сдвиг вправо на

1 разряд регистров 1 коэффициентов;

Y — сдвиг регистра частичных !5 сумм 10 вправо на 1 разряд с записью в первый разряд значения выхода сумматора 9;

Y — сдвиг регистра частичных сумм

10 на 1 разряд вправо; 20

Y< — пропуск через элементы И 7 и коммутатор 8 содержимого регистров I коэффициентов; — пропуск через коммутатор 8 на сумматор 9 содержимого 25 регистров 3 и 5;

Y — циклический сдвиг содержимого регистра 12 на 1 разряд впра-. во сдвиг содержимого регистра

12 вправо Hà 1 разряд с зал исью в с та рший раз ряд знач ения выхода сумматора 11;

Y9 — запись в регистр 5 содержимо 35 го регистра частичных сумм 10;

Y„ " циклический сдвиг вправо на

1 разряд содержимого регистров 3 и 5;

Y„,— сдвиг íà 1 разряд вправо. содержимого регистра 15; 40

YÄ вЂ” сигнал в. 3ВМ об окончании итерационного процесса;

Х, — сигнал "Пуск" от ЭВМ (начало итерационного процесса);

X, - произведено и сдвигов регист-45 ров 1,10 3 и 5;

Х вЂ” произведено и-1 сдвигов регистра 12, Вычислительный узел цифровой сетки работает следующим образом.

Все числа представлены в виде

50 дробных в дополнительном коде, По информационной шине по управляющим сигналам, передаваемым по шине управления от 3ВМ, в регистры 1 коэффициентов, и регистр 3 правой части посту55 лают значения коэффициентов, в регистр 12 начальные условия. На первом этапе происходит вычисление (2);

6487

6 выходе узла и использоваться в ЭВМ для анализа условия окончания итерационного процесса °

Фо р м ул.а

5 147 стре 10 частичных сумм получается значение (2) . В дальнейшем, по, сигналу У содержимое регистра 10 частичных сумм, т. е, полученное значение

v(i,j) переписывается в регистр 5, По сигналу У„происходит циклический сдвиг регистра 12 для восстановления значения функции V (i,j) . По сигна-. лу У, происходит обнуление регистра

10 частичных сумм, Сигнал У настраивает коммутатор

8 на пропуск содержимого регистра 5 и регистра 3, переносов в соответствующие разряды сумматора 9, На выходе многовходового сумматора 9 формируется сумма младших разрядов регистров 3, 5 и 1 О. По сигналу Yq происходит сдвиг регистра 10 частичных сумм вправо на 1 разряд с записью.в старший разряд полученной суммы, по сигналу У „ — сдвиг регистра 3 правой части и регистра 5, Таким образом, на выходе многовходового сумматора 9 получается сумма следующих разрядов, а через п тактов в регистре 10 частичных сумм находится сумма произведений содержимого регистра 3 правой части: и регистра 5 на младший разряд

При умножении на старший разряд

i „.„ по управляющему сигналу Y „ происходит сдвиг. регистра 12 с записью в старший разряд регистра результата, полученного на выходе сумматора 11, При этом на выходе сумматора 11 формируется сумма содержимого регистра 12.с получаемым результатом на выходе многовходового сумматора 9, который записывается в .регистр частичных сумм, Так как на выходе многовходового сумматора 9 получается сумма произведений 8 „, V(i,j) + „„ °

xy(i,j), то в регистр 12 заносится сумма y<(i,j)+ 7<„59,i,j)+u(i, j)), т,е, значение у „., (i,j), которое через коммутатор 14 поступает в ЭВМ, Значение приращения функции

С„„((, j) <(i, j)3 из регистра 10 частичных сумм через коммутатор 14 может быть получено на параллельном изобретения

Вычислительный узел цифровой сетки, содержащий четыре регистра коэффициентов, четыре преобразователя прямого кода в обратный, два элемен" та И, пер вый сумматор, реги стр частичных сумм, блок анализа разрядов . и регистр начальных условий, причем информационные входы регистров с первого по четвертый коэффициентов и установочные входы регистра начальных условий соединены с установочными входами узла, выходы младших разрядов с первого по четвертый регистров коэффициентов соединены с информационными входами,с первого по четвертый преобразователей прямого кода в обратный соответственно, выходы

25 первого и второго преобразователей прямого кода в обратный соединены с первыми входами первого и второго элементов И cooTветственно, выходы которых подключены к входам соответственно первого и второго слагаемых первого сумматора, выход которого соединен с входом старшего разряда регистра частичных сумм, выход младшего разряда которого подключен к входу третьего слагаемого первого

35 сумматора, выходы двух младших разрядов регистра начальных .условий соединены с информационными входами блока анализа разрядов, выход которого соединен с управляющим выходом узла и входом установки переноса первого разряда первого сумматора, вход сброса узла соединен с входом сброса регистра частичных сумм, с

45 первого по восьмой управляющие входы первой группы узла соединены соответственно с управляющим входом первого сумматора, объединенными входами синхронизации регистров с первого по четвертый коэффициентов, 50 первым управляющим входом регистра частичных сумм, вторым управляющим входом регистра частичных сумм, вторыми входами первого и второго элементов И, первым управляющим . входом регистра начальных условий, управляющим входом блока анализа разрядов и вторым управляющим входом регистра .начальных условий, о т л и1476487 ч а ю шийся тем, что, с целью повышения быстродействия, в него введены регистр пятого коэффициента, регистр правой части, регистр промежуточного результата, с пятого по восьмой преобразователи прямого кода в обратный, третий элемент И, два коммутатора и второй сумматор, причем установленные входы узла подключены к информационным входам регистра правой части и регистра пятого коэффициента, выход младшего разряда которого соединен с информационным вхо дом пятого преобразователя прямого кода в обратный, выход которого соединен с первым входом третьего элемента И, выход которого соединен .с;входом четвертого слагаемого первого сумматора, выход которого соединен 20 с входом первого слагаемого второго сумматора, выход которого соединен с, входом старшего разряда регистра начальных условий, выход младшего разряда которого соединен с входом вто- 25 рого слагаемого второго сумматора, выходы третьего и четвертого преобразователей прямого кода в обратный соединены с информационными входами первой группы первого коммутатора, первый и второй выходы которого соединены соответственно с входами пятого и шестого слагаемых первого сумматора, выход младшего разряда регистра правой: части соединен с информационным входом шестого преобразователя прямого кода в обратный, выход. которого соединен с соответствукщим информационным входом второй группы первого коммутатора, выходы регистра частичных сумм соединен с информационными входами первой группы второго коммутатора и информационными входами регистра промежуточного результата, выход младшего разряда которого соединен с информационным входом седьмого преобразователя прямого кода в обратный, выход которого подключен к соответствующему информационному входу второй группы первого коммутатора, выходы регистра начальных условий соединены с информационными входами второй группы второго коммутатора, выходы которого соединены с информационными выходами узла, выход блока анализа разрядов соединен с управляющим входом пятого преобразователя прямого кода в обратный, пятый управляющий вход первой группы узла соединен с вторым входом третьего элемента И и первым управляющим входом первого коммутатора, второй управляющий вход которого соединен с девятым управ" ляющим входом первой группы узла, десятый, одиннадцатый и двенадцатый управляющие входы первой группы узла соединены соответственно с входом синхронизации записи регистра промежуточного результата, входами синхроимпульса сдвига регистра промежуточного результата и регистра правой части, управляющими входами шестого и седьмого преобразователей прямого кода в обратный и входом установки переноса второго разряда первого сумматора, уравляющие входы второй группы узла соединены с управляющими входами с первого по четвертый преобразователей прямого кода в обратный и входами установки переноса соответственно с третьего по шестой разрядов первого сумматора, третий и

:тринадцатый управляющие входы первой группы соединены с управляющими входами соответственно регистра пятого коэффициента и второго коммутатора.

1476487

Составитель А. Чеканов

Редактор Л. Пчолинская Техред И. Ходанич КоРРектоР И. Муска

Заказ 2158/50 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент™, г. Ужгород, ул. Гагарина,101