Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной технике и может быть использовано как для измерения постоянных электрических сигналов, следующих на фоне аддитивных случайных помех, так и для определения параметров (математического ожидания) случайных процессов. Цель изобретения - повышение быстродействия - достигается тем, что в устройство, содержащее генератор 1 импульсов, генератор 4 шума, компараторы 5, 7, постоянное запоминающее устройство 9, цифроаналоговый преобразователь 13, сумматор 14, регистр 15, дешифратор 16, введены мультиплексоры 3, 10, блок 11 сравнения кодов, элемент 2 задержки, RS-триггер 8 и блок 12 задания кода. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1д1) 4 Н 03 M /46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4273510/24-24 (22) 06.04,87 (46) 30,04,89, Бкл. - !6 (71) Азербайджанский институт нефти и химии им, M,Àçèýáåêoâà (72) Т.М.Алиев, Д,И,агамиров, А,А.Тер-Хачатуров и A,З, Федорцов (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 488147, кл, G 01 R 13/02, !974, Авторское свидетельство СССР

11- 1129528, кл ° G 01 R 13/02, 1983. (54) АНАЛОГО-ЦИФРОВОЛ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относит ся к информационно-измерительной технике и может быть использовано как для изме„„Я0„„14766О9 д 1 рения постоянных электрических сигналов, следующих на фоне аддитивных случайных помех, так и для определения параметров (математическогo ожидания) случайных процессов. Цель изобретения — повышение быстр од ей ствия — достигается тем, что в устройство, содержащее генератор 1 импульсов, генератор 4 шума, компараторы 5, 7, постоянное запоминающее устройство 9, цифроаналоговый преобразователь 13, сумматор 14, регистр 15, дещифр атор 16, введены мультиплексоры 3, О, блок 11 сравнения кодов, элемент 2 задержки, FHтриггер 8 и блок 12 задания кода.

1э и, флы Зил °

1476609

35 l2 на время, равное длительности это1

Изобретение относится к информа" ционно-измерительной и вычислительной технике и может быть использ овано как для измерения постоянных электрических сигналов, в том числе действующих на фоне аддитивных случайных помех, так и для определения параметров (математического ожидания) случайных процессов, Целью изобретения является повышение быстродействия.

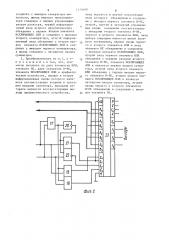

На фиг,1 приведена функциональная схема устройства; на фиг,2 — функциональная схема сумматора; на фиг.3— временные диаграммы работы устройст" ва, Пр ео бр аз о в ат ел ь содержит ге нер атор 1 импульсов, элемент 2 задержки, мул ьтиплексор 3, генер атор 4 шума, компар атор 5, элемент ИСКЛ!ОЧА1ОЩЕЕ ИЛИ

6, компаратор 7, RS-триггер 8, блок

9 задания шага, мультиплексор !О, блок 11 сравнения кодов, блок 12 задания кодов, цифроаналогoBbIH преобразов атель (IJAII) 13, сумматор 14, регистр 15, дешифратор 16, Сумматор (фиг. 2) содержит элемент

17 ИСЕЛ1ОЧА1ОЦЕЕ ИЛИ, элементы ИЛИ 18, 19, элемент НЕ 20, элементы И-HE 21, 22, арифметическое устройство 23.

На фиг.3 обозначено 24 — 28 — напряжения соответственно на выходах генератора 1, RS-триггера 8, компараторов 5, 7, ЦАП 13. Х вЂ” измеряемая величина, Переход от детерминирован10

2

1Л

Z и где Z — наибольшее значение параметра Х, Il - номер шага (тактового импульса генератора 1), является оптимальным с точки зрения минимума дисперсии ошибки, Цикл преобразования начинается с появления на выходе блока 9 начального кода, распознаваемого дешифратором 16, сигнал с выхода которого устанавливает начальное состояние регистр 15 и сбрасывает ВЯ-триггер 8, Сигнал с выхода триггера 8 поступает на управляющие входы мультиплексоров

3 и 10. При этом мультиплексор 3 подключает выход элемента 2 задержки к первому управляющему входу регистра

15, а мультиплексор 10 подключает выход компаратора 5 к четвертому входу сумматора 4. Если в момент опроса состояние компаратора 5 указывает на то, что значение входного параметра превышает уровень сигнала ЦАП 13, то число, сформированное блоком 9, складывается в сумматоре 14 с содержанием регистра 15, в противном случае оно вычитывается из содержимого регистра 15, Запись результата алгебраического суммирования в ЦАП 13 и регистр 15 производится сигналом с генератора 1, задержанным в элементе

55 ного рекима работы к стохастическому отмечен точкой 29, точками 30 — 32 показано изменение уравновешивающей величины на выходе ЦАП при детерминированном режиме в каждом такте, Точками 33 — 37 показ аны моменты, в которых знаки выходных сигналов компараторов в момент опроса совпадают в режиме стохастиче ской компенсации.

Преобразователь работает следующим образом, Синхронно поступлению импульсов генератора 1 производится опрос состояния компаратора 5 и формирования помощью блока 9 регулярной последовательности чисел Z. убывающих по опеределенному закону, В основу выбора последовательности

Е. могут быть положены различные кри1 терии, При этом ограничения накладываются лишь на характер последовательности — она не должна быть возрастающей, Например, выбор Z из ус- ловия

ro сигнала, Таким образом, при сброшенном состоянии RS-триггера 8 реализуется детерминированный алгоритм ур авновешив ания измеря емой величины сигналом с выхода ЦАП 13, причем закон ур авновешив ания з адает ся по сл едовательностью чисел S; записанных в блоке 9.

Детерминированный режим работы сохранения до момента совпадения кода на выходе блока 9 с кодом, задаваемым блоком 12 с помощью набора переключателей, Этот код задается исходя из априорных сведений об уровне 3ашумпенности сигнала и определяет ту наибольшую по величине ступень ур авновешив ающе го си гнал а, начиная с которой включается режим стохастической компенсации, Это достигается тем, что при совпадении кодов на входах блока 11 сигнал с его выхода взводит RS-триггер 8. Сигнал с выхода RS-триггера 8 переключает мультиплексоры 3 и 10, При этом вы1- 76609 ход элемента 6 подключается к первому управляющему входу регистра 15 и к управляющему входу ЦАП 13, а выход компаратора 7 подключается к четвертому входу сумматора 14, В этом режи5 ме q если в момент опроса состояние компараторов 5 и 7 указывают на то, что значение входного параметра превышает уровень сигнала ЦАП 13, а сиг-10 нал генератора 4 превышает нулевой уровень, то число, сформированное блоком 9, складывается в сумматоре

14 с содержимым регистра 15. Если же в момент опроса состояние компараторов 5 и 7 указывает на то, что значение входного параметра меньше уровня сигнала ЦАП 13, а сигнал генератора 4 меньше нулевого уровня, то число, сформированное блоком 9, вы- 20 читыв ает ся в сумматор е 14 иэ содержимого регистра 15. Запись результаг а алгебраического суммир ов ания в

ЦАП 13 и регистр 15 производится с помощью элемента 6, анализирующего состояние компараторов 5 и 7 на предмет их несовпадения.

Преобразование э аканчивается с окончанием формирования значений шага блоком 9. Результат преобразования фиксируется в регистр 15. Следующий цикл преобразования начинается с появления на выходе блока 9 начального кода, распознаваемого дешифратором 16, который устанавливает регистр

15 и ЯЯ-триггер 8 в исходное состо35 яние.

В случае измерения постоянных электрических сигналов с небольшим уровнем помех может быть задан режим, при котором .весь цикл преобразо вания будет о суще ст влят ься по средством детерминированной процедуры компенсации, Для этого необходимо в блоке 12 задать код, не совпадающий ни с одним из кодов, записанных в блоке 9, Введение указанных элементов и связей позволяет в преобразователе в отличие от прототипа реализовать в пределах каждого цикла преобразования комбинацию метода детерминированной компенсации, обладающего большим быстродействием, и метода стохастической компенсации, обеспечии

55 вающего высокую помехоустойчивость, Это повышает быстродействие преобразователя, так как уменьшает необходимое ддя обеспечения заданной точности преобразования чи Ic! шагов по сравнению с прототипом при сохранении помехоустойчивосги последнего, Ф о р м у л а и з о б р е т е н и я

1. Аналого-цифровои преобразовательь, содерж ащий цифр о ан ал о говый пр еобр аз овател ь > выход которо го соединен с первым информационным входом первого компаратора, второй информационный вход которого я вля ется входной шиной, информационные входы цифроаналогового преобразователя объединены с соответствующими информационными входами ре гистр а и соединены с соответствующими выходами сумматора, управляющий вход цифроаналогового преобразователя объединен с первым упр авляющн м вх одо м регистра, стробируюшие входы первого и второго компараторов и вход постоянного запоминающего устройства объединены и соединены с выходом генер атор а импул ьсов, пер вый инфор мационный вход второго компар атор а соединен с выходом генератора шума, второй информационный вход является шиной нулевого потенциала, выход первого компаратора соединен с первым входом сумматора, вторые входы сумматора объединены с соответствую",ими входами дешифратор а и соединены с соответствующими выходами постоянного запоминающего устройства, третьи входы соединены с со ответ ст вующими выходами регистра, выход дешифратора соединен с вторым управляющим входом регистра, о тл и ч а ющи и с я тем, что, с целью повышения быстродействия, в него введены элемент ИС1(ЛЮЧАЮЯЕЕ ИЛИ, первый и второй мультиплексоры, блок сравнения кодов, элемент задержки, Б ;- .-триггер, блок задания кода, выходы которого соединены с соответствующими. первыми входами блока сравнения кодов, вторые входы которого объединены с соответст вующими входами дешифр атор а, а выход соединен с Я входом ЕЗ-триггера, R-вход которого соединен с выходом дешифратора, а выход соединен с управляющими входами первого и второго мультиплексоров, первый и второй информационные B.:oiTo1 первого мультиплексора caenèíåíû. соответственно с выходом элемента ИС1(:1 ОЧАК111ЕЕ ИЛИ и элемента задержки, вход которого

I л 7")609 соединен с выходом генератора импул ьсов, выход первого мультиплексора соединен с первым управляющим входом регистра, первый информационный вход второго мультиплексора объединен с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом второго компар атор а, второй и нфор мационный вход объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом пер во ro компар ат ор а, а выход соединен с четвертым входом сумматор а, 2, Преобразователь по п ° 1, о тличающийcятем,что,сумматор выполнен на двух элементах ИЛИ, элементе НЕ, двух элементах И-НЕ, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ и арифметическом устройстве, первые и вторые информационные входы которого являютсяя соответ ст ве нно вторыми и тр ет ьими входами сумматора, выходами коорого являются соответствующие выходы арифме тиче с ко го у стр ой ст ва, вход переноса и пер вый унр являющий вход которого объединены и соединены с выходом первого элемента И-НЕ, второй, третий и четвертый управляю5 щие входы соединены соответственно с выходами второго элемента И-HF., первого и второго элементов ИЛИ, вход выбор а операции я вля ется шиной нул евого потенциала, первые входы первого и второго элементов ИЛИ и вход элемента НЕ объединены и соединены с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ> второй вход первого элемента ИЛИ объединен с первыми входами второго элемента И-НЕ, элемента ИСКЛОЧАЮЩЕЕ

ИЛИ и является первым входом сумматора, второй вход второго элемента

ИЛИ объединен с первым входом первого элемента И-НЕ, вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является четвертым входом сумматора, вторые входы перво го и второго элементов

И-НЕ объединены и соединены с выхо25 дом элемента НЕ, 14 76609

Корректор Э,Лончакова

Редактор О,Спесивых

Заказ 2)67/56 Тираж 885 Подпи сна е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина,101 о

0

Составитель А,Титов

Техред А.Кравчук