Синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано в радиосвязи. Цель изобретения - повышение спектральной чистоты выходных сигналов. Синтезатор частот содержит фазовращатель (Ф) 1, фазовые детекторы (ФД) 2-4, инвертирующий усилитель 5, дешифратор 6, параллельный сумматор (ПС) 7, фильтр 8 нижних частот, управляемый аттенюатор 9, г-р опорной частоты 10, счетчик 11, интегратор 22 со сбросом. Поставленная цель достигается введением новых элементов: умножителя 12 частоты, трех мультиплексоров 14,15,16, двух инверторов 17,18, N блоков интегрирования 19<SB POS="POST">1</SB>-19<SB POS="POST">N</SB>, линии задержки 21, двух ФД 23,13, фильтра 24 нижних частот и двух ПС 25,20. Для снижения уровня паразитных составляющих спектра параметры управляющего сигнала Ф1 стабилизируются тремя следящими системами, которые обеспечивают: 1 - установление начальной рабочей точки на х-ке Ф1 П - установление размаха управляющего напряжения, соответственно набегу фазы F<SB POS="POST">вх</SB> на 2П Ш-форму управляющего напряжения, компенсируя нелинейность Ф 1.4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 Н 03 В 21/02

8. t; 02Лй.1

ПАТЕЛИ i,...Ë :, ;; 3

БИБ.:, -1О

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Д BTOPCHOMY СВИДЕТЕЛЬСТВУ (54) СИНТЕЗАТОР ЧАСТОТ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР (21) 4171354/24-09 (22) 31.12.86 (46) 07,05.89. Бюл. №- 17 (72) А.Г.Воронин и И.Е.Сидоренко (53) 621.373(088.8) (56) Авторское свидетельство СССР

¹ 634446, кл. H 03 В 21/02, 25,02.77.

Авторское свидетельство СССР

¹ 1285555, кл. Н 03 В 21/02, 26.04.85. (57) Изобретение относится к радиотехнике и м.б. использовано в радиосвязи. Цель изобретения — повышение спектральной чистоты выходных сигналов. Синтезатор частот содержит фазовращатель (Ф) 1, фазовые детекторы (ФД) 2-4, инвертирующий у-ль 5, дешифратор 6, параллельный сумматор (ПС) 7, фильтр 8 нижних частот, ЛК 1478284 А 1 управляемый аттенюатор 9, г-р опорной частоты 10, счетчик 11, интегратор

22 со сбросом. Поставленная цель достигается введением новых элементов: умножителя 12 частоты, трех мультиплексоров 14, 15, 16, двух инверторов 17, 18, N блоков интегрирования 19 -1911, линии задержки 21, двух

ФД 23, 13, фильтра 24 нижних частбт и двух ПС 25, 20. Для снижения уровня паразитных составляющих спектра параметры управляющего сигнала Ф 1 стабилизируются тремя следящими системами, которые обеспечивают установление начальной рабочей точки на х-ке

Ф 1; установление размаха управляющего напряжения, соотв. набегу фазы

F на 2Г, а также форму управляющего напряжения, компенсируя нелинейность Ф 1. 4 ил, 1478284

F = Е +

ЮЫХ ВХ

Знак "+" соответствует положительной производной приращения фазы сигнала на выходе фазовращателя 1, а знак "-" отрицательной

1.

Если набег фазы в фазовращателе 1 сигнала F „ не равен 2п и форма управляющего напряжения не компенсирует нелинейность фазовращателя 1, то в сигнале Е ых присутствует паразитная фазовая модуляция, что

Изобретение относится к радиотехнике и может быть использовано в радиосвязи.

Цель изобретения — повышение спек5 тральной чистоты выходных сигналов °

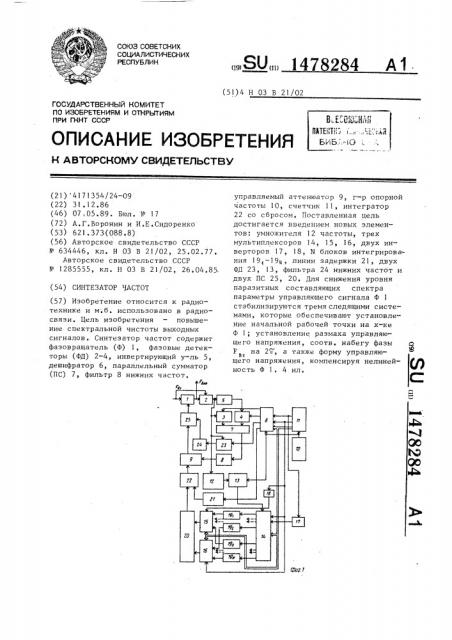

На фиг.l приведена структурная электрическая схема синтезатора частот; на фиг.2 — 4 — временные диаграммы, поясняющие работу устройства. 10

Синтезатор частот (фиг.l) содержит фазовращатель 1; первый, второй и третий фазовые детекторы 2, 3 и 4, инвертирующий усилитель 5, дешифратор

6, первый параллельный сумматор 7, 15 первый фильтр 8 нижних частот, управляемый аттенюатор 9, генератор 10 опорной частоты; счетчик ll умножитель 12 частоты, пятый фазовый детектор 13, первый, второй и третий муль- 20 типлексоры 14, 15 и 16, первый и второй инверторы 17 и 18, первый, второй, ..., .Г1-й блоки 19», 192... °, 19 интегрирования, третий параллельный сумматор 20, линию 21 эадерж- 25 ки, интегратор 22 со сбросом, четвертый фазовый детектор 23, второй фильтр 24 нижних частот, второй параллельный сумматор 25.

Синтезатор работает следующим . 30 образом.

На вход фаэовращателя 1 подается гармонический сигнал с частотой F „, а на его управляющий вход — комплексный сигнал управления в виде постоян- 35 ного напряжения, при помощи которого осуществляется выбор начальной рабочей точки на характеристике управления фазовращателем, и линейно-ломанное напряжение с частото" f. Размах 40 линейно-ломанного напряжения соответствует смещению фазы Г на 2 и из ях начальной рабочей точки на характеристике фазовращателя 1, что обеспечивает смещение частоты Г „ на + Т 45 на выходе синтезатора частоты приводит к появлению в спектре выход— ного сигнала составляющих с частотами

Гм + Кй(К = 1, 2. .. ° ).

Для снижения уровня паразитных составляющих спектра параметры управляющего сигнала фазовращателя 1 стабилизируются тремя следящими системами, которые обеспечивают установление начальной рабочей точки на характеристике фазовращателя 1 установление разд маха управляющего напряжения, соответствующее набегу фазы Г на 2Г

ВХ У а также форму управляющего напряжения, компенсируя нелинейность фазовращателя, На выходе первого фазового детектора 2 выделяется разность фаз на входе и выходе фаэовращателя 1. На фиг.3 показаны эпюры напряжения на выходе первого фазового детектора 2, когда приращение фазы на выходе фазовращателя 1 меньше 2 и (фиг.3a), равное 2 х (фиг.36), более 2 (фиг.Зв) . Когда приращение фазы равно 2 и (фиг.36), на выходе первого фазового детектора ? присутствует гармонический сигнал с частотой и и периодом Т = 1/2 ° Установление размаха управляющего напряжения, соответствующее приращению фазы на 2 7р осуществляется системой регулирования состоящей иэ второго и третьего фазовых детекторов 3 и 4, инвертирующего усилителя 5, первого параллельного сумматора 7 и первого фильтра 8 нижних частот.

Во втором фазовом детекторе 3 измеряется разность фаз между сигналом с выхода первого фазового детектора 2 (фиг.4г) и опорного сигнала с первого выхода дешифратора 6 (фиг.46)> а в третьем фазовом детекторе 4— разность фаэ между инверсией сигнала первого фазового детектора 2 (фиг,4д) и опорным сигналом с второго выхода дешифратора 6 (фиг.4в), сдвинутого относительно опорного сигнала второго фазового детектора 3

Т на — ° Для приращения фазы I х, раво2 ного 2 х, разности фаз, измеряемые во втором и третьем фазовых детекторах 3 и 4 равны, также равны напряжения на выходах фазовых детекторов

3 и 4. Эти напряжения складываются в первом параллельном сумматоре 7 с

147

55 пулей входного сигнала прь коэффициенте умножения частоты К равно 2К, Измеренное в пятом фазаном детекторе

13 фазовое рассогласование, соответствующее нечетным номерам импульсов генератора 10 опорной частоты, является лишним. Эти измерения исключаются при помощи первого мультиплексора 14, на вход разрешения которого подается через иннертор )7 сигнал с первого выхода счетчика 11 (фиг.4з), который разрывает выход пятого фазового детектора 13 с блоками 19,, 19,..., 19 ц интегрирования а время действия ложного напряжения на выходе пятого фазового. детектора 13.

Напряжение, соответствующее расгогласованию положения нулей измеряемого сигнала и четных импульсов генератора 10 опорной частоты с выхода пятдго фазового детектора 13 перез первый мультиплексор 14 поступает а вход саотнетстнующего блока 19,, !9, 19н интегрирования, «а котором накапливается напряжение, пропорциональное фазовой ошибке модуляции на соответствующем интервале между двумя соседними четными импульсами генератора 10 опорной частоты.

При прохождении сигнала через нуль (фиг,4в) с положительной производной напряжение ошибки поступает на группу блоков 19,, 19 >, 19, интегрирования, подключенных к входам второго мультиплексора 15, а для сигнала с отрицательной производной — на вторую группу блокон 19, 19,, ..., 19 „ интегрирования, подключенных к входам третьего мультиплексора 16. При помощи кода, поступающего со счетчика ll, на адресные входы второго и третьего мультиплексоров 15 и 16, выходы блоков 19,, 19, ..., 19 интегрирования последовательно подключаются к входам треть— его параллельного сумматора 20, где суммируются с разными знаками. Второй и третий мультиплексоры )5 и 16 подключаются поочередно к третьему параллельному сумматору 20. Для этого входы разрешения второго и третьего мультиплексоров 15 и 16. соответственно через инвертор 18 и непосредственно соединены с вторым выходом счетчика 11 (фиг.4и).

Таким образом, на выходе третьегс параллельного сумматора 20 формируется ступенчатое напряжение (фпг,4к), 8284

6 характеризующее отличие реальной фазавой характеристики фазовращателя

1 от линейной (фиг,2). Ступенчатое напряжение, поступая на интегратор

22, преобразуется н нем в линейноломанное, аппроксимирующее функцию, обратную фазовай характеристике фазонращателя (фиг.2 и фпг.4л). Сброс интегратора 22 в конце периода моду— ляции Т осуществляется импульсам дешифратора 6, задержанным н линии

21 задержки (фиг,4м) для того, чтобы сброс интегратора 22 не совпадал с последним четным импульсом генератора 10 опорной частоты, па которому производится определение фазоной ошибки модуляции в конце периода Т.

Выходные сигналы дешифратора 6 простробированы па длительности импульсами генератора 10 опорной частоты, поскольку импульс сброса (фиг.4м) па длительности должен быть много меньше периода Т.

Ф о р и у л а и 3 а б р е т е н и я

Синтезатор частот, содержащий фазовращатель, первый, второй, третий фазовые детекторы, инвертирующий усилитель, первый параллельный сумматор, первый фильтр нижних частот, управляемый аттенюатор, интегратор со сбросом, счетчик, генератор опорной частоты и дешифратор, причем выход первого фазового детектора соединен с первым входом второго фазового детектора и входом инвертирующего усилителя, первый вход третьего фазового детектора соединен с выходом инвертирующего усилителя, выходы второго и третьего фазовых детекторон соединены соответственно с первым и вторым входами первого параллельного сумматора, вторые входы второго и третьего фазовых детекторов соединены соответственно с первым и вторым выходами дешифратора, выход первого параллельного сумматора подключен к входу первого фильтра нижних частот, выход которого соединен с управляющим входом управляемого аттенюатора, к сигнальному входу которого подключен выход интегратора со сбросом, первый вход первого фазового детектора объединен с входом фазонращателя, выход генератора опорной частоты соединен с входом счетчика, первый выход, второй выход, 1478284 разными знаками и результирующее напряжение на его выходе равно нулю.

Когда приращение фазы Г „ отличается от 2 п, на выходе первого параллельного сумматора 7 формируется напряжение, пропорциональное фазовой ошибке. Это напряжение через первый фильтр 8 нижних частот изменяет коэффициент передачи управляемого атте †!р нюатора 9 и, следовательно, размах управляющего напряжения фазовращателя 1 (которое формируется в интеграторе 22) до тех нор, пока приращение фазы Р „ не станет равным 2ь. Система !5 регулирования размаха управляющего напряжения не чувствительна к начальной фазе Р „, поскольку в ней определяется только приращение фазы F (информация о начальной фазе 1 e,< вы в 2p читается в первом параллельном сумматоре 7).

Выделение информации о нелинейности характеристики фазовращателя 1 производится умножителем 12 25 и пятым фазовым детектором 13 из сигнала с выхода первого фазового детектора 2. Умножение частоты в К раз увеличивает число точек перехода через нуль также в К раэ (фиг.4е) за период модуляции фазы Т. Сравнивая положение точек перехода через нуль частоты с выхода умножителя 12 частоты с положением импульсов генератора

10 опорной частоты (фиг.4а) в пя35 том фазовом детекторе 13, получим и информацию о линейности фазовой характеристики фазовращателя 1. Для синхронизации начала модуляции с импульсами генератора 10 опорной

40 частоты служит система регулирования начальной рабочей точки на характеристике фазовращателя 1, которая устанавливает начальный сдвиг фаз сигналов на входах пятого фазового детек- 45 тора 13, равный нулю. Тогда в случае линейной фазовой модуляции 2 и в фазовращателе напряжение на выходе пятого фазового детектора 13 равно нулю, Если же закон модуляции отличается от линейного, но с приращением фазы, равной 2, на выходе пятого фазового детектора 13 появляется напряжение, пропорциональное ошибке модуляции ° Пятый фазовый детектор 13

55 необходимо выполнить импульсно-фаэовым.

Система регулирования начальной рабочей точки содержит четвертый фазовый детектор 23 и второй фильтр ,24 нижних частот. В четвертом фазовом детекторе 23 сравнивается фаза опорных импульсов с третьего выхода дешифратора 6 (фиг.4ж) и фаза сигнала первого фазового детектора 2 (фиг.4г) . Если раэность фаз сигналов от. лична от нуля, то на выходе четвертого фазового детектора 23 возникает напряжение, которое, пройдя второй фильтр 24 нижних частот и второй параллельный сумматор 25, подстраивает начальную рабочую точку фазовращателя 1.

Система регулирования формы управляющего напряжения состоит иэ умножителя 12 частоты, пятого фазового детектора 13, первого мультиплексора

14, блоков 19<, 19, ..., 19к интегрирования и второго мультиплексора 15, третьего мультиплексора 16 и третьего параллельного сумматора 20.

Умножитель 12 частоты должен быть широкополосным, поскольку информация о нелинейности фазовращателя содержится в высокочастотных составляющих спектра входного сигнала (если искажений нет, то сигнал на входе умножителя гармонический). Этому требованию удовлетворяет умножитель (удвоитель) частоты с характеристикой вида

Y = 2Х, который дает на выходе только постоянную составляющую и составляющие с удвоенной частотой, Увеличение коэффициента умножения

К можно получить последовательным включением удвоителей частоты. При этом К равен К = 2 (m = 1, 2...).

Yll

Для того, чтобы разность фаз на входах пятого фазового детектора

13 к началу модуляции была равная нулю, фазовый, сдвиг сигнала на входе умножителя 12 частот при К = 2 должен быть равен ti/2К по отношению к началу модуляции. Тогда соотношение частоты генератора 10 опорной частоты Р и частоты модуляции Е будет равно F, = 4Kf, Таким образом, на периоде модуляции Т укладывается

4К импульсов генератора 10 опорной частоты, причем положение нулей сигнала на входе пятого фазового детектора !3 при отсутствии нелинейности фазовращат=ля 1 определяют четные номера импульсо» генератора 10 опорной частоты (фи,4а), поскольку число

1478?84 разрядный выход которого соединень:. соответствующими входами дешифратора,отличаlOщийс ягем, что, с целью повышения спектральной чистоты выходных сигналов, вве,цены последовательно соединенные четвертый фазовый детектор, первый вход которого соединен с выходом первого фазового детектора, второй фильтр нижних частот и второй параллельный сумматор, выход которого соединен с управляющим входом фазовращателя, последовательно соединенные умножитель частоты, вход которого соединен с выходом первого фазового детектора, пятый фазовый детектор и первый мультиплексор, а также второй и третий мультиплексоры, третий параллельный сумматор, N блоков интегрирования, где N — четное число, первый и второй инверторы и линия задержки, при этом к другому входу второго параллельного сумматора подключен выход управляемого аттенюатора, выход фазовращателя соединен с вторым входом первого фазового детектора и является выходом синтезатора частот, второй вход четвертого фазового детектора соединен с третьим выходом дешифратора, четвертый выход которого соединен с входом линии задержки, первый выход счетчика соединен с входом первого инвертора, выход которого соединен ! с входом разрешения первого мультиплексора, вход второго инвертора, вход разрешения третьего мультиплек5 сора и вход сигнала младшего разряда адресного кода первого мультиплексора объединены и подключены к второму выходу счетчика, выход второго инвертора соединен с входом разрешения второго мультиплексора, разрядный выход счетчика соединен с входом адресного кода первого, второго и третьего мультиплексоров, выход третьего параллельного сумматора соединен с входом интегратора со сбросом, вход сигнала сброса которого соединен с выходом линии задержки, выход генератора опорной частоты соединен с входом стробирования дешифратора и другим входом пятого фазового детектора, входы N блоков интегрирования соединены с соответствующими выходами первого мультиплексора, выходы 1,3,..., (N — 1)-го блоков интегрирования под25 ключены к соответствующим входам второго мультиплексора, выходы 2,4, (N-го) блоков интегрирования подключены к соответствующим входам третьего мультиплексора, выходы вто30 рого и третьего мультиплексоров соединены соответственно с первым и вторым входами третьего параллельного сумматора.

1478284

Составитель А.Мышакин

Техред Л.Сердюкова Корректор M.Ìàêñèìèøèíåö

Редактор А,Мотыль

Подписное

Тираж 885

Заказ 2370/52

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101