Цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано в устройствах цифровой обработки сигналов. Цель изобретения - упрощение цифрового фильтра за счет исключения умножителей и сумматоров. Цифровой фильтр содержит АЦП 1, блоки 2.1 - 2.ν определения вычетов входного сигнала, (M-1) -каскадные линии задержки 3.1, 3.2, 3.ν, вычислительные блоки (ВБ) 5, входы ВБ 5.1-5.4, выходы ВБ 5.5, 5.6, умножители 7, блок 8 восстановления результата и блок 9 управления. Для достижения цели в цифровой фильтр введены ν регистров 6 и ν групп по (M-1) ВБ в каждой. 6 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

1 д

rocvglrecmm A HoMerET

П0 ИЗОВИГТЕНИЯМ И ОТМЕЫТИяМ пРИ п<нт сссР

1 (21) 4252480/24-09 (22) 27.05.87 (46) 07.05.89. Бюл. Р 17 (71) Марийский политехнический институт им. А.М.Горького (72) Е.К.Лебедев (53) 68 1.325 (088.8) (56) Авторское свидетельство СССР

В 1246344, кл. Н 03 H 17/00, 1984. (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к радиотехнике и м.б. использовано в. устрвах цифровой обработки сигналов.

„„SU„„1478297 (51)4 H 03 Н 17/00 г

Цель изобретения — упрощение цифрового фильтра за счет исключения .умножителей и сумматоров. Цифровой фильтр содержит АЦП 1, блоки 2.1-2.g определения вычетов входного сигнала, (m-1)-каскадные линии задержки 3 ° 1, 3. 2, 3. 4, вычислительные блоки (ВБ)

5, входы ВБ 5.1-5.4, выходы ВБ 5.5, 5.6, умножители 7, блок 8 восстановления результата и блок 9 управления. Для достижения цели в цифровой фильтр введены 1 регистров 6 и 4 групп по (m-1) ВБ в каждой. 5 ил., 1 табл.

14782

Изобретение относится к радиотехнике и может быть использовано в устройствах цифровой обработки сигналов.

Цель изобретения — упрощение цифрового фильтра за счет исключения умножителей и сумматоров.

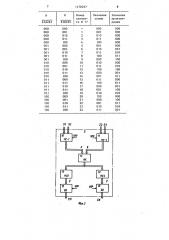

На фиг. 1 приведена структурная электрическая схема цифрового фильтра; на фиг. 2 — структурная электрическая схема вычислительного блока, на фиг. 3 — пример выполнения матриц ,конъюнкций и дизъюнкций вычислительного блока; на фиг. 4 - пример выполнения блока управления; на фиг. фиг. 5 — временные диаграммы, поясняющие работу цифрового фильтра.

Цифровой фильтр содержит аналогоцифровой преобразователь (АЦП) 1, . 2О блоки 2.1, 2.2,...,2. 4 определения вычетов входного сигнала, (ш-1)-каскадные линии 3 ° 1, 3.2, 3. задержки, группы вычислительных блоков 4.1

4.2,...,4,4, вычислительные блоки 5, 25 с первого по четвертый входы 5.1-5.4 вычислительных блоков, первый 5.5 и второй 5.6 выходы вычислительных блоков, регистры 6, умножители 7, блок 8 восстановления результата и 8р блок 9 управления °

Вычислительный блок (ВБ) 5 содержит первый 10 и второй 11 мультиплексоры, матрицу 12 конъюнкций, первую

13 и вторую 14 матрицы дизъюнкций и первый 15 и второй 16 буферные регистры.

Матрица 12 конъюнкций (МК) содержит элементы И 17.

Матрицы 13 и 14 дизъюнкций (МД) содержат элементы ИЛИ 18.

Блок 9 управления содержит генератор 19 тактовых импульсов и элементы

20 задержки.

Цифровой фильтр работает следующим образом

Сигналы () с выхода АЦП 1 поступают одновременно на ) блоков 2.1, 2.2,...,2. 4. Выходным сигналом блока

2.1 является последовательность выче- 50 тов х,(t) = (f(t)> гюс1 Nq, блока

2.2 — вычеты х <(t) = (g (t) 7 mod N< блока 2. 4 — вычеты х „(t)

< g(t) > mod N 1, Разрядность этих вычетов составляет соответственно

К flog х (, К1 )log х

К = 3 1о8 х . С выходов S-й (m-1)каскадной линии З.S задержки отсчеты

Вычетов х % х 5(t) х 25 х (С+У) ° ° .

x<,> = х (t + (m-1)T3 взвешиваются в соответствующих ВБ 5 с вычетами весовых коэффициентов А ° 5 = ас1 >

w mod М, j = 1,ш-1, S = 1, (отсчет х взвешивается в S-м умножителе

?.S с весом ° А ). .В ВБ 5 происходит и сложение взвешенных комбинаций.

С выхода 5.6 (m-1)-х ВБ 5 поканальные результаты в непозиционном коде подаются на блок 8, где они преобразуются в позиционный двоичный код.

Рассмотрим принцип работы вычислительного блока 5. Первый 10 и второй

11 мультиплексоры этого блока являются К -разрядными и имеют как прямой, так и инверсные выходы разрядов.

Выходы разрядов первого 10 и второго 11 мультиплексоров соединяются соответствующим образом с входами разрядов матрицы 12 конъюнкций.

Пример выполнения матриц конъюнкций 12 и дизъюнкций 13 и 14 при значении модуля N 5 = 5 приведен на фиг ° 3.

Если N 5 = 5, то R 5 3, т.е. первый и второй мультиплексоры являются трехразрядными и имеют следующие вкходы разрядов: А1, А?, АЗ, А1, А2, АЗ и Â1, В2, В3, В1, В2, ВЗ.

Эти разряды поступают на входы элементов И 17 согласно фиг ° 3, причем на первый элемент И 17 поступает кодовая комбинация А1А2АЗВ1В2ВЗ, на второй элемент И 17 — А1А2АЗВ1В2ВЗ на двадцать четвертый элемент

И 17 — А1А2АЗВ1В2ВЗ.

В матрице конъюнкций выделяются все логические комбинации, дающие

"1" в разрядах результата при реализации алгоритма .суммирования и умножения rio выбранному модулю системы остаточных классов (в данном .случае по модулю 5) .

Матрицы 13 и 14 дизъюнкций собирают комбинации, соответствующие

"1" в разрядах произведения и суммы соответственно. Ниже приведена таблица истинности для синтеза матриц конъюнкции 12 и дизъюнкции 13 и 14 для случая N = 5.

Из таблицы видно, что, если, например, число А на выходе первого мультиплексора 10 равно 4, а число

В на выходе второго мультиплексора равно 2, т.е. А1 = 1, А2 = О, A3 = О, B1 = О, В2 = 1, ВЗ = О, то откроется двадцать второй элемент И 17. Следовательно, на выходах произведения

5 14 по mod 5 (выход первой матрицы 13 дизъюнкций) "i" будет в первом и втором разрядах, а на выходах суммы (выход второй матрицы 14 дизъюнкций)

"1" будет только в первом разряде.

Следовательно, (А+В) mod 5 = (4+2) mod 5 = 1; (АВ) mod 5 (4 ° 2) mod 5 = 3, Временные диаграммы работы вычислительных блоков 5 в течение одного такта работы цифрового фильтра приведены на фиг. 5.

В момент t открываются второй и третий входы 5.2 и 5.3 ВБ 5 сигналом U s, поступающим на управляющие входы первого 10 и второго 11 мультиплексоров с выхода генератора 19 (фиг..4). На интервале от t до происходит формирование.в матрицах конъюнкции 12 и дизъюнкции 13 вычета произведения вычетов отсчета и весового коэффициента ° В момент времени

t < это произведение фиксируется управляющим сигналом U „ в первом буферном регистре 15.

Таким образом, при t = t< в первых буферных регистрах 15 всех ВБ 5, а также в регистрах 6 записаны произВедения 7613 уз23 ° . ° Ф Ys(m р Ysm (последнее получено в умножителях 7 и зафиксировано в регистрах 6) .

На интервале от t po t(„1 открыты первый и четвертый 5.1 и 5.4 входы ВБ 5. При этом происходит последовательное суммирование полученных вычетов произведений с фиксацией промежуточных результатов во вторых буферных регистрах 16 управляющими сигналами.

В момент времени t< ., результирующая сумма появляется на втором выходе 5.6 (m-1)-го ВБ 5 и поступает на вход блока 8.

Формула из обр ет ения

Цифровой фильтр, содержащий аналого-цифровой преобразователь, вход которого является входом цифрового фильтра, 11 блоков определения вычетов входного сигнала, где 4 >i 2, входы которых подключены к выходу аналого-цифрового преобразователя, 4(m-1)-каскадных линий задержки, где m — порядок цифрового фильтра, 4 умножителей, блок восстановления результата, выход которого является выходом цифрового фильтра, и блок

78297

6 управления, причем первый вход s Fo умножителя, где s - "1,2,..., соединен с выходом s-й (m-1)-каскадной линии задержки, вход которого подключен к выходу s-го .блока определения вычетов входного сигнала, а вторые входы умножителей являются входами вычетов m-го весового коэффициента, отличающийся тем, что; с целью упрощения цифрового фильтра за счет исключения умножителей и сумматоров, введены регист ров и групп по (m-1) вычислительных

15 блоков в каждой, управляющие входы которых соединены с соответствующими выходами блока управления, а в

s-й группе первьй вход первого вычислительного блока соединен со своим первым выходом, второй выход

j-го вычислительного блока, где

1,2,..., (m-1), является входом вычета j-го весового коэффициента, третий вход j — го вычислительного бло25 ка соединен с выходом s — ro блока определения вычетов входного сигнала и выходом (j-1)-го каскада s-й (j-1)-каскадной линии .задержки соответственно, четвертый вход и второй выход j-го вычислительного блока кроме (m-1)-ro соединены с первыми выходами и входом (j+1)-го вычислигельного блока соответственно, а выход s — го умножителя соединен через

s-й регистр с четвертым входом (m-i)ro вычислительного блока s-й группы, второй выход которого подключен к

s ìó входу блока восстановления результата, причем вычислительный блок

40 содержит первый и в горой мультиплексоры, матрицу конъюнкций, первую и вторую матрицы дизъюнкций и первый и второй буферные регистры, выходы которых являются первым и вторым выходами вычислительного блока соответственно, первым, вторым, третьим и четвертым входами которого являются первый и второй входы первого и второго мультиплексоров соответственно, выходы которых соединены с первым и

50 вторым входами матрицы конъюнкций соответственно, выход которой соединен с входами первого и второго буферного регистров через первую и

55 вторую матрицу дизъюнкций соответственно, а управляющие входы мультиплексоров и буферных регистров являются управляющими входами вычислительного блока.

А1А2АЗ

0О0

0Of

001

001

001

001

011

011

011

011

01,1

100

В1В2АЗ

001

0!0

011

001

011

001

011

011

011

l00

001

01 I

100

1478297

Номер элемента И 17

2

Э

5 б

8

11

12 .13

14

16

17

18

19

2.0

21

22

23

Значения

Сумм

001

011

001

011

011

001

011

001

001

011

ЯИ

Значения произведения

001

011

001

011

011

001

011

001

1478297

Фиг.5

1478297 ЯРС 4я O 8

° Ф

tm t 1

Т ираж 884

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35; Раушская наб., д. 4/5

Производственно- издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Редактор А.Мотыль

Заказ 3546 г

0е -с(/аб д 2 3 .

Фис.J

Составитель С.Музычук

Техред JI,Ñåðäþêîâà Корректор С.Шекмар -.