Многочастотный цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано для полосовой фильтрации сигналов на M из N частот (M*98N). Цель изобретения - повышение точности фильтрации. Фильтр содержит АЦП 1, блок 2 синхронизации, блок 8 многоканальной фильтрации, блок 9 памяти коэффициентов, коммутатор 10. Для достижения цели введены блок 3 округления отсчетов, блок 4 преобразования частоты отсчетов, блок 5 многоканальной фильтрации, блок 6 памяти коэффициентов и блок 7 выделения максимального сигнала. В предлагаемом устройстве производится предварительная оценка спектральной структуры входного сигнала, причем блоки, формирующие указанную оценку, работают с пониженной частотой дискретизации и уменьшенной разрядностью отсчетов сигналов и весовых коэффициентов. После этого на основании полученной оценки выбираются M из N частот, подлежащих выделению фильтром, работающим с повышенной частотой дискретизации, разрядностью отсчетов сигналов и весовых коэффициентов. 6 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 11 03 Н 17/04

C--" Оюр г

Ev n@.. 1.. 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4302653/24-09 (22) 08.09 ° 87 (46) 07.05.89. Вюл. М- 17 (72) Ю.О.Охлобыстин (53) 621.372.544(088.8) (56) Цикин И.А. Дискретно-аналоговая обработка сигналов. — M. Радио и связь, 1982, с. 81. (54) МНОГОЧАСТОТНЫЙ ЦИФРОВОЙ ФЮ1ЬТР (57) Изобретение относится к радиотехнике и м.б. использовано для полосовой фильтрации сигналов на m из N частот (тпЕМ). Цель изобретения — повышение точности фильтрации. Фильтр содержит АЦП 1, блок 2 синхронизации, .блок 8 многоканальной фильтрации, блок 9 памяти коэффициентов, коммутатор 10. Для достижения цели введены

„„SU„„1478299 А1 блок 3 округления отсчетов блок 4 преобразования частоты отсчетов, блок

5 многоканальной фильтрации, блок 6 памяти коэффициентов и блок 7 выделения максимального сигнала. В предлагаемом устройстве производится предварительная оценка спектральной структуры входного сигнала, причем блоки, формирующие указанную оценку, работают с пониженной частотой дис" кретизации и уменьшенной разрядностью отсчетов сигналов и весовых коэффициентов. После этого на основании полученной оценки выбираются m из N частот, подлежащих выделению фильтром, работающим с повышенной частотой дискретизации, разрядностью отсчетов сигналов и весовых коэффициентов. 6 ил.

1 147829

Изобретение относится к радиотехнике и может быть использовано для полосовой фильтрации, сигналов íà m иэ N частот (m

Цель изобретения — повышение точности фильтрации.

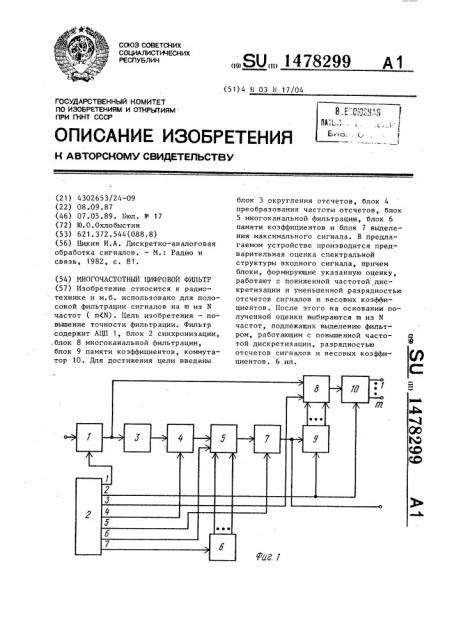

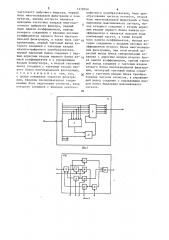

На фиг.. 1 представлена электрическая структурная схема многочастотного фильтра; на фиг. 2 — схема блока округления отсчетов; на фиг. 3 — схе- 1О ма блока многоканальной фильтрации; на фиг. 4 — схема блока выделения максимального сигнала; на фиг. 5 схема блока преобразования частоты отсчетов; на фиг. 6 — схема блока 15 синхронизации.

Многочастотный цифровой фильтр (фиг. 1) содержит аналого-цифровой преобразователь (АЦП) 1, блок 2 синхронизации, блок 3 округления отсче- 20 тов блок 4 преобразования частоты отсчетов, второй блок 5 многоканальной фильтрации, второй блок 6 памяти коэффициентов, блок 7 выделения максимального сигнала, первый блок 8 мно- 5 гоканальной фильтрации, первый блок 9 памяти коэффициентов, коммутатор 10 °

Блок 3 округления отсчетов (фиг.2) содержит элемент И-НЕ 11, сумматор 12, элемент И 13. 30

Первый и второй блоки 8 и 5 многоканальной фильтрации (фиг. 3) содержат сумматор 14, элемент 15 задержки, умножители 16 и 17, элемент 18 задержки, умножители 19 — 21, сумматор 22 °

Блок 7 выделения максимального сигнала (фиг. 4) содержит коммутатор 23, формирователи 24-1, 24-2, 24-3 модуля сигнала, регистры 25-1, 25-2, 25-3 40 сдвига, взвешивающие сумматоры 26-1, 26-2, 26-3, компараторы 27-1, 27-2, 27-3.

Блок 4 преобразования частоты отсчетов (фиг. 5) сожержит блок 28 сов- 45 падения, элемент 29 задержки, блок 30 памяти.

Блок 2 синхронизации (фиг. 6) содержит генератор 31 тактовых импульсов, делитель 32 частоты импульсов, 5ц счетчик 33 импульсов, делители 34 и

35 частоты импульсов, счетчик 36 импульсов, делитель 37 импульсов.

Многочастотный цифровой фильтр работает следующим образом.

Выходной сигнал АЦП 1, представляющий собой последовательность отсчетов исследуемого аналогового сигнала в цифровой форме и следующих с

9 2 периодом дискретизации Т, поступает в блок 3 округления отсчетов, понижающий разрядность двоичных чисел, представляющих отсчеты. Если эти числа поступают в параллельном коде, то округление может быть выполнено просто отбрасыванием нескольких младших разрядов. Более точно округление может быть выполнено при использовании блока 3 округления (фиг. 2) . Если число, образованное отбрасываемыми разрядами, больше половины младшего оставляемого разряда (например, как на фиг. 2, если старший отбрасываемый разряд этого числа равен 1), то к числу, образованному оставляемыми разрядами, добавляется единица, поступающая на сумматор 12 с выхода элемента И 13. Элемент И-НЕ 11 защищает сумматор 12 от переполнения.

Последовательность отсчетов, представленных двоичными числами пониженной разрядности, с выхода блока 3 поступает на вход блока 4, осуществляющего понижение частоты следования отсчетов в случае, если F*/F --2п, где и (целое)) 1, à F > — высшая частота спектра исследуемого аналогового сигнала. При этом на блок 4 от блока 2 синхронизации подается частота У2,>

Обновление информации в блоке 30 памяти на D-триггерах происходит только по передним фронтам сигнала Ед/2, т .е. частота следования отсчетов на выходе блока 4 уменьшена вдвое по сравнению с частотой Гд. Аналогично можно понизить частоту дискретизации, например, в 4 раза и т.д. Элемент 29 задержки обеспечивает небольшую задержку момента стробирования информации в блок 30 памяти для того, чтобы код текущего отсчета гарантированно успел пройти через блок 28 совпадения.

Сигнал с уменьшенной разрядностью чисел и пониженной частотой дискретизации подается в Х-канальный блок 5.

Тактовая частота второго блока 5 многоканальной фильтрации в Х раз выше частоты дискретизации сигнала на выходе блока 2 ° Второй блок 5 обеспечивает. предварительную фильтрацию сигнала в N частотных каналах (на N частотах) и выдачу результатов в ви3 147829 де уплотненных по времени N последовательностей отсчетов, являющихся результатами фильтрации выходного сигнала блока 4 на М различных частотах

5 на вход блока 7 выделения максимального сигнала.

Блок 7 выбирает m максимальных сигналов из N и определяет, в каких

m из N частотных каналов блока 5 сиг- 1ð налы максимальны, а следовательно, точное выделение каких именно частотных составляющих должно быть произведено первым блоком 8. Для этого блок

7 формирует сигнал для первого бло- 15 ка 9 памяти коэффициентов, который в совокупности с сигналом, поданным на первый блок 9 памяти от второго выхода блока 2 синхронизации образует совокупный адресный сигнал, определяющий считывание из блока 9 памяти коэффициентов, соответствующих передаточным функциям в выбранных m частотных каналах первого блока 8.

Для сравнения уровней выходных 25 сигналов различных частотных каналов второго блока 5 в блоке 7 могут быть сформированы для каждого k-го частотного канала оценки среднего значения (t; „, t ) сигнала этого канала на ин- go тервале в соответствии со следующим равенством. из трех сигналов являются 11,(;), U,(t,.); U,(r..), U,(t.,); U,(t;), U(t;), соответствует определенный двоичный код на выходе блока 7, который определяет считывание из тех зон первого блока 9 памяти коэффициентов, в которых хранятся значения весовых коэффициентов, определяющие передаточные функции в m выбранных частотных каналах, сигналы в которых на выходе. второго блока 5 оказались максимальными.

Выход блока 7 образует выход кода комбинации частот, на который поступает двоичный код, определяющий какие именно m из N частот выделяются первым блоком 8. Первый блок 8 многоканальной фильтрации обеспечивает полосовую фильтрацию на m выбранных частотах из N и построен аналогично структуре, приведенной на фиг..3. Выделение результатов фильтрации в каждом отдельном канале из m производится выходным коммутатором 10. Разрядность отсчетов, весовых коэффициентов и частота дискретизации в первом блоке 8 выше, чем во втором блоке 5, что обеспечивает высокую точность фильтрации на ш выбранных частотах.

Все необходимые для работы сигналы формируются блоком 2 синхронизации, один из возможных вариантов которого приведен на фиг. 6. Генератор 31 формирует частоту NF которая с помощью делителей 32, 37 и 35 делится соот ветственно на 2, на N è íà N/m, чем формируются тактовая частота для

АЦП 1, тактовая частота NF 2>

2 раза.

55

U (t;)=-,>(U„(t1,. )1, 1

j-o

35 где И „(t;) — среднее значение выход- . ного сигнала k — ro частотного канала второго блока 5 на интервале (t; „ значения отсчетов сигнала k-го час- 4р тотного канала в моменты времени t; >

Для повышения точности оценки по равенству (1) интервал суммирования должен охватывать, как правило, несколько полупериодов частоты k-го ка- 45 нала (Кя 1).

Компараторы 27-1 — 27-3 позволяют достаточно просто выполнить попарное сравнение величин U <(t ) для всех N каналов и выбрать m частотных каналов, сигналы в которых максимальны.

Для этого коммутатор 23 обеспечивает выделение потоков отсчетов, соответствующих каждому частотному каналу второго блока 5. Формирователи

24-1 — 24-3, вычисляющие абсолютные значения отсчетов, могут просто производить отбрасывание знаковых разря9

4 дов входных чисел, а регистры 25-1

25-3 сдвига совместно с сумматорами

26-1 — 26-3 формируют оценки средних значений U3,(t,) сигналов в соответствии с (1), которые затем попарно сравниваются в компараторах 27-1 — 27-3.

Каждому случаю, когда максимальными

Формула изобретения

Многочастотный цифровой фильтр, содержащий последовате.п иа соединенные аналого-цифровой преобразователь, вход которого является входом много5 14782 частотного цифрового фильтра, первый блок многоканальной фильтрации и коммутатор, выходы которого являются выходами частотных каналов многочастотного цифрового фильтра, первый

5 блок памяти коэффициентов, выходы которого соединены с входами весовых коэффициентов первого блока многоканальной фильтрации, а также блок син- 0 хронизации, первый тактовый выход которого соединен с тактовым входом аналого-цифрового преобразователя,. первый адресный выход соединен с первым адресным входом первого блока па- g мяти коэффициентов и с управляющим входом коммутатора, а второй тактовый выход соединен с тактовым входом первого блока многоканальной фильтрации, отличающийся тем, что, с целью повышения точности фильтрации, введены последовательно соединенные блок округления отсчетов, вход которого соединен с выходом аналого-

99 б цифрового преобразователя, блок преобразования частоты отсчетов, второй блок многоканальной фильтрации и блок выделения максимального сигнала, выход которого соединен с вторым адресным входом первого блока памяти коэффициентов и является выходом кода комбинации частот, а также второй блок памяти коэффициентов, выходы которых соединены с входами весовых коэффициентов второго блока многоканальНоН фильтрации, при этом второй адресный выход блока синхронизации соединен с адресным входом второго блока памяти коэффициентов, третий тактовый выход соединен с тактовым входом второго блока многоканальной фильтрации, четвертый тактовый выход соединен с тактовым входом блока преобразования частоты отсчетов, а управляющий выход соединен с управляющим входом блока выделения максимального сигнала.

Фиг.2

1478299

1478299 фее. б

Составитель Э.Борисов

Редактор А.Мотыль Техред А.Кравчук Корректор Э.Лончакова

Заказ 2371/53 Тираж 885 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101