Устройство адаптивного приема многопозиционных дискретных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к области электросвязи. Цель изобретения - повышение помехоустойчивости. Для достижения цели в устройство, содержащее коммутатор 1 и адаптивный трансверсальный фильтр 2, введены решающий блок 3, блок 4 регистров, мультиплексор 5, блок 6 подстройки коэффициентов, блок 7 сравнения сигналов, блок 8 управления и вычислительные блоки 9<SB POS="POST">1</SB>-9<SB POS="POST">N</SB>. В устройстве реализована модифицированная рекурентная процедура поэлементного вынесения решения о переданной последовательности элементов сигнала, основанная на правиле максимального правдоподобия, чем и достигается поставленная цель. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

gg4 Н 04 В 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4134963/24-09 (22) 17.10.86 (46) 07.05.89, Бил, № 17 (72) A.Ë. Маримонт, С.С. Разживин и Й.В. Ткаченко (53) 621.394.62(088.8) (56) Nonsen Р. Feedback Equalization

for Forling Dispersiol Channel, ОЕЕЕ

Transactions on Information theory, vol. 17, № 1, 1971, р. 61 (прототип). ! (54) УСТРОЙСТВО АДАПТИВНОГО ПРИЕМА

МНОГОПОЗИ! ИОННЫХ ДИСКРЕТНЫХ СИГНАЛОВ (57) Изобретение относится к области электросвязи. Цель изобретения — поÄÄSUÄÄ 1478342 А1 вышение помехоустойчивости. Для достижения цели в устр-во, содержащее коммутатор 1 и адаптивный трансверсальный фильтр 2, введены решающий блок 3, блок 4 регистров, мультиплексор 5, блок 6 подстройки коэффициентов, блок 7 сравнения сигналов, блок

8 управления и вычислительные блоки

9,-9 . В устр-ве реализована модифицированная рекурентная процедура поэлементного вынесения решения о переданной последовательности элементов сигнала, основанная на правиле максимального правдоподобия, чем и достигается поставленная цель. 5 ил .

1478342 гдето =

Z )с ром

Изобретение относится к электрос вя зи и может использоваться в системах передачи данных по каналам с межсимвольной интерференцией.

Цель изобретения — повьннение помехоустойчивости.

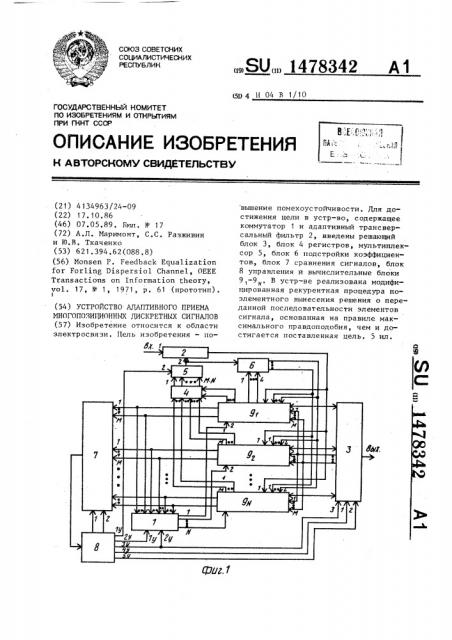

На фиг. 1 изображена структурная электрическая схема устройства адаптивного приема многопозиционных дискретных сигналов; на фиг. 2-5 — решающий блок, вычислительный блок, блок сравнения сигналов и блок управления соответственно.

Устройство адаптивного приема мно- 15 гопозиционных дискретных сигналов со держит коммутатор 1, адаптивный трансверсальный фильтр 2, а также решающий блок 3, блок 4 регистров, мультиплексор 5, блок 6 подстройки 20 коэффициентов, блок 7 сравнения сигналов, блок 8 управления и вычислительные блоки 9„-9„ .

Решающий блок 3 (фиг. 2) содержит первый коммутатор 10, регистры 11, — 25

11„ сдвига, источники 12,-12 эталонных элементов сигнала и второй коммутатор 13..

Вычислительный блок 9 (фиг. 3) содержит линию 14 задержки, умножители gp

15„-15, первый сумматор 16, блоки

17„-17... вычитания, квадраторы 18,—

i8» вторые сумматоры 19 „-19 и согласующие блоки 20„-?О

Блок 7 сравнения сигналов (фиг. 4)

35 с одержит цифр овые компара торы 21 „21 д и мультиплексор 22, Блок 8 управления (фиг. 5) содержит счетчик 23 по модулю M N тактовый генератор 24, счетчик 25 по 40 модулю N, делитель 26 на М x N, двоичный 1 разрядный счетчик 27, регистр 28 сдвига и дешифратор 29.

Устройство работает следующим образом. 45

Для достижения поставленной цели в предлагаемом устройстве реализована м одифицир овани а я р екурр ентная процедура поэлементного вынесения решения о переданной последователь50 ности элементов сигнала, основанная на правиле максимального правдоподобия. В общем случае, оценка последовательности по этому правилу базируется на представлении системы пере †дачи в виде системы с конечным числом состояний. Каждое состояние на k-м шаге обработки характеризуется векто2

6„= (a„, с1,, ..., d <), (1) я где д„, л с1 эталонные значения элементов передаваемого сигнала, взятого иэ алфавита объемом М; — число ненулевых отсчетов импульсной характеристики тракта передачи.

Общее число состояний системы равно M . Переход системы из состояния

Ь, в состояние б„ характеризуется целевой функцией т„(ь„) = т „,(ь,,) + f („Р„), (2) где Р— вектор управления, задающий оптимальную стратегию поиска.

Последовательность переходов системы из состояния в состояние образует граф с числом путей М, причем метрика каждого из них определя" ется выражением (2). Выбор продолжений для каждого пути осуществляется на основе минимизации целевой функции (2). Переданная последовательность элементов сигнала определяется последовательностью состояний вектора (1), через которые проходит путь в графе с минимальной метрикой, Реализованная в устройстве модификация описанной процедуры заключается в том, что на каждом шаге л ь обработки отслеживается только N (c M наиболее вероятных путей с наименьшими метриками, что значительно упрощает процедуру вынесения решений при сохранении высокой помехоустойчивости. В качестве целевой функции выбрана метрика пути,. характеризуемая выражением

1 р; 1 „,. ) + т „",, (3)

l=o

1, 2, . ° ., N.; отсчет сигнала на выходе адаптивного трансверсального фильтра 2 на k-ом шаге обра.ботки; коэффициенты, задающие импульсную характеристику сквозного тракта передачи в отсчетные моменты времени

idT учитывающие канал и адаптивный трансверсальный фильтр 2, (= 1;

1478342 (ю оК- ° ° °

25 л (г

Ci

30 к-L

° ° ° гдеш=1, 2, 1=1, 2, ° ° ° и у м;

dT — длительность элемента сигна— предварительные решения, характеризующие состояние (1), в котором закончился гп-й путь.

Вычислительные блоки 9 обеспечивают хранение предварительньгх решений, соответствующих отслеживаемому пути, вычисление сигналов ошибки, их выдачу в блок 4 регистров,, а также вычисление метрик M возможных продолжений пути и их выдачу на соответствующую группу информационных входов блока 7 сравнения сигналов. Последний совместно с блоком 8 управления осуществляет сравнение и выбор N наименьших метрик. Блок 8 управления по результатам сравнения осуществляет выдачу управляющих сигналов, В соответствии с управляющими сигналами производится: выдача текущего решения и сортировка предварительных решений в решающем блоке 3 с последующей записью предварительных решений в N вычислительных блоков 9 в порядке возрастания метрик: с помощью коммутатора 1 — выбор соответствующих отсортированным предварительным решениям метрик и их запись в N вычислительных блоков 9; выдача сигнала ошибки из блока регистров 4 с помощью мультиплексора 5. 35

Сигнал ошибки с выхода мультиплексора 5 используется. для подстройки коэффициентов в адаптивном трансверсальном фильтре 2, а также поступает на вход блока 6 подстройки коэф- 40 фициентов, который осуществляет адаптивную подстройку коэффициентов, соответствующих ртсчетам импульсной характеристики сквозного тракта передачи. 45

Ha k-м шаге обработки в момент времени С к = kQT, где dT — длительность элемента сигнала, отсчет принимаемого сигнала поступает на сиг:нальный вход адаптивного трансвер- 50 сального фильтра 2. С выхода адаптивного трансверсального фильтра 2 .частично откорректированный сигнал ггоступает на первые одиночные входы вычислительных блоков 9,-9,„, каждый из которых обеспечивает хранение предварительных решений, вынесенных за предыдущие п шагов обработки в виде и-мерного вектора

Д (< м- 1 к- ° ° ° э м ) ý(4) гдегп=1, 2,..., N; л гп — предварительное решение, хра нящееся в m-м вычислительном блоке 9„, вынесенное на (К-и)-ом шаге обработки;

n — величина задержки, выбираемая из условия и ъ L + 1.

В вычислительных блоках 9."9 произ:1 Й водится дальнейшая компенсация искажений частично откорректированного сигнала с выхода адаптивного транс- . версального фильтра 2 путем вычитаний из него предсказанных значений мешающих воздействий в соответствии с выражением

3"к(гп) Z 2 к = Z„ Р;г1 к (5) г-"1 где m = i, 2, ..., N; и

7.„- предсказанное значение мешающего воздействия; коэффициенты, характеризующие импульсную характеристику сквозного тракта передачи канал — адаптивный трансверсальный фильтр 2; — предварительные решения, являющиеся элементами m-ro вектора (4) .

С первых выходов решающего блока 3 на вторые групповые входы вычислительных блоков 9„-9 гпоступает M эталонных значений сигнала, которые используются для вычисления сигналов ошибки в соответствии с выражением

e„(m, 1) = g„(m) — dI,(e), (6) где гп = 1, 2,..., N; .1 = 1, 2,..., М); л

cl „, ° ° °

1л (e>

cl — эталонные значения элементов сигнала. М сигналов ошибки (6) с вторых групповых выходов каждого вьгчислительного блока 9 поступают на соответствующие входы блока 4 регистров.

В соответствии с выражением (3) в каждом из N вычислительных блоков

9 производится вьгчисление М метрик с использованием сигналов ошибки (6) по правилу

Т к(гп 1) = е к (ш, 1) + Т „, (гп), (7) пути и полученная на предыдущем шаге обработки.

Обработка сигналов в решающем блоке 3 (фиг . 2) производится по управляющим сигналам на его первом, втором и третьем входах. С началом текущего шага обработки векторы предварительных решений (4), хранимые в вычислительных блоках 9, через входы-выходы и.первый коммутатор 10 переписыйаются в соответствующие регистры 11 сдвига, При этом управляющие

10 сигналы (нулевые коды) на третьем и втором входах решающего блока 3 обеспечивают проключение входов на выходы первого коммутатора 10. Далее производится сдвиг информации в регистрах 11 -11 сдвига на один эле1 „N мент "вправо". При этом освобождаются первые ячейки регистров для записи в них текущих решений dg, а решения, хранимые в последних ячейках всех регистров 11 сдвига, кроме первого, теряются. На выход решающего блока 3 поступает задержанное на и шагов обработки решение, соответствующее наименьшей метрике предыдущего шага. При записи текущих решений в первые ячейки регистров 11 сдвига выбор источника 12 эталонного элемента сигнала, подключенного к соот15

30 ветствующему входу второго коммутатора 13, осуществляется с помощью управляющего сигнала на первом входе решающего блока 3. Выбор выхода второго коммутатора 13, подключенного к соответствующему регистру 11 сдви35 га, осуществляется с помощью управляющего сигнала на втором входе реша- 40 ющего блока 3. Перепись предварительных решений в обратном порядке из регистров 11 сдвига в N вычислительных блоков с одновременной их сортировкой в порядке возрастания метрик осуществляется с помощью первого коммутатора 10, по мере поступления управляющих сигналов на входы решающего блока 3. При этом первый коммутатор 10 по управляющему сигналу на втором входе решающего блока 3

50 проключает выход регистра 11 сдвига, соответствующего текущей .найценной метрике, на вход очередного вычислительного блока 9 по управляющему сиг- 55 калу на третьем входе решающего блока, В результате, в конце каждого акта обработки И вычислительных блоков 9 содержат предварительные реше5 147834

T (m) — метрика, соответствующая m-му

2 6 ния и соответствующие им метрики, отсортированные в порядке возрастания, В первом вычислительном блоке 9 (фиг, 3) сигналы, поступающие через вход — выход блока, задерживаются в линии 14 задержки и с ее отводов поступают на входы умножителей 15 и образуют также третью группу выходов блока, соединенных с вторыми входами блока 6 подстройки коэффициентов. Эта группа выходов отсутствует в других вычислительных блоках,9. Работа вычислительных блоков

9, -9 л,происходит в соответствии с выражением (7) .

На вторые входы умножителей 15 поступают сигналы с выходов блока 6 подстройки коэффициентов. Сигналы с выходов умножителей 15 после суммирования в первом сумматоре 16 поступают на блок 17 вычитания, другой вход которого является первым одиночным входом вычислительного блока

9. Сигнал с выхода блока вычитания поступает на общий вход других блоков 17 -17, „ вычитания, на индивидуальные входы которых поступают сигналы с первых выходов решающего блока 3. Результаты вычитания после обработки в квадраторах

18 поступают в вторые сумматоры 19, вторые входы которых через соответству щ и согласу щ и блок 20 ч„ соединены с вторым одиночным входом вычислительного блока 9.

Вычисленные метрики поступают через согласующие блоки 20,-20 на соответствующие групповые входы коммутатора 1 и блока 7 сравнения сигналов, которые совместно с блоком 8 управления осуществляют сравнение

N М вычисленных в блоках 9 метрик и выбирают из них N наименьших, Происходит это следующим образом. На индивидуальные входы цифровых компараторов 21 блока 7 сравнения сигналов (фиг. 4) подаются сигналы с вычислительных блоков 9„-9 „, а на общий вход — ступенчато нарастающий цифровой код (начиная с нулевого состояния), поступающий из блока 8 управления. На каждой ступеньке мультиплексор 22 опрашивает выходы всех цифровых компараторов 21 и, если хотя бы на одном из них входные сиг налы совпадут, то на выходе мультиплексора 22 или, что то же, на выходе блока 7 сравнения сигналов поя1 7834 ) вится импульс, поступающий на вход блока 8 управления. Этот импульс (фиг. 5) поступает на вход тактового генератора 24 и счетчик 25 по модулю N, подсчитывающий количество отоб5 раженных метрик. При выборе N наи1 меньших метрик он вырабатывает на верхнем по схеме выходе импульс, воздействующий на тактовый генератор 24, 1О который, в свою очередь, вырабатывает импульс сброса на счетчик 23 по модулю M к N и на двоичный 1-разрядный счетчик 27 °

Тактовые импульсы с другого выхода генератора 24 поступают на тактовый вход счетчика 23 по модулю M N и через делитель 26 на M N, на тактовый вход двоичного 1-разрядного счет-чика 27, образуя на выходах упомяну- 20 тых счетчиков цифровые коды, поступающие на блок 7 сравнения сигналов.

При этом за счет делителя 26 на

М N одно изменение кода на выходе . двоичного 1-разрядного счетчика 27 (что соответствует одной ступеньке в блоке 7 сравнения сигналов) вызывает изменение цифрового кода на выходе счетчика 23 по модулю MхИ от

О до Е N . Этот код управляет мультиплексором 22 (фиг. 4), опрашивающем выходы цифровых компараторов 21 и одновременно поступает на вход дешифратора 29 (фиг. 5), где он определяет один из M N информационных входов блока 7 сравнения сигналов.

При поступлении импульса на вход тактового генератора 24, последний задерживает выдачу тактовых импульсов и вырабатывает импульс разрешения на дешифратор 29, который по цифровому коду на выходах счетчика 23 по модулю М N вырабатывает пять управляющих сигналов. При этом код на первый выход блока 8 управления проходит через регистр 28 сдвига, не изменяемый до следующей первой выбранной метрики. Этот код определяет номер входа из М > N входов блока 7 сравнения сигналов с первой найденной.метрикой и поступает также на 50 мультиплексор 5, осуществляющий выбор соответствующего выхода блока регистров 4, содержащего сигналы ошибки. Благодаря этому обеспечивается выдача сигнала ошибки е„, соответст- 55 вующей наименьшей из метрик.

Код на втором выходе блока 8 управления определяет номер одного из

М < N входов коммутатора 1 с текущей найденной метрикой из множе<.тва N наименьших метрик.

Код на третьем выходе блока 8 управления определяет очередной номер найденной метрики из N, с помощью которого выбирается один из N выходов коммутатора 1 для подачи в соответствующий из вычислительных блоков

9 -9 метрики пути или последующего шага обработки по выражению (7) . На каждом шаге обработки передается

N метрик путей в соответствующие вычислительные блоки 9 в порядке их возражения.

Код на четвертом выходе блока 8 управления определяет номер эталони ного элемента сигнала d „в группе входов с метрикой, соответствующей второму выходу этого блока.

Код на пятом выходе блока 8 управления указывает на группу информационных входов блока 7 сравнения сигналов для отобранной метрики.

Сигнал ошибки с выхода мультиплексора 5 поступает на управляющий вход апаптивного трансверсального фильтра 2 и на вход блока подстройки коэффициентов. Подстройка коэффициентов адаптивного трансверсального фильтра 2 выполняется аналогично известному, Подстройка коэффициентов для вычислительных блоков 9 осуществляется в соответствии с выражением

I где p, „ — коэффициент, соответствуI ющий i-му отсчету импульсной характеристики сквозного тракта передачи; е — сигнал ошибки на k-м шаге обработки; л, d, — предварительное решение, задержанное на (k-i) шагов обработки, содержащееся в первом вычислительном блоке 9„ р — шаг подстройки.

Подстройка коэффициентов в соответствии с выражением (8) осуществляется в блоке 6 подстройки коэффициентов. При этом на группу из L входов блока 6 подстройки коэффициентов поступают и еднарительные решения

d,;, ..., d „ с. третьей группы (1i (ii выходов первого вычислительного блока 9,, так как в этом блоке хранятся решения, соîTBåòeTâ÷îùèå наименьшей

1478342

Моделирование на ЭВМ показало, что использование предлагаемого устройства, даже при небольшом числе вычислительных блоков (3-8), позволяет уменьшить более чем на порядок вероятность ошибки по отношению к известному при одном и том же отношении. сигнал/шум.

30

Формула изобретения

Устройство адаптивного приема многопозиционных дискретных сигналов, содержащее коммутатор и адаптивный трансверсальный фильтр, сигнальный вход которого является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчиврсти, введены решающий блок, блок регистров, мультиплексор, блок подстройки коэффициентов, блок сравнения сигналов, блок управления и N метрике. Подстроенные коэффициенты

Р с группы ? выходов блока подстройки 9 поступают на первые групповые входы N вычислительных блоков 9.

В соответствии с управляющими сигналами на 2-м — 5-м выходах блока 8 управления осуществляется сортировка предварительных решений в решающем блоке 3, а также с помощью коммутатора 1 соответствующих им метрик.

При этом номер входа коммутатора 1 с очередной наименьшей .метрикой задается управляющим сигналом на первом входе, а номер выхода - управляющим сигналом на втором входе коммутатора 1. В результате в конце текущего шага обработки в 1, 2,...

N-м вычислительных блоках 9 метрики 20 располагаются в порядке их возрастания. вычислительных блоков, первые групповые входы которых соединены с выходами блока подстройки коэффициентов, первый вход которого подключен к выходу мультиплексора и управляющему входу адаптивного трансверсального фильтра, выход которого соединен с первыми одиночными входами вычислительных блоков, вторые одиночные вхо" ды которых подключены к соответствующим выходам коммутатора, N групповых входов которого и И групповых входов блока сравнения сигналов соединены с первыми групповыми выходами соответствующих вычислительных блоков, вторые групповые выходы которых соединены с соответствующими входами блока регистров, выходы которого подключены к первым входам мультиплексора, второй вход которого соединен с первым выходом блока управления, вход, второй и третий выходы которого подключены соответственно к выходу блока сравнения сигналов и первому и второму одиночным входам коммутатора, причем вторые групповые входы вычислительных блоков соединены с первыми выходами решающего блока, четвертый, пятый, шестой и седьмой выходы блока управления соединены соответственно с первым и вторым входами решающего блока и первым и вторым одиночными входами блока сравнения сигналов, а N входов-выходов решающего блока подключены к входамвыходам соответствующих вычислительных блоков, при этом вторые входы блока подстройки коэффициентов соеди иены с третьим групповым выходом соответствующего вычислительного блока, третий выход блока управления подключен к третьему входу решающего блока, второй выход которого является выходом устройства.

1ч 783ч2

14 78342

Составитель В. Зенкин

Редактор П, Лазаренко . Техред Л.Сердюкова Корректор Н. Король

Заказ 2374/55 Тираж 627. Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035., Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101