Устройство защиты от ошибок

Иллюстрации

Показать всеРеферат

Изобретение касается передачи дискретной информации и относится к устройствам защиты от ошибок с решающей обратной связью. Цель изобретения - повышение скорости передачи информации. Устройство содержит входной накопитель 1, блок 2 элементов ИЛИ, анализатор 3 служебной команды, кодер 4, буферный накопитель 5, ключ 6, датчик 7 служебных команд, блок 8 управления, задающий г-р 9, датчик 10 запросной комбинации, блокиратор 11, дешифратор 12 запросной комбинации, декодирующий блок 13, анализатор 14 служебных команд, приемный накопитель 15. В устройство введены делитель 16 цикловой частоты, счетчик 17 числа фазирований, ключ 18 и блок 19 задержки. Введение новых элементов позволяет сократить кол-во обменов служебными командами при частых фазированиях, за счет чего повышается скорость передачи информации. 5 ил.

А2

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИ4ЕСНИХ

РЕСПУБЛИК ц11, Н 04 Ь 1/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРБ1ТИЯМ

ПРИ ГКНТ СССР (61 ) 1197115 (21) 4221403/24 — 09 (22) 06,04.87 (4Ь) 07.05.89. Бюл. М 17 (72) В.И.Самофалов, И.Е.Гришин, А.В,Ермоленко и 1О,П.Иванов (53) 621.394.14 (088,8) (56) Шляпоберский B.È. Основы техники передачи дискретных сообщений, M. Связь, 1973, с.398, рис.7.10.

Авторское свидетельство СССР

Р 1197115, кл. Н 04 Ь 1/16, 1984. (54) УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК (57) Изобретение касается передачи дискретной информации и относится к устр-вам защиты от ошибок с решающей обратной связью. Цель изобретения — повышение скорости передачи

ÄÄSUÄÄ 1478362 информации. Устр-во содержит входной накопитель 1, блок 2 элементов ИЛИ, анализатор 3 служебной команды, кодер 4, буферный накопитель 5, ключ

6, датчик 7 служебных команд, блок

8 управления, задающий г-р 9, датчик 10 запросной комбинации, блокиратор 11, дешифратор 12 запросной комбинации, декодирующий блок 13, анализатор 14 служебных команд, приемный накопитель 15. В устр-во введены делитель 16 цикловой частоты, счетчик 17 числа фазирований, ключ

18 и блок 1-9 задержки. Введение новых элементов позволяет сократить кол-во обменов служебными командами при частых фаэированиях, за счет чего повышается скорость передачи информации. 6 ил.

1478362

Изобретение относится к области передачи дискретной информации, в частности к устройствам защиты от ошибок с решающей обратной связью и является усовершенствованием устройства по основному авт.св.

Ф 1197115.

Цель изобретения — повьппение скорости передачи информации.

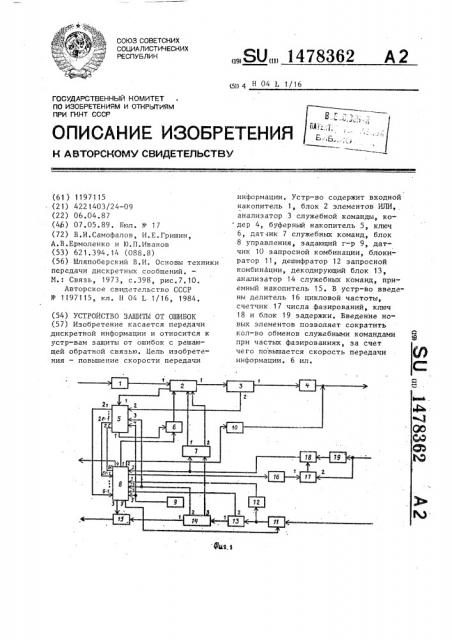

На фиг.1 представлена структурная электрическая схема предложенного устройства; на фиг.2 — схема блока элементов ИЛИ; на фиг.3 — схема анализатора служебной команды.; на 15 фиг.4 — схема анализатора служебных команд; на фиг.5 — функциональная схема буферного накопителя; на фиг.6 — схема блока управления.

Ус гройство защиты от ошибок со- 20 держит входной накопитель 1, блок 2 элементов ИЛИ, анализатор 3 служебной команды, кодер 4 буферный на1 копитель 5, ключ 6, датчик 7 служебных команд, блок 8 управления, задаю- 25 щий генератор 9, датчик 10 запросной комбинации, блокиратор 11, дешифратор

12 запросной комбинации, декодирующий блок 13, анализатор 14 служебных команд, приемный накопитель 15, дели- 30 тель 16 цикловой частоты, счетчик 17 числа фазирований, ключ 18 и блок 19 задержки.

Блок 2 элементов ИЛИ содержит элементы ИЛИ 20-22, анализатор 3 слу- З5 жебной команды содержит регистр 23 и дешифратор 24, анализатор 14 служебных команд — регистр 25 и дефишраторы 26, 26<,, буферный накопитель

5 — регистр 27, первые элементы И 40

28 - 28 первый элемент ИЛИ 29, триггеры 30 — 30р, второй элемент ИЛИ 31, вторые элементы И 32 — 32 дешифратор 33, счетчик 34, элемент И 35 и триггер 36, блок 8 управления — эле- 45 менты И 37, — 37, линию 38 задержки, первый 39 и второй 40 элементы ИЛИ, первый 41, второй 42 и третий 43 триггеры, третий 44, четвертый 45 и пятый 46 элементы HJIH, 50

Устройство защиты от ошибок работает следующим образом.

В исходном состоянии устройства счетчик 17 обнулен, поэтому ключ 18

oTKpb1T ° По окончании процесса фази 55 рования сигнал "Снять фазу" поступает на второй вход счетчика 17 числа фазирований, а через блок 19 задержки и открытый ключ 18 — на второй вход блока 8 управления и первый вход датчика 7 служебных команд.

По этому сигналу через элементы

ИЛИ 39, 40 и 45 срабатывают соответственно триггеры 41-43 блока 8 управления. При этом управляющий сигнал с первого выхода третьего триггера 43 через ч ретий выход блока

8 управления поступает на управляющий вход приемного накопителя 15 и стирает в нем информацию. Сигнал с второго выхода третьего триггера 43 через четвертый выход блока 8 запрещает ввод информации во входной накопитель 1. Управляющий сигнал с выхода второго триггера 42 через первый выход блока 8 управления закрывает ключ 6, а сигнал с выхода триггера 41 через пятый выход блока

8 открывает блокиратор 11. Сигналом об окончании фазирования на инициирующей станции запускается датчик

7 служебных команд, который вырабатывает служебную команду, условно называемую далее СК-1, представляющую собой последовательность из К элементов, не используемую при передаче оперативной информации от источника информации.

Команда СК-1 с первого выхода датчика 7 через элементы ИЛИ 21 и 20 блока 2 элементов ИЛИ поступает на первый вход буферного накопителя 5 и записывается в его регистр 27, а через элементы ИЛИ 21 и 22 блока 2, анализатор 3 служебной команды, кодер 4, где она перекодируется в помехозащищенный код, поступает на выход устройства.

При прохождении команды СК-f через анализатор 3 служебной команды на его втором выходе появляется сигнал, который поступает на второй вход буферного накопителя 5. По этому сигналу срабатывает триггер 36, а счетчик 34 и триггеры 30 -30 устанавливаются в исходное нулевое состояние. Управляющий сигнал с выхода триггера 36 поступает на первый вход элемента И 35, а через второй элемент ИЛИ 31 — на второй вход элемента И 28 и на выход 2р буферного накопителя 5, далее на вход 6, первый вход элемента И 37 блока 8 управления. При этом разрешается прохождение импульсов цикловой частоты через четвертый вход буферного накопителя 5 от задающего генератора 9

1478362 на второй вход счетчика 34, а выход регистра 27, соответствующий максимальной емкости буферного накопителя 5, подключается через элемент

И 28, первый элемент ИЛИ 29 и первый вход буферного накопителя 5 к входу ключа 6 (величина 1 обозначает максимальную емкость накопителя).

Команда СК-1, поступающая из кана- 1ð ла связи на вход устройства противоположной станции, через блокиратор

11 записывается в декодирующий блок

13, где проверяется ее правильность, а затем переписывается в регистр 25 анализатора 14. В результате на выходе 3 дешифратора 26 появляется сигнал, который подается на второй вход датчика 7 служебных команд.

Под действием этого сигнала датчик 2р

7 вырабатывает вторую команду, условно называемую далее СК-2. Принятая команда СК-1 переписывается из регистра 25 в приемный накопитель 15 в котором она сти- 25 рается сигналом, поступающим с третьего выхода блока 8. Команда СК-2 через элемент ИЛИ 22, анализатор 3 и кодер 4 поступает в канал связи.

На инициирующей станции принятая команда СК-2 через открытый блокиратор 11 записывается в декодирующий блок 13, где она кодируется, а затем переписывается в регистр 25 анализатора 14 служебной команды. В результате на выходе дешифратора 26 появляется сигнал, который подается на третьи входы накопителя 5 и блока 8.

Команда СК-2 переписывается из регистра 25 в приемный накопитель 15, 4р где она стирается сигналом, поступаю. щим с третьего выхода блока 8. Под действием сигнала, поступающего на третий вход буферного накопителя 5, срабатывают триггер 36 и один из триггеров 30 — 30 через соответствующий элемент И 32, — 32 в зависимости от сигнала на соответствующем выходе дешифратора 33, определяемого количеством импульсов цикловой час- р тоты, подсчитанных счетчиком 34 с момента передачи команды СК-1 на про. тивоположную станцию до момента приема от нее команды СК-2. После сраба тывания триггера 36 снимаются разрешающий сигнал с первого входа элемента И 35, запрещая прохождение на второй вход счетчика 34 импульсов от генератора 9, и разрешающий сигнал с второго входа элемента И 28 через первый вход второго элемента

ИЛИ 31 °

Пусть, с момента пер дачи команды СК-1 на противоположную станцию до момента приема от нее команды

СК-2 счетчик 34 насчитал такое количество импульсов цикловой частоты, при котором в момент поступления сигнала с выхода дешифратора 26 на третий вход накопителя 5 появляется импульс на (ь-1 ) выходе дешифратора

33, В результате на выходе элемента

И 32 появляется импульс, под действием которого срабатывает триггер

30 . Управляющий импульс с выхода. триггера 30 < поступает на второй вход элемента И 28 <, тем самым создается возможность для съема информации с (ь-1) выхода регистра 27, т.е. выбирается определенная емкость буферного накопителя 5 и, следовательно, определяется цикл повторения дискретной информации. Кроме того, управляющий сигнал с выхода триггера 30 < через 2 < выход накопителя 5 поступает на 6 вход блока 8 и далее на первый вход элемента И 37, . В то же. время под действием сигнала с выхода дешифратора 26„, поступающего на третий вход блока 8 и третий элемент ИЛИ 44, срабатывает триггер 43. В результате с третьего выхода блока 8 поступает сигнал, разрешающий считывание информации из накопителя 15, а с четвертого выхода поступает сигнал, разрешающий ввод информации от источника в накопитель 1.

В случае обнаружения ошибки при приеме команды СК-1 на втором выходе декодирующего блока 13 появляется управляющий сигнал, который через четвертый вход блока 8 поступает на второй вход пятого элемента ИЛИ 46.

С выхода последнего управляющий сигнал через элемент И 37 записывается на первый вход линии 38 задержки, для которой продвигающими сигналами являются импульсы цикловой частоты, поступающие на пятый вход блока 8 от задающего генератора 9. Кроме того, прад действием сигнала с выхода элемента ИЛИ 46 срабатывают первый

41 и второй 42 триггеры, запускается (по второму выходу блока 8) датчик

10 запросной комбинации, который вы дает в канал связи запросную комби1478362 нацию, а через четвертый элемент

ИЛИ 45 срабатывает третий триггер 43.

В результате переключения первого триггера 41 блокируется прием информации из канала связи на Ю тактов цикловой частоты, сигналом с первого выхода третьего триггера 43 стирается информация в накопителе 15 и запрещается считывание информации от источника в накопитель 1, а сигналом с выхода второго триггера 42 разрешается считывание информации из регистра 27 накопителя 5 через ключ 6, элементы ИЛИ 21 и 22 блока 2, анализатор 3 и кодер 4 в канал связи, а также с выхода элемента ИЛИ 21 через элемент ИЛИ 2О на первый вход накопителя 5.

Принятая инициирующей станцией запросная комбинация через блокиратор t1 поступает на дешифратор 12 запросной комбинации, где она выделяется. В результате на выходе дешифратора 12 появляется сигнал, который поступает на первый вход блока 8 и далее через элемент ИЛИ 46, элемент И 37 записывается на первый вход линии 38 задержки. Кроме того, под действием сигнала с выхода элемента ИЛИ 46 срабатывают первый 4 1 и второй 42 триггеры, запускается (по второму выходу блока 8) датчик

10 запросной комбинации, который выдает в канал связИ запросную комбинацию, а через элемент И 45 срабатывает третий триггер 43. В результате переключения триггера 41 блокируется прием информации из канала связи на

В тактов цикловой частоты, сигналом с выхода триггера 43 стирается информация в накопителе 15 и запрещается ввод информации от источника, а сигналом с выхода триггера 42 разрешается перезапись и считывание с регистра 27 накопителя 5 команды

СК-1 через ключ 6, блок 2, анализатор 3 и кодер 4 в канал связи. К моменту приема команды СК-1 противоположной станцией на выходе ф линии

38 задержки блока 8 появляется сигнал, который через элементы ИЛИ 40, 44 и 39 воздействует соответственно на триггеры 42, 43 и 41. В результате переключения триггера 43 с его первого выхода поступает разрешающий сигнал на управляющий вход накопителя

15, а с второго выхода триггера 43 поступает сигнал, разрешающий считывание информации от источника в накопитель 1. Сигнал с выхода триггера

42 разрешает перезапись и считывание информации из накопителя 5 через ключ

6, а в результате переключения триггера 41 открывается блокиратор 11, разрешая прием информации из канала связи. В случае- искажения команды

СК-1 в канале связи ошибка обнаруживается декодирующим блоком 13 и процесс запроса повторяется вновь.

При искажении команды СК-2 в канале связи ошибка обнаруживается на инициирующей станции декодирующим блоком 13 и процесс определения цикла повторения начинается вновь, как описано, с передачи команды СК-1.

Процесс определения цикла повторения в противоположном направлении происходит аналогично. Процесс определения цикла повторения происходит до тех пор, пока команда СК-2, передаваемая в ответ на полученную команду

СК-1, будет принята без искажений.

В процессе работы устройства импульсы цикловой частоты через делитель 16 поступают на первый вход счетчика 17 и сбрасывают его в нулеI вое состояние, этим обеспечивается удержание ключа 18 в положении "Открыто". Если по какой-либо причине число фазирований возрастает 3а установленный период, определяемый .делителем 16, и превышает допустимую величину, срабатывает счетчик 17 и закрывает ключ 18, что предотвращает переключение устройства в режим определения емкости буферного накопителя 5 и тем самым исключаются наоправданные потери пропускной способности.

Таким образом, предложенное устройство обеспечивает повышение эффективности скорости передачи информации по сравнению с известным устройством за счет сокращения количества обменов служебными командами при частых фазированиях.

15

25

35

45

Устройство защиты от ошибок по авт.св. И 1197115, о т л и ч а ю— щ е е с я тем, что, с целью повышения скорости передачи информации, введены делитель цикловой частоты, счетчик числа фазирования, ключ и блок задержки, выход которого соеди55

50 формула изобретения

1478362 нен 6 информационным входом ключа, выход которого подключен к второму входу блока управления, а управляющий вход соединен с выходом счетчика числа фазирований, установочный вход которого соединен с выходом делителя цикловой частоты, вход которого подключен к выходу зада .щего генератора, а счетный вход счетчика числа фази5 рований соединен с входом блока задержки и является входом сигнала окончания фазирования устройства.

1478362

Составитель В.Микуцкий

Техред Л.Олийнык

Корректор M.Màêñèìèøèíåö

Редактор И.Шмакова

Заказ 2375/56 Тираж 627 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушакая наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина,101

II Н