Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных комплексах. Целью изобретения является расширение класса решаемых задач путем обеспечения преобразования передаваемой через устройство информации. Цель достигается тем, что в устройство, содержащее входной и выходной коммутаторы, два счетчика, два дешифратора и первую группу регистров, введены блок триггеров условий преобразования, блок элементов И , блок элементов ИЛИ, вторая группа регистров, два триггера, два элемента ИЛИ, элемент И и три элемента задержки. Информация от источника поступает квантами (например, байтами) и запоминается на буферных регистрах первой группы. После приема последнего кванта информация в преобразованном виде передается на выходные регистры второй группы и выдается приемнику информации словами (например, 32- или 64-разрядными). Прием и передача информации осуществляются независимо и сопровождаются соответствующими синхроимпульсами. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (51)4 G 06 F 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4272310/24-24 (22) 30 ° 06.87 (46) 15.05.89, Бюл. № 18 (72) С.В.ЕАимов, M ° M,Çàðåöêèé и В.А.Кулистов (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 1166125, кл. G 06 Е 13/00, 1984 .

Авторское свидетельство СССР

¹ 881722, кл. С 06 F 13/00, 1979. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано в вычислительных комплексах. Целью изобретения является расширение класса решаемых задач путем обеспечения преобразования передаваемой через устройство информации.

Цель достигается тем, что в устройст3

Изобретение относится к вычислительной технике и может быть использовано в вычислительных комплексах.

Целью изобретения является расширение класса решаемых задач путем обеспечения преобразования передаваемой через устройство инАормации.

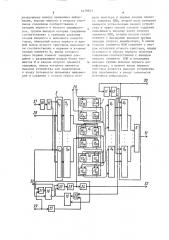

На чертеже представлено предлагаемое устройство.

Устройство содержит блок 1 триггеров условий преобразования, состоящий из р»р триггеров 2 (р — число квантов входной информации), входной коммутатор 3, состоящий из р групп элементов И 4, первую и вторую группы регистров 5 и 6, выходной коммутатор 7, состоящий из

„„SU, „, 1479935 во, содержащее входной и выходной коммутаторы, два счетчика, два дешиАратора и первую группу регистров, введены блок триггеров условий преобразования, блок элементов И, блок элементов ИЛИ, вторая группа регистров, два триггера, два элемента ИЛИ, элемент И и три элемента задержки.

ИнАормация от источника поступает квантами (например, байтами) и запоминается на буАерных регистрах первой группы. После приема последнего кванта информация в преобразованном виде передается на выходные регистры второй группы и выдается приемнику информации словами (например 32р

Ю или бч-разрядными). Прием и передача информации осуществляются независимо и сопровождаются соответствующими синхроимпульсами. 1 ил. групп элементов И 8 и группы элементов ИЛИ 9, счетчики 10 и 11, дешифраторы 12 и 13, блока 14 элементов И, образованный группами элементов И 15, блок 16 элементов ИЛИ, образованный Щ

К х Ь группами элементов ИЛИ 17 (K— число слов в выходном сообщении, число квантов входной информации, размещаемых в выходном сообщении), триггеры 18, 19, элемент И 20, элемен- а ты ИЛИ 21 и 22, элементы 23, 24 и 25 задержки, группу входов 26 задания условий преобразования, синхровход

27 записи, группу информационнных входов 28, установочный вход 29, синхровход 30 чтения, группу информа- ционных выходов 31, выходы 32 и 33

1479935 оповещения приемника и источника информации.

Устройство работает следующим образом 5

Импульс запуска, поступающий на вход 29, устанавливает в единичное состояние триггеры 18 и 19. С прямого выхода триггера 18 на выход 33 поступает единичный потенциал, разрешающий выдачу информации источником »а группу входов 28. Каждый кваIIT I III1toptt ttI H oT Hc o Hitt ott coii ровождается синхроимпульсом, поступающим на вход 27, который изменяет состояние счетчика 10. С помощью дешифряторя 12 и коммутатора 3 производится последовательное запоминание квантов информации ня регистрах

5. Импульс синхронизации записи в последний регистр 5 одновременно устанавливает триггер 18 в пулевое состояние. При этом на выход 33 поступает нулевой потенциал, запрещающий выдачу информации источником, а с

25 инверсного вы; ода триггера 18 на вход элемента И 20 поступает единичный потенциал, из которого с задержкой, равной сумме задержек элементов 23 и

ЗО

24, IIепочкой, состоящей из элемента

И 20, элементов задержки 23 и 24, триггера 19, формируется импульс готовности устройства к выдаче информации приемнику, поступающей на выход 32. K этому моменту по импуль- 35 су с выходя элемента задержки 23 путем стробировяния элементов И 15 производится передача информации с регитров 5 на регистры 6 с одновременной сортировкой ее в соответствии с 40 информацией, записанной в триггеры 2.

Информация В блок 1 заносится перед началом работы устройства. Гдипица с выхода одного из триггеров

2 каждой строки разрешает передачу информации с регистров 5 через соответствующие элементы И 15 на регистр

6. Импульс с выхода элемента задержки 24 поступает также на вход эле- . мента ИЛИ 21 и устанавливает триггер

18 в единичное состояние, что вновь разрешает выдачу информации источником.

После получения импульса готовности с выхода 32 приемник информации начинает выдавать IIB Itxo 30 сННхро импульсы запроса, которые изменяют состояние счетчика 11, С помощью дешифратора 13 производится поочередная выдача информации через соответствующие элементы И 8 и элементы ИЛИ 9 с выходов регистров 6 на выходы 31 устройства к приемнику информации. Сигнал, открывающий элементы И 8, одновременно устанавливает триггер 19 в единичное состояние, чем инициируется новый цикл передачи информации с регистров

5 в регистры 6 при условии заполнения регистров 5 новой информацией (триггер 18 в нулевом состоянии).

Формула изобретения

Устройство для сопряжения источника и приемника лнформации, содержащее первый и второй счетчики, входы которых являются соответствующими входами устройства для подключения к гинхронизирующим выходам источника и приемника информации, два дешифратора, входной коммутатор, группа информационных входов которого является группой входов устройства для подключения к группе информационных выходов источника информации, i-я группа выходов входного коммутатора (i = 1, р) подключена к группе входов 1-го регистра первой группы, выходной коммутатор, группа выходов которого является группой выходов устройства для подключения к группе информационных входов приемника информации, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач устройства, в него введены блок триггеров условий преобразования, блок элементов И, блок элементов ИЛИ, вторая группа регистров, два триггера, два элемента ИЛИ, элемент И и три элемента задержки, причем выходы регистров первой группы подключены к первой группе входов блока элементов И, второй группой входов соединенного с группой выходов блока триггеров условий преобразования, группа входов которого является группой Входов задания условий преобразования устройства, i-я группа выходов блока элементов

И соединена с i-й группой входов блока элементов ИЛИ, 1-я группа

ВыхОдОВ KQTopoI"o (j = 1 k) подклю» чена через j-й регистр второй группы к j-й группе информационных входов выходного коммутатора, стробирующий вход которого соединен с входом устройства для подключения к синхро1479935 низирующему выходу приемника инфор)

1 мации, выходы первого и второго счетчиков соединены соответственно с входами первого и второго дешифрато5 ров, группы выходов которых соединены соответственно с группами адресных входов входного и выходного коммутаторов, инверсный выход первого и прямой выход второго триггеров подключе- 1Î ны соответственно к первому и второму входам элемента И, выход которого через первый элемент задержки соединен с разрешающим входом блока элементов И и входом второго элемента 15 задержки, выход которого является выходом устройства для подключения к входу готовности приемника информации и соединен с входом сброса второго триггера и первым входом первого элемента ИЛИ, второй вход которого является установочным входом устройства и через третий элемент задержки подключен к первому входу второго элемента ИЛИ, вторым вхсдом соединенного с последним выходом группы выходов второго дешифратора, а выход второго элемента ИЛИ соединен с входом установки второго триггера, входы установки и сброса первого триггера соединены соответственно с выходом первого элемента ИЛИ и последним выходом группы выходов первого дешифратора, а прямой выход первого триггера является выходом устройства для подключения к входу готовности источника информации.