Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах универсальных и специализированных ЭВМ. Цель изобретения - расширение функциональных возможностей за счет выполнения умножения двоичных чисел в дополнительных кодах. В устройство, содержащее сдвиговые регистры сомножителей, две группы элементов И и регистр результата, введены два элемента И, элемент ИЛИ, блок управления и блок преобразования кода. Это обеспечивает выполнение умножения параллельным кодом при представлении его в устройство последовательным кодом, коррекцию псевдорезультата по знаку множимого и накопление сумм парных произведений в регистре результата. 2 з.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СНИДЕТНЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4285879/24-24 (22) 20.07.87 (46) 23.05.89. Бюл. № 19 (71) Институт кибернетики им. В. М. Глушкова (72) В. А. Вышинский и Ю. Я. Ледянкин (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 905814, кл. G 06 F 7/52, 1980.

Авторское свидетельство СССР № 1203512, кл. G 06 F 7/52, 1984. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах униИзобретение относится к вычислительной технике и может быть использовано в арифметических универсальных и специализированных цифровых вычислительных машинах.

Целью изобретения является расширение функциональных возможностей за счет выполнения умножения двоичных чисел в дополнительных кодах.

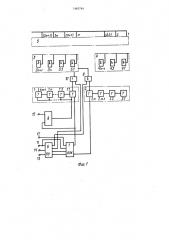

На фиг. 1 представлена схема устройства; на фиг. 2 — схема блока управления; на фиг. 3 — схема блока преобразования кода.

Устройство содержит (n+1)-разрядный сдвиговый регистр 1 первого сомножителя и и-разрядный 2 сдвиговый регистр второго сомножителя, первую 3 группу из (и+1) -го элементов И, вторую 4 группу из (и-1)-го элементов И, регистр 5 результата, блок 6 управления, блок 7 преобразования кода, элементы И 8 и 9, элемент ИЛИ 10, первый

11 и второй 12 соответственно информационные входы устройства, управляющие входы

13 — 15 устройства.

SU» 1481744 А1 версальных и спекиалHÇHDo-,ÿнных ЦВМ.

Цель изобретения — расшн с:ие функциональных возможностей за счет выполнения умножения двоичных чисел ь дополните .ьных кодах. B устройство, содержащ.с сдвнговые регистры сомножителей. две гру . i»i элементов И и регистр результата, введены два элемента И, элемент ИЛИ, блок управления и олок преобразован я i 0, i,а, это обеспечивает выполнение х множения параллельным кодом при представлении его в устройство последовательным кодом, коррекцию псевдорезу. ьтата по знаку множимого и накопление сумм парных произведений в регистре результата. 2 злl. ф-лы, 3 ил.

Схема блока управления |фи;, 1) содержит 1К-триггер 16, элементы И 17 и элемент HE 18.

Схема блока преобразования кода (фиг. 3) содержит ., К-триггер 19, два элемента НЕ 20 и 21 и два элемента 2И---ИЛИ

22 и 23.

Элемент И 8 служит для установки регистр а 1.

Устройство для умножения работает следующим образом.

При работе устройства на первом тгктс передается знаковый разряд (а.) множителя (В), представленного дополнительным кодом. Он может быть ргзен о.=1 либо о .=О и в устройство поступает через вход

11, передается на вход блока управления и на первый информационный вход блока преобразования кода.

Если множитель отрицательный (т.е. сов=1), триггер 16 блока управления устанавливается в «1».

1481744

61 QlQ2Q3Q4b2b3b4

b2 ®стa1a2a3b3b4 (23 < 3д 4o„a1Q2b4

b4 <о coÄco„а1 а1 аз 41з =О а2 а1 в„=О либо 1

b.

Р2

Ьз

1Р4

QlQ2Q3Q4

coÄ а1а2а3а4

и1 < 1 Q1Q2Q3Q4 со„со „ю„а1a2aoa4

Если 13и=О, то по сигналу управления

Уl, который в первом такте подается на вход 13 устройства, триггер 16 блока управления установится в «О».

Далее по знаку множимого (boa= О или и> 1), который поступает через вход

12 устройства, по сигналу управления У2, поступающему на вход 15 устройства во втором такте умножения, будут установлены в «О» или «1» все разряды сдвигового регистра 1. При этом, если ц2

= О, то множимое поступает на вход первого разряда сдвигового регистра 1 в коде представления.

При отрицательном множителе триггер 16 блока управления в первом такте устанавливается в «!». Это означает, что знак множимого 134=0 или 43=! уже во втором такте, преобразуясь в блоке 7 преобразования кода, поступает на входы сдвигового регистра 1 в обратном коде.

Код множимого поступает на вход сдвигового регистра 1 старшими разрядами вперед, а код множителя поступает на вход сдвигового регистра 2 младшими разрядами вперед. Поэтому в третьем такте в устройство поступает младший разряд (первый) множителя, а в четвертом такте— старший разряд (и-й) множимого и т.д. до (2п+2) -го такта, после которого будут заведены в сдвиговые регистры все разряды множимого и множителя. Причем (и+1) -й разряд множимого устанавливается во втором такте, а (п+1) -й разряд множителя должен быть всегда равен <О».

Нули множителя (В) по указанному для со =! тракту проходят на вход сдвигового регистра 2 без изменения, включая в первую единицу (младший разряд множителя, отличный от нуля), которая также проходит блок преобразования кода без изменения йо она устанавливает триггер 9 блока преобразования кода в «1». Далее на вход сдвигового регистра 2 значение множителя уже будет поступать в инверсном коде.

Каждая новая пара текущих информационных разрядов сомножителей заводится в оба сдвиговые регистры 1 и 2. Их кон.ьюнкция определяет и-й разряд частичного произведения в регистре 5. Кроме того, значение «!» или «О» введенного текущего разряда множимого разрешит или запретит соответственно ввод /-х (j= 1, (n — 1) разрядов кода множителя через вторую 4 группу элементов И в младшие (n — 1) -е разряды. регистра 5, а значения «1» или «О» множителя разрешат илииааиоетит, соотиетственно ввод i-x (i=2, (n+1) разрядов кода множимого через первую 3 группу элементов И в старшие (2п+1)- — n разряды регистра 5.

При работе устройства с первого такта до корректирующего второй вход элемента И

9 разрешает прохождение сигнала с выхода

40 сдвигового регистра 2, а второй вход элемента ИЛИ 10 отключен. Осуществляется коррекция следующим образом.

На (2п+3) -м такте на вход 14 устройства поступает сигнал управления (УЗ), который отключает элемент И 9 устройства, поэтому содержимое сдвигового регистра 1 не пройдет через первую 3 группу элементов устройства на входы регистра 5. Одновременно сигнал управления УЗ поступит на второй вход элемента ИЛИ 10 устройства. И тем самым обеспечит коммутацию j-x разрядов кода содержимого (1=1,n) сдвигового регистра 2 в соответствующие j-e (j=1, n) разряды регистра 5 через i-e (j=l, n) элементы И второй группы 4.

Отключение элемента И 9 с одновременным включением или отключением элемента ИЛИ 10 осуществляется из блока управления. После этого в регистре и накопилось в виде двухрядного кода результатов и переносов очередное произведение двух сомножителей. Со следующего после корректирующего такта в устройство может быть подано значение знакового разряда (co ) кода множителя или необходимо в течение (2п+1) -го такта прогнать переносы из младших разрядов регистра 5 в старшие, если последнее умножение было последним в даннои группе.

Устройство реализует новый алгоритм умножения, который модернизирует два известных. Первый из них формирует частичные произведения в прямых кодах в виде некоторого треугольника, а второй — в дополнительных кодах. Суть алгоритма в том, что на входах регистра 5 формируются частичные произведения по правилу:

Суммирование приведенных строк равносильно следующему:

Для одновременного преобразования кода в дополнительный и его поразрядной передачи в устройство старшими разрядами вперед используется передача его обратным кодом (если со„= 1) с последующей коррекцией псевдорезультата, накопленного в регистре. Она выполняется в виде сложения кода множителя, преобразованного (при со, =1) в дополнительный с псевдорезультатом, накопленным в регистре 5.

1481744

Формула изобретения

15

25

1. Устройство для умножения, содержащее (n+1) -разрядный сдвиговый регистр первого сомножителя, п-разрядный сдвиговый регистр второго сомножителя, (n-разрядность сомножителей без учета знака), две группы из n+1 и и — 1 элементов И соответственно, (2n+1) -разрядный регистр результата, причем первые входы i-x элементов И первой группы (i=1,2,...,n+1) соединены между собой, второй вход первого элемента И первой группы соединен с первыми входами 1-х элементов И второй группы (1=1,2,...,n — 1), вторые входы которых соединены соответственно с выходами j-x разрядов п-разрядного сдвигового регистра второго сомножителя, выходы К-х разрядов (л+1)-разрядного сдвигового регистра первого сомножителя соединены соответственно с вторыми входами К-х элементов И первой группы (К=2,3,...,n+1), выходы элементов

И второй и первой групп соединены соответственно с входами (2n+1) -х разрядов регистра результата, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения умножения двоичных чисел в дополнительных кодах, в него введены два элемента И, элемент ИЛИ, блок управления и блок преобразования кода, причем вход первого сомножителя устройства соединен с входом синхронизации блока управления и первым информационным входом блока преобразования кода, второй информационный вход которого соединен с входом второго сом ножителя устройства, первый управляющий вход которого соединен с входом установки знакового разряда множителя блока управления, первый и второй выходы которого соединены соответственно с первым и вторым управляющим входами блока преобразования кода, первый выход которого соединен с информационным входом первого разряда (n+1)-разрядного сдвигового регистра первого сомножителя и первым входом первого элемента И, второй вход которого соединен с вторым управляющим входом устройства, а выход — с входом установки в «1» (n+1)-разрядного сдвигового регистра первого сомножителя, второй выход блока преобразования кода соединен с информационным входом п-го разряда п-разрядного сдвигового регистра второго сомножителя, выход а-го разряда:-}оторого соединен с первым входом второго элемента И, выход которого соединен с первым входом первого элемента И первой группы, второй вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом первого разряда (n+1)-разрядного сдвигового регистра первого сомножителя, а второй вход — с третьим выходом блока управления, четвертый выход которого соединен с вторым входом второго элемента И, третий управляющий вход устройства соединен с входом разрешения коррекции блока управления.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит элемент И, элемент НЕ и jK-триггер, j-вход которого соединен с входом потенциала единицы, вход синхронизации jK-триггера соединен с входом синхронизации блока, вход установки знакового разряда множителя которого соединен с К-входом jK-триггера, прямой выход которого соединен с первым выходом блока и первым входом элемента И, второй вход которого соединен с входом ра=.,ðåøåíèÿ коррекции блока и входом элемента НЕ, выход которого соединен с четверть}м выходом блока, второй и третий выходы которого соединены соответственно с инверсными a}}xoдами }К-триггера и элемента И.

3. Устройство по и. !, отличающееся тем, что блок преобразования кода содержит

jK-триггер, два элеъ:сита 2И вЂ” ИЛИ и два элемента НЕ, причем .}epaa!»: информационный вход блока соединен с входом с}}нхронизации jK-триггера, вхоло } } срвого элемента 2И вЂ” ИЛИ, второй вхс д которого соединен с инверсным выходом j K-триггера, прямой выход которого соединен с третьим входом первого элемента 2И- — ИЛИ, четверть}й вход которого соединен с выходом }lc}iao}.o элемента НЕ, а выход — с вторым выходом блока, первый выход которого соедин:}» с выходом второго элемента 2И вЂ” ИЛИ, первый вход которого соединен с входом ьторого элемента НЕ и вторь}м информационным входом блока, второй управляющий вход которого соединен с вторым входом второго элемента 2И вЂ” ИЛИ, третий вход которого сосдинен с выходом второго элемента HE. a четвертый вход — с первым управляющим входом блока и j-входом jK-триггера, K-вход которого соединен с нулевым потенциалом.

1481744

1481744

Составитель Е. Мурзина

Редактор Л. Гратилло Техред И. Верес Корректор С. Черни

Заказ 2690/49 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент>, г. Ужгород, ул. Гагарина, 101