Устройство для деления двоичного кода на (2 @ -1)

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для формирования адресов оперативных запоминающих устройств средств отображения информации. Цель изобретения - повышение быстродействия. Устройство содержит накапливающий сумматор 1, регистр сдвига 2, блок 3 микропрограммного управления, первый 4 и второй 5 элементы И и счетчик 6. Сокращение времени выполнения операции деления достигается за счет уменьшения сдвиговых операций. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК дц4 G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4303509/24-24 (22) 07.09.87 (46) 23.05.89. Бюл. № 19 (71) Научно-производственное объединение

«Автоматика» (72) В. А. Роспономарев и В. Я. Кривчик (53) 681.325 (088.8) (56) Патент США № 4334285, кл. G 06 F 7/52 опублик. 1982.

Авторское свидетельство СССР № 1425660, кл. G 06 F 7/52,,09.03.87.

„„Я0„„1481746 А1

2 (54) УСТРОЙСТВО Д 1V ДЕЛЕНИЯ ДВОИЧНОГО КОДА НА (2" -1) (57) Изобретение относится к вычислительной технике и может быть использовано для формирования адресов оперативных запоминающих устройств средств отобра жения информации. Цель изобретения -- повышение быстродействия. Устройство содержит накапливающий сумматор 1, регистр сдвига 2, блок 3 микропрограммного управления, первый 4 и второй 5 элементы И и счетчик 6. Сокращение времени выполнения операции деления достигается за счет уменьшения сдвиговых операций. 2 ил.

1481746

Изобретение относится к области вычислительной техники и может быть использовано в целях формирования адресов оперативных запоминающих устройство средств отображения информации.

Цель изобретения — повышение быстродействия.

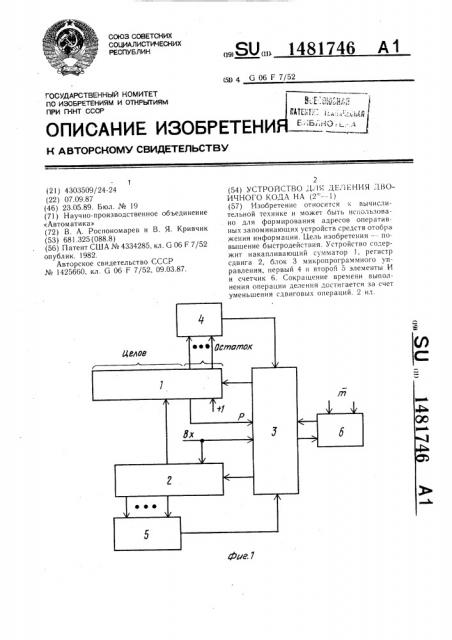

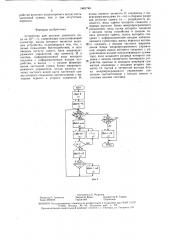

На фиг. 1 представлена функциональная схема устройства для деления двоичного кода на (2 — 1); на фиг. 2 — алгоритм работы устройства.

Устройство для деления двоичного кода на (2 " — 1) содержит накапливающий сумматор 1, регистр 2 сдвига, блок 3 микропрограммного управления, первый 4 и второй

5 элементы И и счетчик 6.

Накапливающий сумматор 1 двухтактовый. Разрядность его составляет (и+1), перенос осуществляется с m-го разряда.

Регистр 2 сдвига предназначен для занесения в него делимого и сдвига кода делимого.

Элемент И 4 предназначен для фиксации единичного кода остатка от деления.

Количество входов элемента И 4 равно т.

Элемент И 5 предназначен для фиксации нулевого кода на выходе (n — т)-х старших разрядов регистра 2 сдвига.

Счетчик 6 служит для определения количества сдвигов, формируемых блоком 3 микропрограммного управления, в зависимости от числа т.

Делимое D представлено и- разрядным двоичным кодом. Делитель d равен (2" — 1), где т=1,2,...,m, и выбирается пользователем. Результат определяется целой величиной и остатком. Целое определяется (n—

m+ 1) -и старшими разрядами сумматора 1, остаток определяется т младшими разрядами, n)m. Устройство осуществляет последовательное деление делимого D и незадействованных оста гков на 2" . При этом имеем — „,=S i+6s,;

Ь .Л у = 2+ Ь - j

S„=>-s р Sl — 1+б5п — 1ь

S;.iЛ

2 — О+Ь,.

Дополнение Л делителя до 2 " в данном слу ае равно единице. Частичные суммы (1) выделяют целую часть S; и остаток Ь, S S,...,S; — значения задействованных величин при делении на 2", Ь,Ь,...,6s, — значения остатков задействованных величин; — значения величин, не задейст— вованных при делении на де— литель (2 " — 1) ..

S, i.Л

Признаком окончания деления на 2" является нулевая целая часть частичной суммы (1), которая в устройстве контролируется элементом И 5.

Целое и остаток частного определяются суммированием частичных сумм с уче том переполнения остаточных частичных сумм и анализа полноты остатка.

Переполнение m разрядного кода остатка

2 "=d+ 1 (2) свидетельствует о наличии единицы в остатке частного. Выравнивание частного по переносу осуществляется прибавлением единицы к полученному результату при сложении частичных сумм.

Остаток, равный делителю d

d= 2 " — 1 = 1 1 ...! (3)

15 есть целое число. Анализ завершается прибавлением единицы к окончательному результату. Контроль остатка производится элементом И 4.

Устройство функционирует в соответствии с выражениями (1) — (3). Пользователь предварительно выбирает разрядность и делимого, определяет делитель d=(2 " — !) и в зависимости от величины m производит коммутацию элементов И 4 и 5. д Устройство работает следующим образом (фиг. 2).

При запуске устройства код делимого заносится B регистр 2 сдвига, блок 3 управления производит сброс сумматора 1 и заносит содержимое регистра 2 сдвигов в

ЗО сумматор 1.

При равенстве целой части частичной суммы нулю, что фиксируется элементом

И 5, анализируется остаток от деления элементом И 4 в соответствии с выражением (3). Если остаток частного равен

35 11...1, блок 3 управления приформировывает единицу к содержимому сумматора l.

Процесс деления завершается как и в случае, если остаток частного не равен 11...1.

В случае, если целая часть частичной суммы не равна 00...0, блок 3 управления вырабатывает т импульсов, сдвигающих код в регистре 2 сдвига на m разрядов, после чего содержимое регистра 2 сдвига заносится в сумматор 1, суммируясь с его содержимым.

Формирование m импульсов блоком 3 управления прои водится следующим образом. Осуществляется ввод величины m в счетчик 6, формируется импульс, осуществляющий сдвиг содержимого в регистре 2 сдвига. Блок 3 управления анализирует

$Q полное заполнение счетчика 6 единицами

11...1, если заполнения нет, то к содержимому счетчика 6 прибавляется единица, процесс формирования импульса сдвига повторяется до полного заполнения счетчика 6 единицами 11...1.

После сложения блок 3 управления анализирует перенос с m-ro выхода сумматора 1. Если перенос был, то к содержимому сумматора прибавляется единица. Уст481746

Формула изобретения

ôèã. 2

Составитель Е.Мурзина

Редактор Л. Гратилло Техред И. Верее Корректор В. Гирняк

Заказ 2690/49 Тираж 669 П одп исное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101

1 ройство начинает анализировать целую часть частичной суммы, как и при отсутствии переноса.

Устройство для деления двоичного кода на (2" — 1), содержащее накапливающий сумматор, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр сдвига, блок микропрограммного управления, два элемента И и счетчик, информационный вход которого соединен с информационным входом устройства, а выход — с входом формирования частичной суммы блока микропрограммного управления, входы анализа остатка частного целой части частичной суммы которого соединены соответственно с выходами первого и второго элементов И, 6 входы первого элемента И соединены с инверсными выходами (n — m) -x старших разря дов регистра сдвига (n — разрядность делимого), вход сдвига которого соединен с первым выходом блока микропрограммного управления, вход пуска которого соединен с входом пуска устройства и входом записи регистра сдвига, выход которого соединен с информационным входом накапливающего сумматора, выход переноса котороtO го соединен с входом частного выравнивания блока микропрограммного управления, второй выход которого соединен с управляющим входом накапливающего сумматора, вход младшего разряда которого соединен с входом единичного потенциала устройства, выходы m младших разрядов сумматора соединены с входами второго элемента И, третий и четвертый выходы блока микропрограммного управления соединены соответственно с входом записи и счетным входом счетчика.