Устройство для умножения чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено для быстрого выполнения операции умножения двоичных и десятичных чисел. Особенно эффективно его использование при применении БИС и СБИС. Целью изобретения является сокращение аппаратурных затрат за счет новой организации связей. Устройство для умножения чисел содержит группу блоков 1 умножения, группы 2, 3 суммирования, группы буферных регистров 5-7 и группу регистров 8 произведения. 2 з.п.ф-лы, 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5И 4 б 06 F 7 52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4318783/24-24 (22) 20.10.87 (46) 23.05.89. Бюл. № 19 (72) А. А. Жалковский, А. А. Шостак и Л. О. Шпаков (53) 681.325 (088.8) (56) Авторское свидетельство СССР № !229758, кл. G 06 F 7/52, 1982.

Авторское свидетельство СССР № 842800, кл. С 06 F 7/52, 1979. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

ЧИСЕЛ

„„SU„„È81748 А 1

2 (57) Изобретение относится к вычислительной технике и может быть применено для быстрого выполнения операции умножения двоичных и десятичных чисел. Особенно эффективно его использование при применении БИС и СБИС. Целью изобретения является сокращение аппаратурных затрат за счет новой организации связей.

Устройство для умножения чисел содержит группу блоков 1 умножения, группы блоков 2, 3 суммирования, группы буферных регистров 5 — 7 и группу регистров 8 произведения. 2 з. п. ф-лы, 5 ил.

1481748 сум мирова ния, выходы 4 — 4. сум мы соответственно блоков 2i — 2. суммирования первой группы, первую, вторую и третью группы буферных регистров 5, — 5, 6 — 6 и 7 — 7. соответственно, группу регистров 8i — 8. i произведения, входы 9 — 9 переноса соответственно блоков 2i — 2 суммирования первой группы, вход 10 множителя устройства, группу входов 11 — 11, цифр множимого устройства, вход 12 зна- 30 чения коррекции устройства, входы 13 и 14 соответственно первой и второй констант устройства, вход 15 логического нуля устройства, выходы 16 — 16 i соответственно регистров 7i — 7м+ третьей группы, выход 17 младшей части произведения устройства, 35 группу выходов 18 — 18 цифр старшей части произведения устройства, вход 19 начальной установки устройства, первый тактовый вход 20 устройства, выходы

21 — 21M+1 блоков 3i — 3»+i суммирования

40 второй группы соответственно, вход 22 задания режима устройства, второй тактовый вход 23 устройства, выходы 24 — 24 старших частей произведений и выходы 25i—

25. младших частей произведений блоков

1 — 1. умножения, группы выходов 26 — 26 буферных регистров 5i — 5. первой группы

Изобретение относится к области вычислительной техники, может быть использовано для умножения двоичных и десятичных чисел и может найти примененение в качестве основы при разработке быстродействующих арифметических устройств универсальных ЭВМ, работающих как с двоичными, так и с десятичными числами.

Целью изобретения является сокращение аппаратурных затрат.

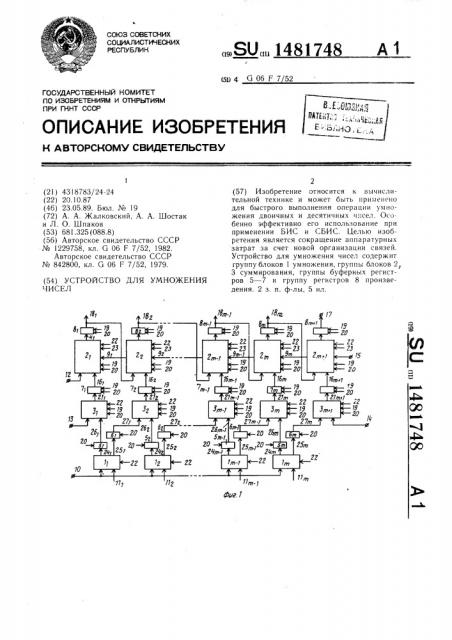

На фиг. 1 показана структурная схема устройства для умножения чисел; на фиг. 2— структурная схема блока суммирования первой группы; на фиг. 3 — структурная схема блока суммирования второй группы; на фиг. 4 и 5 — потактные временные диаграммы выполнения соответственно двоичного и десятичного умножения.

Устройство для умножения чисел содержит (фиг. 1) группу блоков li — 1 умножения, первую группу блоков 2i — 2+ суммирования, вторую группу блоков 3 — 3 соответственно, выходы 27 — 27. буферных регистров 6i — 6 второй группы соответственно.

Блок 2 суммирования первой группы содержит (фиг. 2) сумматор 28, корректор 29, триггер 30 и мультиплексор 31.

Блок 3 суммирования второй группы содержит (фиг. 3) сумматор 32, корректор 33 и триггер 34.

Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства.

Каждый из блоков 1i — 1 умножения осуществляет умножение соответствующей

20 тетрады разрядов множимого на тетраду разрядов множителя. В зависимости от значения потенциала, поступающего с входа 22 ,на вход задания режима блока 1 умножения на его выходе 24 старшей и выходе

25 младшей части произведения появляется результат умножения либо в двоичном, либо в двоично-десятичном коде. Потенциал логической единицы на входе 22 обеспечивает работу устройства в десятичной системе счисления, а потенциал логического нуля — его работу в двоичной системе счисления. Блоки 1! — 1. умножения целесообразно реализовать в виде

ППЗУ. В этом случае младшая или старшая часть двоично-десятичного произведения на выходах блока умножения могут формироваться уже скорректированными на

«+6» без каких-либо дополнительных аппаратурных затрат.

Блоки 2 — 2;+i суммирования первой группы предназначены для формирования промежуточных и окончательного результатов при выполнении операции двоичного и десятичного умножения, причем все они работают идентичным образом. Рассмотрим функциональное назначение узлов блока 2р (р=2, 3, ..., м). В нем (фиг. 2) на суматоре 28 осуществляется суммирование значений двух тетрад, поступающих с выхода

18, регистра 8р- произведения и с выхода 16 буферного регистра 7 третьей группы, причем значение выходного переноса сумматора 28 запоминается в триггере 30, которое в следующем такте подается с выхода триггера 30 на вход младшего разряда второго входа сумматора 28. Значение входного переноса сумматора 28 поступает через мультиплексор

31 либо с выхода младшего разряда буферного регистра 7р третьей группы, либо с выхода переноса сумматора 28 более старшего (р+1) -го блока суммирования первой группы. Коммутация выхода триггера 30 с входом младшего разряда второго входа сумматора 28 обеспечивает возможность быстрого приведения переносов в конце выполнения операции умножения. В этом случае сквозной перенос в блоках 2i — 2м суммирования первой группы распространяется через мультиплексоры 31 и одновременно в каждом блоке на сумматоре 28 подсуммируется содержимое триггера 30. Настройка же мультиплексоров 31 блоков суммирования первой группы на передачу информации через их вторые входы осуществляется потенциалом логической единицы с входа 23 устройства.

При выполнении в устройстве двоичного умножения корректор 29 настраивается потенциалом логического нуля с входа 22 на передачу информации транзитом. При десятичном умножении с входа 22 на управляющий вход задания режима коррек1481748

20

30

40

55 тора 29 подается потенциал логической единицы, что обеспечивает коррекцию «-6» в случае отсутствия выходного переноса сумматора 28. Значение же выходного переноса сумматора 28, равное логической единице, поступая на вход запрета коррекции корректора 29, обеспечивает передачу через него информации без изменения.

Самый старший 2i и самый младший

2. блоки суммирования первой группы построены точно так же, как и описанные выше блоки 2> — 2, причем с входа 12 устройства в блок 2i при двоичном умножении, чисел в дополнительных кодах может вводиться коррекция либо подсуммироваться в процессе умножения двух чисел третье число к получающемуся произведению.

Блоки 3i — Э.+! суммирования второи группы предназначены для предварительного суммирования старших и младших частей произведений, вырабатываемых блоками l i — 1.. умножения.

На первый вход сумматора 32 блока Зр суммирования второй группы подается содержимое p-ro буферного регистра 5 первой группы, а на второй вход — значение содержимого (р — 1) -го буферного регистра 6 второй группы. После выполнения очередного такта..значение результата суммирования на сумматоре 32 запоминается в буферном регистре 7р третьей группы, а значение выходного переноса сумматора 32— в триггере 34.

При выполнении в устройстве двоичного. умножения корректор 33 настраивается потенциалом логического нуля с входа

22 на передачу информации транзитом.

При десятичном умножении с входа 22 на управляющий вход корректора 33 поступает потенциал логической единицы, что обеспечивает коррекцию «+6» при наличии единичного значения выходного переноса сумматора 32. В отсутствие переноса из сумматора 32 информация через корректор 33 передается без изменения.

Самый старший 3i и самый младший

3. i блоки суммирования второй группы построены так же, как и блоки 3 — 3, но подключены они в устройстве несколько иначе. Если при десятичном умножении старшие тетрады произведений на выходах блоков l i — 1.. умножения формируются уже скорректированными на «+6», то на вход 13 первой константы устройства подается код 0000, а на вход 14 второй константы — код 0110. Если же младшие тетрады произведений на выходах блоков 1! — l. умножения формируются уже скорректированными на «+6», то на вход 13 первой константы подается код 0110, а на вход 14 второй константы — код 0000.

При двоичном умножении на оба входа 13 и 14 подается код 0000.

Устройство работает следу!о (и: .; (Ибр;:.:;0. ; (фиг. 4 и 5).

По сигналу У19 происходит обнуление регистров 7i — 7.. +i, 8i — 8:+I и триггеров 30 и 34 блоков суммирования, сигнал У20 разрешает запись Но синхроимпульсу информации в регистры 5i — 5, 6i — 6., 7i — 7.. +I, 8i — 8. i, а также в триггеры 30 и 34 блоков суммирования, сигнал У22 ооеспечивает функционирование блоков 1! — !. умножения в десятичной системе счислениH и настройку корректоров 29 и 33 блоков суммирования на режим коррекции, ilo сигналу У23 мультиплексора 31 блоки сум!!ирования первой группы настраиваются на передачу информации с их вторых входов, на которые поступают значения выходных переносов из сумматоров 28 соседних более младших блоков ". ììI;.poI;àHIIÿ:I««IHI I группы.

Рассмотрим выполнение . Иои-!!!ol жения (фиг. 4). Перед H ÷ «loì 0 !«рации на входах 1;!, .станавл:I HI0(с.! значения множимого. на входе 10 множителя устройства уста пав.! ивлстся 3!! (! !«!II! « самой младшей тетрады множителя.

В первом такте двои;ного ум Hoх,:i!! IH в блоках 1 — 1., а",!ая младш .я тстав;!да множителя перемножается íà с !0;— ветствующие тетрадь м нож и мого.. 1вои I I I:. резул ьтаты этих тстраднь!х ум нож«н:! й;! «и;:— сываются в буфер.—.ые регистры 5, -5. и 6! — 6 по сиги !л разрешен!!:;! i У20.

Одновременно прои«ходя« обнулс..;,:.с регистров 7! — !>.,!, 8! — -8w, и триг.ср >в 30 и 34 блоков суммирования (с!!: !:а.; У i 9) . а также подача на вход 10 у(т;.0ист!!:следующей тетрады vi::ожителя.

Во втором такте T.",I |I 0H(«:!i! H . .;.;«и, х<(дят перемножение очеред!!ой второ, !1; с!рады множителя на тст; «дь: м!гожимого одновременно с этим предварит«. !и!О с, м. !!— рование предыдущих тетрадных иронззсдсний в блоках 3i — 3, суммирования второй группы. В конце второго такта с разрешения сигнала У20 в регистрах 5i---5, 6! — 6н, 7i — 7н+, 8! — 8 „, и триггерах 30 и 34 блоков суммирования фиксируется промежуточная информация. а на вхо!« lii множителя устройства появляется з!!ачени(следующей (третьей) тетрады множителя.

Аналогичным образом устройство фу!!:ционируеT и В других т(!ктах. В каждо такте с выхода 17 устройства. начиная с четвертого такта, считывается значение очередной тетрады младшей части результата.

После выполнения последнего м-го такта собственно умножения в буферных регистрах 5! — 5„и 6! — 6 запоминаются знaчения тетрадных произведений последней (самой старшей) тетрады множителя на все тетрады множимого.

При выполнении (м+1) -го такта происходит предварительное суммирование значений содержимого буферных регистров 5! 5н

1481748

tS

30

50

Формула изобретения и 6 — 6 в блоках 3i — 3„„ суммирования второй группы, а также суммирование содержимого регистров 8i — 8„„и 7i — 7 в блоках 2 — 2„+, суммирования первой группы. С входа 10 множителя устройства при этом на все входы множителя блоков l i — l„умножения подается нулевая тетрада. В конце такта образуемые на выходах блоков 11 — l„нулевые произведения запоминаются в буферных регистрах 5 — 5„ и 61 — 6„, а в регистрах 7i — 7„+, и 8> — 8„+,— некоторая промежуточная информация.

После выполнения (м+2)-ro и (м+3)-го тактов завершается вывод информации из блоков 3i — Зм+ и буферных регистров 7>—

7м.

При выполнении (м+4)-го такта сигнал

У23 настраивает мультиплексоры 31 блоков

21 — 2„ суммирования первой группы на передачу информации через их вторые входы, тем самым выходы переноса сумматоров 28 оказываются соединенными с входами переноса сумматоров 28 соседних старших блоков суммирования первой группы. В результате этого значения содержимого триггеров 30 подсуммируются к сумме содержимых соответствующих регистров

7 — 7 ., и 8 — 8ч,„и двухрядный код произведения преобразуется к однорядному.

Поскольку при приведении двухрядного кода к однорядному перенос распространяется через все блоки 21 — 2 +, суммирования, то длительности одного такта работы устройства не хватает для завершения такого приведения. Поэтому сигнал

У23 поддерживается в течение двух (как это предполагается на фиг. 4 и 5) или более тактов.

После выполнения (м+4) -го и (м+5) -ro тактов в регистрах 8i — 8„„произведения будет находиться старшая часть окончательного произведения в однорядном коде.

Младшая же часть произведения уже введена через выход 17 устройства во время выполнения предыдущйх тактов.

Десятичное умножение выполняется в основном аналогично двоичному. На фиг. 5 приведена диаграмма выполнения десятичного умножения в предположении, что количество десятичных разрядов в операндах равно м. Отличие от двоичного умножения состоит в том, что в тактах с первого по (м+5)-й присутствует дополнительный сигнал У22, который настраивает блоки li — 1„ на умножение в десятичной системе счисления, а корректоры 29 и 33 блоков суммирования — на режим коррекциии.

1. Устройство для ум ножения чисел, содержащее группу блоков умножения, две группы блоков суммирования, группу регистров произведения и три группы буферных регистров, причем вход множителя устройства соединен с входами множителя блоков умножения группы, входы множимого которых соединены с соответствующими входами цифр множимого группы устройства, вход задания режима которого соединен с входами задания режима блоков умножения группы, с входами задания режима блоков суммирования первой и второй групп, выходы старших и младших частей произведений блоков умножения группы соединены с информационными входами соответствующих буферных регистров первой и второй групп, выходы буферных регистров первой группы соединены с первыми информационными входами соответствующих блоков суммирования второй группы, выход

Р-ro (Р= 1 — М, M=n 4, и. — разрядность сомножителей) буферного регистра второй группы соединен с вторым информационным входом (Р+1)-го блока суммирования второй группы, выходы блоков суммирования второй группы соединены с информационными входами соответствующих буферных регистров третьей группы, входы установки в «О» которых соединены с входом начальной установки устройства, выходы суммы блоков суммирования первой группы соединены с информационными входами соответствующих регистров произведения группы, выход Р-го регистра произведения группы соединен с первым информационным входом (Р+1)-ro блока суммирования первой группы и является выходом Р-й цифры старшей части произведения устройства, выход младшей части произведения которого соединен с выходом (М+1) -го регистра произведения группы, вход начальной установки устройства соединен с входами установки в «О» регистров произведения группы, входы разрешения приема которых объединены с входами разрешения приема буферных регистров первой, второй и третьей групп и соединены с первым тактовым входом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, входы первой и второй констант устройства соединены соответственно с вторым информационным входом первого и с первым информационным входом (М+1) -го блоков суммирования второй группы, вход значения коррекции устройства соединен с первым информационным входом первого блока суммирования первой группы, выходы буферных регистров третьей группь1 соединены с вторыми информационными входами соответствующих блоков суммирования первой группы, входы сброса которых объединены с входами сброса блоков суммирования второй группы и соединены с входом начальной установки устройства, первый и второй тактовые входы которого соединены соответственно с первыми и вторыми тактовыми входами блоков суммирования первой груп1481748

10 пы, тактовые входы -блоков суммирования второй группы соединены с первым тактовым входом устройства, вход переноса.

P-ro блока суммирования первой группы соединен с выходом переноса (Р+ 1)-го 5 блока суммирования первой группы, вход переноса (Я+1) -го блока суммирования первой группы соединен с входом логического нуля устройства.

2. Устройство по п. 1, отличающееся тем, что блок суммирования первой группы содержит сумматор, корректор, триггер и мультиплексор, причем .выход суммы сумматора соединен с информационным входом корректора, вход запрета которого соединен с выходом переноса сумматора и с ин- 15 формационным входом триггера, выход корректора и выход переноса сумматора являются соответственно выходом суммы и выходом переноса блока суммирования первой группы, вход задания режима, первый и второй тактовые входы и вход сброса которого соединены соответственно с входом задания режима корректора, входом разрешения приема триггера, управляющим входом мультиплексора и входом установки в «О» триггера, первый информационный g5 вход блока суммирования первой группы соединен с входом первого слагаемого сумматора, входы разрядов второго слагаемого которого соединены соответственно с входами разрядов, кроме младшего, второго информационного входа блока суммирования первой группы и с выходом триггера, вход младшего разряда второго информационного входа и вход переноса блока суммирования первой группы соединены соответственно с первым и вторым информационными входами мультиплексора, выход которого соединен с входом переноса сумматора.

3. Устройство по п. 1, отличающееся тем, что блок суммирования второй группы содержит сумматор, корректор и триггер, причем первый и второй информационные входы, вход сброса, тактовый вход и вход задания режима блока суммирования второй группы соединены соответственно с входами первого и второго слагаемых сумматора, входом установки «О» н входом разрешения приема триггера, с входом задания режима корректора, выход которого является выходом блока суммирования второй группы, выход суммы сумматора соединен с информационным входом корректора, вход разрешения которого соединен с выходом переноса сумматора и с информационным входом триггера, выход которого соединен с входом переноса сумматора.

1481748

Составитель А. Клюев

Редактор Л. Гратилло Техред И. Верес Корректор А. Обручар

Заказ 2690/49 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Г1атент», г. Ужгород, ул. Гагарина, 101