Цифровой накопитель с дробной переменной емкостью

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной и вычислительной технике и может быть использовано для суммирования импульсных последовательностей в цифровых синтезаторах частот с любым дискретом изменения выходной синтезируемой частоты. Цель изобретения - повышение быстродействия и упрощение цифрового накопителя. Цифровой накопитель содержит мультиплексоры 1 и 11, сумматоры 2 и 12, регистры 3-5, управляемый делитель частоты 13, вход 6 кода, вход 7 управления целочисленной величиной изменения емкости, вход 14 управления дробной величиной изменения емкости, выходы 8 и 9, тактовый вход 10, вход 15 управления коэффициентом деления частоты. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК!

511 4 G 06 F 7/68

Q,".-„, Б. ь;„!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

llO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4308094/24-24 (22) 21.09.87 (46) 23.05.89. Бюл. № 19 (72) А. Б. Сучкова и В. С. Станков (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1162040, кл. Н 03 К 23/66, 1985.

Авторское свидетельство СССР № 1374426, кл. Н 03 К 23/66, 1986, (54) ЦИФРОВОЙ НАКОПИТЕЛЬ С ДРОБНОЙ ПЕРЕМЕННОЙ ЕМКОСТЬЮ (57) Изобретение относится к измерительной и вычислительной технике и может быть использовано для суммирования имИзобретение относится к области измерительной и вычислительной техники и может быть использовано для суммирования импульсных последовательностей в цифровых синтезаторах частот с любым дискретом изменения выходной синтезируемой частоты.

Цель изобретения — повышение быстродействия и упрощение цифрового накопителя.

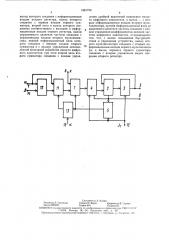

На чертеже представлена функциональная схема цифрового накопителя с дробной переменной емкостью.

Цифровой накопитель содержит мультиплексор 1, сумматор 2, регистры 3 — 5, вход 6 кода (К), вход 7 управления целочисленной величиной изменения емкости накопителя (М), выходы 8 и 9, тактовый вход 10, мультиплексор 11, сумматор

l2, управляемый делитель 13 частоты, вход 14 управления дробной величиной изменения емкости (I!), вход 15 управления коэффициентом деления частоты.

Первый информационный вход мультиплексора 1 является входом 6 кода (К) „,Я0„„1481756 А 1 пульсных последовательностей р, цифровых синтезаторах частот с любым дискретом изменения выходной синтезируемой частоты.

Цель изобретения — повьш1ение б ыстродействия и упрощение цифров:го накопителя.

Цифровой накопитель содержит мультиплексоры 1 и 11, сумматоры 2 и 12, регистры 3 — 5, управляемый делитель частоты 13, вход 6 код-, вход 7 управления целочисленной величиной изменения емкости, вход 14 управления дробной величиной изменения емкости, выходы 8 и 9, тактовый вход 10, вход !5 управления коэффициентом деления частоты. ил. цифрового накопителя, выходами 8 и 9 которого являются соответственно выход переноса сумматора 2 и выход регистра 3, тактовый вход которого соединен тактовым входом 10 цифрового накопителя (тактовая частота f.). Второй информационный вход мультиплексора 1 соединен с выходом мультиплексора l l, а выход мультиплексора 1 соединен с входом регистра 4, выход которого соединен с вторым входом сумма-. тора 2, первый вход и выход которого соединены соответственно с выходом и входом регистра 3.

Вход регистра 5 соединен с выходом переноса сумматора 2 и входом управления регистра 4, выход регистра 5 соединен с управляющим входом мультиплексора 1 и входом управляемого делителя 13 частоты, выход которого соединен с входом управления мультиплексора 11. Информационные входы мультиплексора 11 соединены соответственно с первым входом сумматора 12 и выходом суммы сумматора 12, первый вход которого соединен с входом 7 управления целочисленной величиной изменения емкости

1481756 накопителя (М), а второй — подключен к входу 14 управления дробной величиной изменения емкости накопителя (P). Тактовые входы регистров 3 — 5 объединены и подключены к тактовому входу 10 накопителя (t .). Накопитель работает следующим образом. Сумматор 12 суммирует код М, поступающий с входа 7, с кодом р, поступающим с входа 14, в результате чего на выходе сумматора 12 формируется код суммы M+(. Таким образом, на первый информационный вход мультиплексора 11 непрерывно поступает код М, а на второй информационный вход †к М+ . Если сигнал, поступающий с выхода управляемого делителя !3 частоты на управляющий вход мультиплексора 11, равен нулю, то на второй информационный вход мультиплексора 1 будет поступает код М. Пока сигнал переноса сумматора 2 равен нулю, на выход мультиплексора 1 будет проходить код К с первого информационного входа мультиплексора 1, этот код по тактовым импульсам записывается в регистр 4, который при нулевом значении переноса с сумматора 2 работает в режиме записи и хранения информации. Код К в сумматоре 2 складывается с выходным кодом регистра 3, код суммы подается на вход регистра 3 и следующим тактовым импульсом записывается в регистр 3.

Когда в одном из тактов работы, накопитель переполняется, т. е. значение суммы на выходе сумматора 2 достигнет или превысит величину емкости накопителя, в сумматоре 2 образуется остаток L, а на выходе 8 — сигнал переноса, равный логической единице. Этот сигнал поступает нг вход управления видом операции регистра 4 и переводит его в режим сдвига.

В следующий такт работы накопителя регистр 4 сдвигает выходную информацию— код К на один двоичный разряд в сторону старших разрядов, что равносильно операции умножения кода К на два. Таким образом на вход сумматора 2 в этот такт работы накопителя будет проходить код, соответствующий 2К.

Этим же тактовым импульсом в регистр

3 записывается остаток сумматора 2, в регистр 5 — единица переноса, на выход мультиплексора 1 пройдет код М с второго информационного входа, на выходе сумматора 2 получается код суммы 2K+L, сигнал переноса на выходе 8 становится равным логическому нулю, который поступает на вход управления видом операции регистра 4 и переводит его в режим записи и хранения.

В следующий такт работы накопителя в регистр 5 записывается нуль с выхода переноса сумматора 2, в регистр 4 — код

М, в регистр 3 — код 2К+Е„на выход мультиплексора 1 вновь поступает код К с первого информационного входа, на выходе сумматора 2 получается код суммы

2K+M+L и начинается новый цикл работы накопителя, в котором емкость будет равна Я вЂ” М.

Сигнал с выхода регистра 5 поступает на вход управляемого делителя 13, который вырабатывает импульс, по длительности равный периоду следования выходных импульсов переполнения накопителя, и с частотой, определяемой коэффициентом деления а, задаваемым программно к входу 15.

Таким образом на выход мультиплексора

1! пропускается код М+р только в моменты времени, определяемые коэффициентом деления управляемого делителя 14, т. е. один раз за а циклов работы накопителя. В результата чего в (а в 1) циклах работы накопителя его емкость равна

g — М, а в одном цикле R — М вЂ” P. Среднее значение емкости накопителя за а циклов равно (R — М)(а — I )+ (R — М вЂ” р)

R,— — М вЂ” —.

Из этого выражения следует, что изменяя значения кода Р и коэффициент деления а управляемого делителя 13 частоты, можно получить любую дискрету изменения емкости накопителя.

Для обеспечения работоспособности данного цифрового накопителя с дробной переменной емкостью необходи.ло выполнение следующих условий:

30 тр, + Ъ* т, +т„„(Tr,, тр, +твв.i (To, т13+тщ 1 +тв (Твыв, где т „т„,.т, — время задержки записи регистров 3 — 5 соответствен35 но; т,, т, — время задержки сумматора

2, сумматора,2 до выхода переноса соответственно; т„, т„„— время задержки мультиплексоров 1 и 11.

4Q

Формула изобретения

Цифровой накопитель с дробной пере4 менной емкостью. содержащий первый и второй сумматоры, первый и второй мультиплексоры, первый, второй и третий регистры и управляемый делитель частоты, перзый информационный вход первого мультиплексора соединен с входом кода цифрового накопителя, первый и второй выходы устройства соединены соответственно с выходами переноса первого сумматора и первого регистра, тактовый вход которого соединен с тактовым входом цифрового накопителя и тактовыми входами второго и третьего

55 регистров, информационный вход третьего регистра соединен с выходом переноса первого сумматора, а выход — с тактовым входом управляемого делителя частоты и с управляющим входом первого мультиплексора, 1481756

Составитель А. Клюев

Редактор Л. Гратилло Техред И. Верес Корректор В. Гирняк

За к аз 2690/49 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1! 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101 выход которого соединен с информационным входом второго регистра, выход которого соединен с. первым входом первого сумматора, второй вход и выход которого соединены соответственно с выходом и информационным входом первого регистра, выход управляемого делителя частоты соединен с управляющим входом второго мультиплексора, первый информационный вход которого соединен с первым входом второго сумматора и с входом управления целочисленной величиной изменения емкости цифрового накопителя, при этом второй вход второго сумматора соединен с входом управления дробной величиной изменения емкости цифрового накопителя, а выход — с вторым информационным входом второго мультиплексора, причем информационный вход уп равляемого делителя частоты соединен с входом управления коэффициентом деления частоты цифрового накопителя, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, выход второго мультиплексора соединен с вторым информационным входом первого мультиплексора, а выход переноса первого сумматора соединен с входом управления видом операции второго регистра.