Устройство выборки команд процессора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для выборки команд длиной в слово и полуслово при построении процессора специализированной ЭВМ. ЦЕЛЬЮ ИЗОБРЕТЕНИЯ ЯВЛЯЕТСЯ СОКРАЩЕНИЕ ОБЪЕМА ОБОРУДОВАНИЯ. УСТРОЙСТВО ВЫБОРКИ КОМАНД ПРОЦЕССОРА СОДЕРЖИТ ВХОД 1 КОМАНДНОГО СЛОВА, ВХОД 2 ЗАПУСКА, ПЕРВЫЙ 3 И ВТОРОЙ 4 РЕГИСТРЫ, КОММУТАТОР 5, ДЕШИФРАТОР 6, ЭЛЕМЕНТ И7, СЧЕТЧИК 8, БЛОК 9 МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, ВЫХОД 10 КОМАНДЫ, ВЫХОД 11 АДРЕСА СЛЕДУЮЩЕГО КОМАНДНОГО СЛОВА. 4 ИЛ.

СОЮЗ СОВЕТСКИХ

СОЦИА>1ИСТИЧЕСКИХ

РЕСПУБЛИК (5у 4 G 06 F 9 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬПИЯМ

ПРИ ГКНТ СССР (21) 4311016/24-24 (22) 28.09.87 (46) 23.05.89. Бюл. № 19 (72) С. A. Орлов, A. С. Поляков, Г. Ф. Некрасов и A. С. Сазонов (53) 681.325 (088.8) (56) Авторское свидетельство СССР

¹ 610109, кл. G 06 F 9/00, 1976.

Авторское свидетельство СССР

¹ 1410028, кл. Ci 06 F 9/00, 1986. (54) УСТРОЙСТВО ВЫБОРКИ КОМАНД

ПРОЦЕССОРА (57) Изобретение относится к вычисли„„SU„„1481758 A 1

2 тельной технике и может быть использовано для выборки команд длиной в слово и полуслово при построении процессора специализированной 3ВМ. Целью изобретения является сокращение объема оборудования. Устройство выборки команд процессора содержит вход 1 командного слова, вход 2 запуска, первый 3 и второй 4 регистры, коммутатор 5, дешифратор 6, элемент И 7, счетчик 8, блок 9 микропрограммного управления, выход 10 команды, выход 11 адреса следующего командного слова. 4 ил.

1481758

Формат команды

Любой

RR

10

Изобретение относится к вычислительной технике и может быть использовано для выборки команд длиной в слово и полуслово при построении процессора специализированных ЭВМ среднего быстродействия.

Цель изобретения — сокращение объема оборудования.

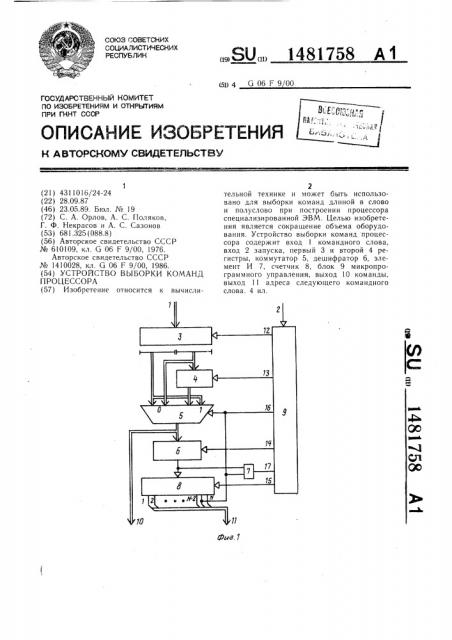

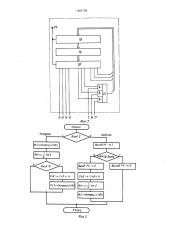

На фиг. 1 представлена структурная схема устройства выборки команд процессора; на фиг. 2 — структурная схема блока микропрограммного управления; на фиг. 3 — граф-схема микропрограммы функционирования устройства; на фиг. 4— временные диаграммы работы устройства.

Устройство выборки команд процессора (фиг. 1) содержит вход 1 командного слова и вход 2 запуска устройства, первый 3 и второй 4 регистры, коммутатор 5, дешифратор 6, элемент И 7, счетчик 8, блок 9 микропрограммного управлсния, выход 10 команды и выход 11 адреса следующего командного слова устройства, выходы

12 — 15 и входы 16 и 17 блока 9 микропрограммного управления.

Блок 9 микропрограммного управления (фиг. 2) содержит регистр адреса микрокоманды 18, память микропрограмм 19, регистр микрокоманды 20, элемент 2И—

ЗИЛИ 21, тактовый вход 22.

В описании использованы следующие обозначения, принятые в системе команд

3BN: RR — формат команды длиной в полуслово (2 байта); RX — - формат команды длиной в слово (4 байта); адрес памяти

N — разрядный.

Принцип действия устройства основан на организации конвейерной выборки командных слов. Запуск конвейера производится в случае начальной загрузки адреса команды в счетчик 8 по сигналу на входе 2 устройства. При этом производится загрузка конвейера. В дальнейшем конвейер работает по выборке командных слов (фиг. 3).

Регистры 3 и 4 организованы так, что содержат f10 крайней мере одну команду.

Выборка командной информации из памяти осуществляется словами с использованием счетчика 8, при этом - с выхода

11 устройства на вход памяти поступает укороченный адрес — адрес слова, в котором обязательно содержится либо левое полуслово команды, либо вся команда.

Начальное значение счетчик 8 получает при загрузке адреса первой команды. В дальнейшем, если в регистрах 3 и 4 не содержится полностью очередной команды, то по сигналу с блока 9 микропрограммного управления, поступающего на первый счетный вход счетчика 8, его значение увеличивается на +4. (N — !)-й разряд счетчика 8 фиксирует факт расположения очередной команды на границе слова или полуслова. В первом случае (N — !)-й разряд счетчика 8 прини15

55 мает нулевое значение, во втором — единичное. Начальное значение (М вЂ” 1)-й разряд получает при загрузке в счетчик 8 адреса первой команды. В процессе работы конвейера дешифратором 6, выход которого управляется сигналом 14 с блока 9, анализируется длина текущей исполняемой команды. Таблица истинности дешифратора

6 имеет вид:

Управляющий Выход вход 14

0 0

1 1

1 0

Если длина текущей исполяемой команды равна полуслову (формат RR), то значение (N — 1)-го разряда счетчика 8 инвертируется после снятия единичного сигнала управления дешифратором 6 по спаду импульса на втором счетном входе счетчика

8. Если текущая команда имеет длину в слово (формат RX), то значение (N — -! )-го разряда счетчика 8 не изменяется.

Сигнал с (Х вЂ” 1) -го выхода счетчика 8 управляет работой коммутатора 5, который подключает к выходу 10 устройства командное слово из первого 3 и второго 4 регистров, начало которого всегда совпадает с началом текущей исполняемой команды.

При нулевом значении сигнала на своем управляющем входе коммутатор 5 подключает выходы левой и правой половин первого регистра 3, по единичному значению— выходы второго регистра 4 и левой половины первого регистра 3. Код операции команды с выхода коммутатора 5 поступает на вход дешифратора 6.

Работу устройства рассмотрим на примере выборки командной информации при обработке некоторой последовательности команд РХ, RR, RX, расположенной в памяти начиная с адреса с единичным значением (N — 1) -го разряда.

На этапе заполнения конвейера в счетчик 8 загружается адрес первой команды, а на вход 2 устройства поступает сигнал на запуск конвейера, и блок 9 микропрограммного управления вырабатывает последовательность управляющих сигналов для заполнения конвейера (фиг. 4): с выхода

12 блока 9 .подается сигнал на загрузку первого регистра 3, командным словом из памяти (слово загружается из ячейки, адрес которой определяется кодом на выходе 11 устройства); с выхода 13 блока 9 подается сигнал на загрузку во второй регистр 4 правого полуслова из первого регистра 3.

В блоке 9 микропрограммного управления производится анализ содержимого (N — 1) -го разряда счетчика 8, поступающего на его вход 16. По единичному значению данного разряда с выхода 15 блока

9 подается управляющий сигнал на первый

1481758 счетный вход счет, ика 8 для увеличения его значения на +4. Новое значение адреса используется для выборки из памяти второго командного слова, которое загружается в первый регистр 3 по сигналу с выхода 12 блока 9. При нулевом значения (N — 1)-го разряда счетчика 8 второе обращение к памяти и заполнение регистра 3 не производится.

На этом этап заполнения конвейера заканчивается. При этом единичный сигнал с (N-1)-го выхода счетчика 8 подается на управляющий вход коммутатора 5, который подключает к выходу 10 устройства первую команду RX для дальнейшей обработки.

Сигнал с выхода 14 блока 9 микропрограммного управления разрешает выход дешифратора 6, значение сигнала на котором остается нулевым — признак команды

RX. При этом ч ачение (N — 1) -ro разряда счетчика 8 в этом цикле не изменится.

На выходе элемента И 7 появляется сигнал с нулевым значением, по которому блок 9 вырабатывает сигналы, вызывающие выборку очередного командного слова из памяти (фиг. 4): по сигналу с выхода

15 блока 9 значение счетчика 8 увеличивается на +4; по сигналу с выхода 13 блока 9 в регистр 4 загружается правое полуслово из регистра 3; по сигналу с выхода 12 блока 9 в регистр 3 загружается очередное кома ндное слово, которое выбирается из памяти по новому адресу.

Коммутатор 5 подключает на выход 10 устройства вторую команду RR.

Сигнал с выхода 14 блока 9 разрешает выход дешифратора 6, значение сигнала на котором изменяется на единичное — признак команды RR.

На выходе элемента И 7 появляется сигнал с единичным значением, по которому блок 9 запрещает выборку очередного командного слова из памяти. По спаду сигнала на выходе дешифратора 6 значение (М вЂ” I ) -r o разряда счетчика 8 инвертируется и сигнал с нулевым значением поступает на управляюьций вход коммутатора 5, который подключает к выходу 10 устройства третью команду RX, расположенную в первом регистре 3.

Формула изобретения

Устройство выборки команд процессора, содержащее первый и второй регистры, коммутатор, дешифратор, элемент И, счетчик, блок микропрограммного управления, вход первого разряда кода условий которого соединен с входом запуска устройства, вход командного слова устройства соединен с информационным входом первого регистра, выход поля младших разрядов которого соединен с первыми входами первой и второй групп информационных входов коммутатора, второй вход второй группы информационных входов которого соединен с выходом второго регистра, информационный вход которого соединен с выходом поля старших разрядов первого регистра и с вторым входом первой группы информационных входов коммутатора, выход которого соединен с информационным входом дешифратора и с выходом команды устройства, выход адреса команды которого соединен с выходом счетчика, первый счетный вход которого соединен с первым выходом блока микропрограммного управления, второй и третий выходы которого соединены соответственно с синхровходами

gp первого и второго регистров, выход дешифратора соединен с первым входом элемента И, выход которого соединен с входом второго разряда кода условий блока микропрограммного управления, отличающееся тем, что, с целью сокращения объема оборудования, выход первого разряда счетчика соединен с вторым входом элемента

И, с управляющим входом коммутатора и с входом третьего разряда кода условий блока микропрограммного управления, выход дешифратора соединен с вторым

40 счет ым входом счетчика, четверть1й вь од блока микропрограммного управления соединен со стробирующим входом дешифратора.

1481758

2 1б!7

Фиг. Я

1481758

76

7Z

Выход деы б иг.

Составитель A. Афанасьев

Редактор С. Г1 атру ше ва Техредй. Верес Корректор М. Васильева

Заказ 2691/50 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям прп ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101