Устройство для адресации блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и ,в частности, к устройствам управления основной памятью. Целью изобретения является расширение области применения устройства за счет индицирования полной занятости внешними заявками включенных блоков. Устройство для адресации блоков памяти содержит N переключателей 1 и элементов И 2, первый дешифратор 3, три элемента И-НЕ 4-6, элемент N -ИЛИ 7, инвертор 8, счетчик стека 9, три блока памяти адресов 10-12, второй дешифратор 13 и триггер 14. 2 ил.

СО 03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5ц 4 G 06 F 12/02

8Е. (21) 4321078/24-24 (22) 26. 10.87

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМ

ПРИ ГКНТ СССР (46) 23.05.89. Бюл. № 19 (71) Львовский политехнический институт им. Ленинского комсомола (72) Г1. А. Кондратов, О. К. Мешков и И. Б. Боженко (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 1024926, кл. G 06 F 12/02,,1980.

Авторское свидетельство СССР № 11 98565, кл. G 11 С 8/00, 1985.

„,Я0„„1481777 А 1

2 (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ

БЛОКОВ ПАМЯТИ (57) Изобретение относится к вычислительной технике и, в частности, к устройствам управления основной памятью. Целью изобретения является расширение области применения устройства за счет индицирования полной занятости внешними заявками включенных блоков. Устройство для адресации блоков памяти содержит N переключателей 1 и э„цементов И 2, первый дешифратор 3, три элемента И вЂ” НЕ 4 — 6, элемент N — ИЛИ 7, инвертор 8, счетчик стека

9, три блока памяти адресов 10 — 12, второй дешифратор 13 и триггер 14 2 ил, 1481777

Изобретение относится к вычислительной технике, в частности к устройствам управления основной памяти.

Цель изобретения — расширение функциональных возможностей и области его применения за счет индицирования полной занятости внешними заявками включенных блоков памяти.

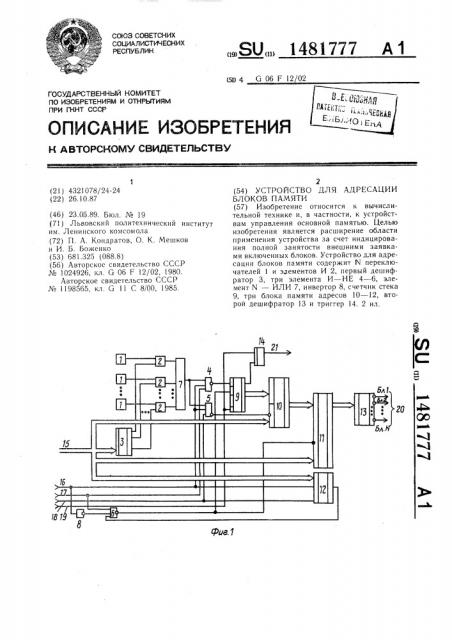

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 — его временные диаграмы.

Устройство содержит (фиг. 1) группу переключателей 1 и элементов И 2, первый дешифратор 3, элементы И вЂ” HE 4-6 и N—

ИЛИ 7, инвертор 8, счетчик стека 9, блоки 10-12 памяти адресов второй дешифратор 13, триггер 14, адресный 15 и задания режима начальной установки 16 входы, синхровходы 17 и 18, вход 19 сброса, выход 20 устройства для возбуждения адресуемого блока памяти и выход 21 устройства для индицирования полной занятости блоков памяти. ь{исло N соответствует количеству адресуемых блоков памяти.

На фиг. 2 обозначены: а — адреса выбираемых блоков памяти; б — сигнал на управляющем входе 16 устройства; в сигнал на первом синхровходе 17 устройства; r — сигнал на втором синхровходе 18 устройства; д — сигнал на входе 19 сброса; е — сигнал записи в первый блок 10 памяти адресов; ж — сигнал записи во второй блок 11 памяти адресов; з — выход третьего блока 12 памяти адресов; и выход обратного переноса счетчика 9 стека; к — выход триггера 14.

Дополнительно на фиг. 2 обозначены участки — 1, II начальной установки устройства, 111 — V — адресации.

Устройство работает следующим образом.

Первой из поступающих с определенным адресом заявок предоставляется первый из неотключенных и незанятых заявками с иным адресом блоков памяти. Совокупность блоков памяти, подлежащих распределению, задается установкой в соответствующее положение переключателей 1 («О» — блок отключен, «1» — включен) .

Уровнем «1» на управляющем входе 16 устройства задается режим начальной установки. Работа в этом режиме (фиг. 2б, участки 1, 11) начинается с поступления в уст-. ройство по его входу 19 сигнала сброса, по которому сбрасывается триггер 14, а счетчик 9 стека устанавливается в единичное состояние. Затем в устройство по адресному входу 15 поступают последовательно инкрементируемые адреса всех имеющихся в наличии блоков памяти, начиная с адреса «О» и кончая адресом «N — 1» (фиг. 2а, участки 1, 11). Адреса сопровождаются стробами по первому 17 (фиг. 2в) и второму 19 (фиг. 2г) синхровходам устройства.

1О !

4S

Пусть блок памяти + включен (! — â€”вЂ”

=- 1,N) — на выходе -, I-го переключателя I уровень «1». 1 îãäà при поступлении на вход 15 соответствующего этому блоку адреса i (фиг. 2а, участок 1) уровень «1», поступающий с i+1-го переключателя на первый вход i=1-го элемента И 2, и уровень «!», поступающий с выхода i дешифратора 3 на второй вход i+3 го элемента И 2, создадут на

его выходе уровень «1», который через элемент М вЂ” ИЛИ 7 поступит на первые входы элементов И вЂ” НЕ 4 и 5. При этом по первому стробу выработается сигнал инкремента счетчика 9 (фиг. 2д), и он из состояния ii+i переключится к состояние .

По второму стробу по этому адресу i в первый блок 10 памяти адресов запишется. (фиг. 2е, участок !) адрес i включенного блока памяти i+I, а в третий блок !2 памяти адресов — уровень «l» (фиг. 2з, участок I): Запись во второй блок 11 памяти адресов в режиме начальной установки блокируется уровнем «О» на выходе инвертора 8.

Пусть блок 1+1 выключен (j = — i, V) .

Тогда при поступлении соответствующего ему адреса j (фиг. 2а, участок II) на вход 16 уровень «О» на переключателе j+i заблокирует прохождение стробов на инкерментацию счетчика 9 и запись в блок 10 (фиг. 2г, е, участок 11). Осуществится только запись

«1» по адресу j в блок 12 (фиг. 2з, участок II). Соответственно при поступлении адреса 1+1, если, например, блок памяти

j+2 включен, в блок 10 этот адрес будет записан по адресу j.

В итоге по окончании начальной установки в счетчике 9 выставится значение, соответствующее числу включенных блоков, в блоке 10 будут хранится упорядоченные по возрастанию физические номера этих блоков, а во всех ячейках блока 12 установится значение «1», указывающее на незанятость подлежащих адресации блоков.

Режим адресации задается сбросом управляющего сигнала на входе 16 в «О» (фиг. 2б, участок 111).

Пусть первое из обращений происходит по адресу К (фиг. 2а, участок- 111), причем О(((log>A где N число адресуемых блоков. При совпадении уровней «1» на выходе блока 12 и инвертора 8 с поступлением с входа 17 первого строба третий элемент И вЂ” НЕ формирует сигнал (фиг. 2ж, участок 111) записи во второй блок 11 памяти по адресу К номера свободного блока из вершины стека блока 10 памяти адресов, а затем декрементирует счетчик 9.

По второму стробу с входа 18 в блоке 12 по адресу К записывается уровень «О» признак занятости блока (фиг. 2з, участок 111). Перезаписанный из блока 10 в блок 11 адрес поступает на вход дешифратора 13. Соответствующий выход этого

1481777 дешифратора через выход 20 устройства возбуждает адресуемый блок памяти.

При следуюгцем обращении к этому же блоку (фиг. 2а, участок IV) уровень «(Ь на выходе блока 12 блокирует запись в блок 11 и декремент счетчика 9 (фиг. 2ж, з, участок 1V). Соответственно из блока 11 по адресу К считывается ранее Определенный по стеку физический адрес выбираемого блока, и дешифратор 13 возбуждает по нему. Требующийст? выход 20.

Если в стеке остается единственный номер свободного блока, значение счетчика 9 стека равно «О». Поступление адреса 1 (фиг. 2а, участок V), до этого егце не поступавшего в устройство, приводит по первому стробу к гоявлению сигнала переноса на выходе счетчика (фиг. 2и).

Сигнал переноса поступает на синхровход трипера 14 и ycravaBливает его в «1» (фиг.2К). С триггера 14 на выход 21 управления устройства поступает сигнал «стек исчерпан,» воспре?цаю?ций дальнейшую адресацию незанятых блоков.

Таким образом, в первом блоке 10 памяти адресов размещаются упорядоченные по возрастанию физические номера включенных блоков пам11.й, во втором блоке 11 памяти устанавливается соответствие между логическими (внешними) и физическими адресами, г, третьем блоке 12 фиксируется занятость адресуемых блоков памяти, а первой из поступающих заявок с определенным адресом представляется первый из включенных и незанятых заявками с иным адресом блоков.

Фор,иу,? а изобретент?

У с1 р О?1 с т в о дл я а д p Bc B II H II б I o K o B Il 3 M Rти, содержащее группы переключателей, группу элементов И, первый дешифратор, три элемента И вЂ” HF. и элемент ИЛИ, входь? которого подключены к выходам элементов И г р уппь1, вь? ход элемента ИЛИ соединен с первыми входами первого и второго элементов И вЂ” -HF, вторые входы которых соединены с входом задания режима на?альной установки устройства, третий вход первого элемента И вЂ” НЕ соединен с первым входом третьего элемента И вЂ” HE и является первым синхрîвходсм устройства, третий вход второго элемента И вЂ” HE является вторым синхровходом устройства, первые входы элементов И группы соединены с выходами соответствующих переключателей группы, а их вторые входы — с соответству?огцими выходамн первого дешифратора, входы которого явл яются адрес??ь?ми входами устрсйст!зя, От.:?пнйю??(ееся тем, что с целью расши1е?:?я области его

IIp f..IåBåíèÿ, за счет индицирона??Ня полНОЙ заыятост!? Вне. и?? ими заявками включенlBlx блоков, в ?1егс введень инвертор, триггер, счетчик стека, три слска памяти адресов и второй деп?куратор. причем выходы второго дешифрлтора являются выходами устройства для возбуждения адресуемого слока памяти. выход тпиггера является выходом устройства, ля индицирования полной занятости блоков и;:мяти, вход сброса тригf cDB coB;"è. BII c R. o1oì уста20 новки счетчика стека !» явл;,стся входом сброса,стройства, синхрозхсд -;1О?|ггера соединен с вь?ходом обратного переноса счетчика стека, входы инкреMепта и декремента которого соединены с выходами соотВе? Отвенно ??ервсго н т1?етьегс Э.1смснтОВ

Vi — НЕ, инфор 1а и онные выходы счетчика стека соединены с адреснымн входами первого блока памяти адресов, информационные входы которого объеди??ены с адресными входами второго и третьего блоков памяти адресов и адресным входом устройства, вход записи первого блока памяти адресов соединен с выходом второго элемента И вЂ” НЕ. информационный выход первого блока памяти адресов соединен с информационным входом второго блока памяти адресов, информационный выход которого соединен с в.,одом ьторого дешифрато ра, вход записи второго блока памяти адресов соединен с выходом третьего элементта И вЂ” НЕ, второй вход которого соединен с информационным выходом третьего блока памяти адресов, информационный вход и вход записи которого соединены соответствеHHQ с управляющим входом и вторым синхровходом устройства, вход задания режима начальной установки устройства соединен через инвертор с третьим входом третьего элемента И--HE.

1481777

О

Ж

U

Составитель А. Иванов

Редактор С. Патрушева Техред И. Верес Корректор В. (ирняк

Заказ 2691/50 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Рау шская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101