Устройство для сопряжения магистрали с каналом связи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для передачи импульсно-потенциальных сигналов управления вычислительными процессами по магистрали данных в вычислительных комплексах и локальных сетях. Целью изобретения является расширение области применения устройства и сокращение оборудования путем передачи по магистрали данных импульсно-потенциальных сигналов управления вычислительными процессами. Устройство содержит генератор импульсов, распределитель импульсов, элемент И, триггер, два регистра и коммутатор. Цель достигается тем, что в устройство введены элементы ИЛИ, два триггера, четыре элемента И и группа из М элементов И, соединенные определенным образом. 1 ил.

СОЮЗ СОНЕТСНИХ, СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gg g С 06 Р 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ.

ПРИ ГКНТ СССР (21) 4294149/24-24 (22) 05.08,87 (46) 23.05.89. Бюп. Р 19 (72) А.В. Анцыгин, В.И. Гречишников, А.А. шанин и H.ß. Полонская . (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М- 604175» кл. Н 04 Ь 25/40, 1978.

Авторское свидетельство СССР

Р 663124, кл. Н 04 Ь 25/40, 1979. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МАГИСТРАЛИ С КАНАЛОМ СВЯЗИ (57) Изобретение относится к вычислительной технике и может быть использовано для передачи импульсно-потенциальных сигналов управления вычислиИзобретение относится к вычислительной технике и может быть использовано для передачи импульсно-потенциальньм сигналов управления вычислительными процессами по магистрали данных в вычислительньм комплексах и локальных сетях.

Целью изобретения является расширение области применения и сокращение оборудования путем передачи по магистрали данных импульсно-потенциальных сигналов управления вычислительными процессами.

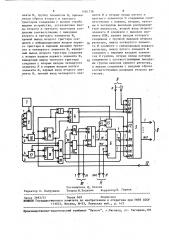

На чертеже приведена схема устройства.

Устройство содержит генератор 1 импульсов, распределитель 2 импульсов, первый элемент И 3, первый триггер 4, коммутатор .5, первый и второй

„„SU„„1481778 А 1

2 тельными процессами по магистрали данных в вычислительных комплексах и локальных сетях. Целью изобретения является расширение области применения устройства и сокращение оборудования путем передачи по магистрали данных импульсно-потенциальных сигналов управления вычислительными процессами. Устройство содержит гене- ратор импульсов, распределитель импульсов, элемент И, триггер, два регистра и коммутатор. Цель достигается тем,что в устройство введены элементы ИЛИ, два триггера, четыре элемента И и группа из М элементов И, соединенные определенным образом.

1 ил. регистры 6 и 7, выходы 8 устройства, информационные входы 9 устройства, входы 10 управляющих импульсных сигналов, входы 11 управляющих потенциальных сигналов, вход 12 сигнала строба вьдачи, элемент ИЛИ 13,второй триггер 14, третий триггер 15, второй-пятый элементы И 16-19, группу элементов И 20»-20»».

Устройство работает следующим образом.

Импульсно-потенциальные сигналы . управления, поступающие на входы

10 и 11 устройства, вьдаются в магистраль данных через выходы 8 устройства каждый раз при поступлении импульсного сигнала на любой из входов 10.

1481 778

Выдача импульсно-потенцйальных сигналов синхронизируется с сигналом строба выдачи, поступающего «а вход

12 устройства и имеет приоритет по отношению к выдаче данных, поступающих на входы 9 устройства.

В исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии. Цепи установки в исходное состояние условно не показаны.

Когда триггер 4 находится в "0", на выходы устройства 8 через коммутатор 5 выдаются сигналы с информационных входов 9.

Импульсный сигнал, пришедший на

К-й разряд входов 10, установит в

"1" К-й разряд регистра 7. Потенциал с К-го разряда регистра 7 поступает 20 через элемент ИЛИ 13 на вход элемента И 16. Импульс с первого выхода распределителя импульсов 2 проходит через элемент И 16 и устанавливает в "1" триггер 14. 25

Поскольку на входах элемента И 18 имеются единичные потенциалы с прямого выхода триггера 14 и инверсного выхода триггера 15, импульс с второго выхода распределителя импульсов 2 30 проходит через него и разрешает запись на регистр 6 содержимого регистра 7 и потенциальных сигналов с входов 11 устройства.

Импульсный сигнал с третьего выхода распределителя 2 импульсов проходит через элемент И 19, так как триггер 15 находится в "0", и устанавливает в "0" те разряды регистра

7, которые уже переписаны в регистр

6, это производится через элементы И группы 20.

По импульсу с четвертого выхода распределителя 2 импульсов устанавливается в "1" триггер 15 ° .

Триггер 4 устанавливается в "1" и разрешает прохождение кода с регистра 6 на выходы 8 устройства через коммутатор 5 по переднему фронту сигнала 12 строба выдачи при условии

"1" триггера 14.

Если за время выдачи на входы 10 не поступило ни одного импульсного сигнала, то триггеры 14 и 15 сбрасываются по заднему фронту сигнала 12 ,строба выдачи, а триггер 4 устанавливается в "0" по переднему фронту следующего сигнала 12 строба выдачи если триггер 14 находится в "0".

Частота импульсов генератора 1 должна быть выбрана в соответствии с временем переключения используемых в устройстве элементов.

Восстановление импульсно-потенциальных сигналов управления на приемной стороне производится с помощью окраски передаваемых кодов в (N+1)-м разряде, который равен "0" при передаче данных с входов 9 и—

"1" при передаче сигналов управления.

Формула изобретения

Устройство для сопряжения магистрали с каналом связи, содержащее генератор импульсов, выход которого с о еди не н с входом рас пр еделит еля импульсов, первый элемент И, первый триггер, коммутатор, первый и второй регистры, причем группа выходов коммутатора является группой выходов устройства для подключения к входам магистрали данных, первая группа информационных входов коммутатора является группой входов устройства для подключения к выходам магистрали данных, вторая группа информационных входов коммутатора подключена к группе выходов первого регистра,первые стробирующий и информационный входы коммутатора подключены к инверсному выходу первого триггера, вторые стробирующий и информационный входы коммутатора соединены с прямым выходом первого триггера, установочные входы разрядов второго регистра являются входами устройства для подключения к шинам импульсных управляющих сигналов управляющей магистрали, группа выходов второго регистра соединена с первой группой информационных входов первого регистра, вторая групна информационных входов которо-. го является группой входов устройства для подключения к шинам потенциальных управляющих сигналов управляющей магистрали, вход строба выдачи устройства соединен с синхровходом первого триггера и первым входом первого элемента И, выход которого соединен с входом сброса первого триггера, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения и сокращения оборудования, оно содержит элемент ИЛИ,. второй и третий триггеры, с второго по пятый эле10

Составитель И. Хазова

Редактор С. Патрушева Техред М.Ходанич КорректорВ Гирняк

Заказ 2692/51 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,!01

5 14 менты И, группу элементов И, причем входы сброса второго и третьего

I триггеров соединены с входом строба выдачи устройства, установочные входы второго и третьего триггеров соединены соответственно с выходами второго и третьего элементов И, прямой выход второго триггера Соединен с информационным входом первого триггера и первыми входами третьего и четвертого элемента И, инверсный выход второго триггера соединен с вторым входом первого элемента И, инверсный выход третьего триггера соединен с вторым входом четвертого элемента И и первым входом пятого элемента И, первый вход второго элемента И, третий вход четвертого эле1

81 778 6 мента И и вторые входы пятого и третьего элементов И соединены соответственно с первым, вторым, треть.им и четвертым выходами распредели5 теля импульсов, второй вход второго элемента И соединен с выходом элемента ИЛИ, группа входов которого соединена с группой выходов второго регистра, выход четвертого элемента И соединен с синхровходом первого регистра, выход пятого элемента И соединен с первыми входами элементов И группы, вторые входы которых соединены с соответствующими выходами группы выходов первого регистра, а выходы соединены с входами сброса соответствующих разрядов второго регистра.