Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет адаптации быстродействия устройства к параметрам абонента. В устройство введены счетчики и входные и выходные коммутаторы которые объединяют необходимое количество секций устройства в один или несколько каналов требуемого быстродействия в зависимости от информации, поступающей на вход задания режима работы блока управления. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1

yg 4 С 11 С 11/00 (, Г . -i ..1 Ц pl

-: - -UI

"I р . л,...

В .- :Di;,) ) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4177864/24-24 (22) 06.01.87 (46) 23.05.89. Бюл. Р 19 (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (72) В.В. Жила, А.К. Шилов, Н.А. Пудзенков и Г.Н. Лукашкова (53) 681.327.6(088,8) (56) Шигин А.Г., Дерюгин А.А. Цифровые вычислительные машины. — M.

Энергия, 1976, с. 495.

Авторское свидетельство СССР

0 932567, кл. С 11 С 11/00, 1972.

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных информационно-измерительных системах, многопроцессорных вычислительных комплексах.

Цель изобретения — расширение функциональных возможностей устройства за счет адаптации быстродействия устройства к параметрам абонента.

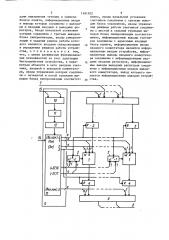

На чертеже представлена структурная схема буферного запоминающего устройства.

Устройство содержит блоки 1 памяти, счетчики 2, регистры 3 и 4, коммутаторы 5 и 6, информационные входы

7 и выходы 8, блок 9 синхронизации, состоящий из последовательно соединенных регистра 10 управления, дешифратора 11, блока 12 постоянной памяти и распределителя 13 импульсов, вход 14 синхронизации блока 9, вход

15 задания режима работы блока 9, (54) БУФЕРНОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, Цель - pacmrpqHae функциональных возможностей за счет адаптации устройства к параметрам абонента. В устройстве введены счетчики и входные и выходные коммутаторы, которые объединяют необходимое количество секций устройства в один ипи несколько каналов требуемого быстродействия в зависимости от информации, поступающей на вход задания режима работы блока управления. 1 ил.

2 входы 7 соединены с информационными входами коммутатора 5, выходы которого соединены с входами регистров 3, выходы которых соединены с информационными входами блоков 1 памяти, выходы которых соединены с входами регистров 4, выходы которых соединены с информационным -входом коммутатора 6, выход которого соединен с выходом 8 устройства, выходы счетчиков 2 соединены с адресными входами блоков 1, первая и вторая группы выходов блока 9 соединены с входами управления чтением и записью блоков

1, третий выход блока 9 — с входами начальной установки счетчиков 2,.регистров 3 и 4, четвертая и пятая группы выходов блока 9 — с входами управления коммутаторов, шестая и седьмая группы выходов блока 9— с входами управления режимом работы счетчиков 2.

1481852

Устройство работает следуппцим образом, Цикл работы БЗУ.состоит из двух этапоя: этапа ввода и этапа вывода массивов информационных слов. На первом этапе в блоки 1 вводится информация от всех участвующих в данном цикле обмена абонентов. На втором— эта информация выводится заинтересо- 1р ванным в ней абонентам. Вся информация или некоторая ее часть может не выводиться в данном цикле, т.е. БЗУ используют для хранения массивов информации. Таким образом, предлага- 15 емое устройство работает в трех режимах: обмена, хранения и смешанном.

Частным случаем любого из этих режи мов является обмен только .одним информационным словом, что возможно 2р в известном устройстве. Каждый из режимов предлагаемого БЗУ имеет подрежимы: "Первый пришел — первый вышел" и "Первый пришел — последний вьппел" ° 25

С началом этапа ввода на выходе блока 9 вырабатывается сигнал сброса в "0", который, поступая на первые входы регистров 3 и 4 и счетчиков 2,. очищает их. Одновременно по входу 15 3р на входы регистра 10 поступают коды абонентов. В кодах содержится информация об абоненте, передающем инфор-, мацию в данном цикле, и об абоненте, принимающем ее. Зто необходимо для 35 согласования канала по максимальному быстродействию и требуемой емкости.

В режиме хранения код не содержит информацию об абоненте, являющемся приемником, поэтому на этапе вывода 4р введенный массив из БЗУ не выводится. В дешифраторе 11 вырабатываются сигналы, управляющие работой блока 12 постоянной памяти, хранящего программу перестройки распределителя 13 на 45 данный цикл работы. При этом программой .учитывается, что часть секций может быть занята хранением информации, полученной в предыдущих циклах обмена. Выбранная из блока 12 постоянной памяти программа поступает в распределитель. Затем начинается собственно ввод информации в БЗУ, который синхронизируется сигналами, поступающими на первую группу входов блока 9 по входу 14 синхронизации.

По окончании этапа ввода начинается этап вывода. На этом этапе различие в работе устройства н зависимости от подрежимов "Первый пришел— первый вьппел" или "Первьп пришелпоследний вьппел" заключается только в способе формирования адресов ячеек, из которых происходит считывание информации.

В подрежиме "Первый пришел — первый вышел" этап вывода начинается с появления на выходе блока 9 сигнала сброса в нуль, который, поступая на первые входы адресных счетчиков, формирует адреса нулевых ячеек. С них начинается вывод. Адрес следующей ячейки каждого блока 1 получается при сложении содержямого адресных счетчиков с единичными сигналами, поступающими с пятой группы выходов блока 9 на вторые входы адресных счетчиков 2. В подрежиме "Первый пришел — последний вьппел" адрес ячейки, с которой начинается вывод, сформирован в адресных счетчиках уже на этапе ввода. Следукпцие адреса получаются вычитанием из содержимого адресньм счетчиков по единице путем подачи на их третьи входы единичных сигналов с шестой группы выходов блока 9.

В буферном запоминающем устройстве осуществляется оперативное изменение быстродействия за счет секционирования памяти. Накопитель и связанные с ним регистры и адресные счетчики представляют собой секцию. Несколько секций образуют канал, предоставляемый абоненту. Использование в предлагаемом устройстве коммутаторов, которые в соответствии с программой, заложенной в блоке постоянной памяти, объединяют в каналы необходимое количество секций, позволяет производить адаптацию быстродействия и емкости канала под характеристики соответствукпцего абонента. Общее количество секций в устройстве определяется числом и быстродействием одновременно обменивающихся абонентов и также быстродействием накопителей.

Формула изобретения

Буферное запоминающее устройство, содержащее входные и выходные регистры, блоки памяти, блок синхронизации, первая и вторая группы выходов которого соединены соответственно с вхо14818 дами управления чтением и записью блоков памяти, информационные входы и выходы которых соединены с выходами и входами входных и выходных реГистров, входы начальной установки которых соединены с третьим выходом блока синхронизации, входы синхронизации и задания режима работы которого являются входами синхронизации и управления режимом работы устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет адаптации быстродействия устройства, к параметрам абонента в него введены счетчики, входной и выходной коммутаторы, входы управления которых соединены с четвертой и пятой группами выходов блока синхронизации соответст10

52 6 венно, входы начальной установки счетчиков соединены с третьим выходом блока управления, входы управления режимом работы счетчиков соединены с шестой и седьмой группами выходов блока синхронизации соответственно, информационные выходы счетчиков соединены с адресными входами блока памяти, информационные входы входного коммутатора являются информационным входом устройства, информационные выходы входного коммутатора соединены с информационными входами входных регистров, информационные выходы выходных регистров соединены с информационным входом выходного коммутатора, выход которого является информационным выходом устройства.