Параллельный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к аналого-дискретным устройствам и может быть использовано в системах обработки и передачи информации и в системах управления. Цель изобретения - повышение точности и упрощение устройства. Применено два входных аналоговых сигнала, сдвинутых один относительно другого на 180°. Преобразователь состоит из матрицы резистивного делителя напряжения, групп компараторов напряжения младших и старших разрядов унитарного кода, кодирующего устройства, преобразующего унитарный код в двоичный выходной код, шины прямого входного сигнала, шины противофазного входного сигнала управляющей шины, шин опорных напряжений и выходной шины. Достижение цели обуславливается тем, что количество резисторов делителя напряжения равно половине разрядов унитарного кода, а к входу преобразователя подключены прямой и противофазный входные сигналы. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11) с5)) 4 Н 03 М 1/36

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1;.> .,0 pj .é" . !

1L i 4 Л "

Б Ё1Ь ;И(3

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4329542/24-24 (22) 09.10.87 (46) 23.05.89. Бюл. В 19 (72) В.H. Паулаускас (53) 681 .325(088.8) (56) Гнатек Ю.P. Справочник по цифроаналоговьм и аналого-цифровьм преобразователям.-M: Радио и связь, 1 982, с.327-328.

Бахтиаров Г.Д. и др. Аналогоцифровые преобразователи.— М.: Советское радио, 1980, с. 30. (54) ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к аналогодискретным устройствам и может быть использовано в системах обработки и передачи информации и в системах управления. Цель изобретения " повы!

Изобретение относится к аналогодискретным устройствам и может быть использовано в системах обработки и передачи информации и в системах управления.

Цель изобретения - повышение точности и упрощение преобразователя.

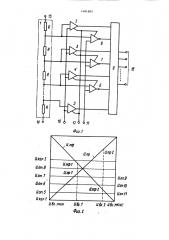

На фиг. 1 приведена блок-схема параллельного аналого-цифрового преобразователя (АЦП), на фиг. 2 — диаграммы входных и опорных напряжений (по оси абсцисс отложено входное переменное, а по оси ординат — опорные напряжения, прямые линии представляют прямое U> и противофазное U.„ф напряжения, уровни опорных напряжений обозначены горизонтальными лишение точности и упрощение устройства. Применено два входных аналоговых сигнала, сдвинутых один относителЬно о другого на 180 . Преобразователь .состоит из матрицы резистивного делителя напряжения, групп компараторов напряжения младших и старших разрядов унитарного кода, кодирующего устройства, преобразующего унитарный код в двоичный выходной код, шины прямого входного сигнала, шины противофаэного входного сигнала управляющей шины, шин опорных напряжений и вькодной шины. Достижение цели обуславливается тем, что количество резисторов делителя напряжения равно половине разрядов унитарного кода, а к входу преобразователя подключены прямой и противофазный входные сигналы. 2 кп.

2 ниями, опорные напряжения компараторов обозначены !) „„, °, !) „ соответственно, шины опорных напряжений U,и U RE, соответственно) .

Аналого-цифровой преобразователь состоит Hs реэистивного делителя 1 напряжения, группы компараторов 2-8 напряжения младших и старших разрядов унитарного кода, кодирующего логического устройства 9,.преобразующего унитарный код .в двоичный вькодной код, шины 10 прямого входного сигнала, шины 11 противофазного входного сигнала, шины 12 управления (тактирования), первой 13, второй 14 шин опор ных напряжений U „, и U р соответственно и выходной шины 15. з 14818

Преобразователь работает следующим образом.

Если прямой входной сигнал или противофазный сигнал на входе преоб5 разователя превышает опорное напряжение, то на юсопе этого компаратора напряжение соответствует "Лог. (фиг. 1) . При этом компараторы 6-8 группы старших разрядов унитарного кода на своих прямых выходах редставляют информацию в обратном коде.

Для получения кода старших разрядов в прямом коде необходимо. информацию с компараторов 6-8 снимать с ин- 15 версного выхода, тогда результат сравнения будет представлен в прямом коде. Например, если входное переменное напряжение (фиг. 2) будет U< то прямой сигнал на входной шине 1 О 20 преобразователя соответствует U r а напряжение на шине 11 противофазного сигнала соответствует U „,, при этом на выходе компараторов 2-4 напряжение будет соответствовать "Лог.1", 25 компаратора 5 — "Лог,О" выходные" состояния компараторов 6-8 - "Лог.О" на инверсных выходах.

Если входное переменное напряжение будет U „x, то прямой сигнал Hà 30 шине 1 0 будет соответствовать U, а сигнал на шине 11 противофазного сигнала — U z, при этом компараторы

2-7 на выходе будут иметь "Лог.1", а компаратор 8 - "Лог.О". При снятии информации с компараторов групп в прямом коде кодовый кортеж для первого U варианта будет пред8xi ставляться 1110111, а для.второго варианта Uq» < 1001 111. Кодовый кор- 4р теж в унитарном коде на прямых выходах младшей группы и инверсных выходах старщей группы компараторов будет иметь вид для первого варианта

ОООО>11, а для второго варианта 45

011lllll .

В предлагаемом преобразователе уменьшено количество резисторов в два раза, в результате чего уменьшается площадь кристалла для монолитного АЦП или уменьшается объем и вес АЦП для дискретного исполнения.

С уменьшением площади кристалла и

83 количества компонентов на кристалле увеличивается процент выхода годных изделий, так как процент выхода годных кристаллов на пластине пропорционален площади кристалла и количеству компонентов. При монолитном изготовлении преобразователя с уменьшением количества резисторов в. делителе напряжения увеличивается его линейность, а в результате этого увеличивается процент выхода годных преобразователей как следствие уменьшения брака по дифференциальной и интегральной нелинейностям.

Формула изобретения

Параллельный аналого-цифровой преобразователь, содержащий две группы компараторов, общее число которых

2"И, где n — число разрядов преобразователя, делитель напряжения, первый вход которого соединен с первой шиной опорного напряжения, кодирующее логическое устройство, входы ко- торого соединены с выходами соответствующих компараторов первой и второй групп, входы стробирования которых подключены к управляющей шине, а выходы кодирующего логического устройства являются выходной шиной, первые входы компараторов впервой группы объединены и являются шиной прямого входного сигнала, а вторые входы соединены с соответствующими выходами резистивного делителя налряжения> о т. л и ч а ю шийся тем,что,.с целью повышения точности и упрощения преобразователя, в него введена шина противофазного входного сигнала, а делитель напряжения выполнен на 2" +1 последовательно соединенных резисторах„ причем второй вывод первого резистора является первым входом делителя напряжения, а второй вывод последнего резистора подключен к второй шине опорного напряжения, при этом первые входы компараторов второй группы объединены с вторыми входами соответствующих компараторов первой группы, а вторые входы объединены и подключены к шине противофазного входного сигнала.

1481883