Преобразователь двоичных чисел в двоично-десятичные

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия. Для этого в преобразователе двоичных чисел в двоично-десятичные, содержащем разрядные преобразователи 1-4 и двоично-десятичные сумматоры 11-13, последние соединены в пирамидальную схему и выполнены из двоичных сумматоров 5, 6, 9 и сумматоров 7, 8, 10 коррекции. При этом инверсные выходы переноса нечетных двоичных сумматоров соединены с входами вычитания (-6) соответствующих сумматоров коррекции, а прямые выходы переносов четных двоичных сумматоров соединены с входами сложения (+6) соответствующих сумматоров коррекция. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1481897 (51)4 Н 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Знак,фоичнм evc o б 3i ббббПlб бб б ббпр б б б б б ббббУЯ

33вцчно -десятичноа число

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 4257545/24-24 (22) 08.06.87 (46) 23.05.89. Бюл. ¹- 19 (71) Институт кибернетики им ° B. Н. Глушк ова (72) В. П. Боюн, Б. Н. Малиновский, В. Е. Реуцкий и M. Е. Урсу (53} 681.325(088.8) (56) Авторское свидетельство СССР

¹ 960794, кл. Н 03 M 7/1 2, 1982.

Патент США ¹- 3882483, кл. 340-347, 1975. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ

В ДВОИЧНО-ДЕСЯТИЧНЫЕ (57) Изобретение относится к вычислительной технике. Целью изобретения являе тся повышение быс трод ей с твия.

Для этого в преобразователе двоичных чисел в двоично-десятичные, содержащем разрядные преобразователи 1 — 4 и двоично-десятичные сумматоры 11

13, последние соединены в пирамидальную схему, и выполнены из двоичных сумматоров 5, 6, 9 и сумматоров 7, 8, 10 коррекции. При этом инверсные выходы переноса нечетных двоичных сумматоров соединены с входами вычитания (-6} соответствующих сумматоров коррекции, а прямые выходы переносов четных двоичных сумматоров соединены с входами сложения (+6) соответствующих сумматоров коррекции. 1 ил.

1481897

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобраэова5 телей.

Целью изобретения является повышение быстродействия.

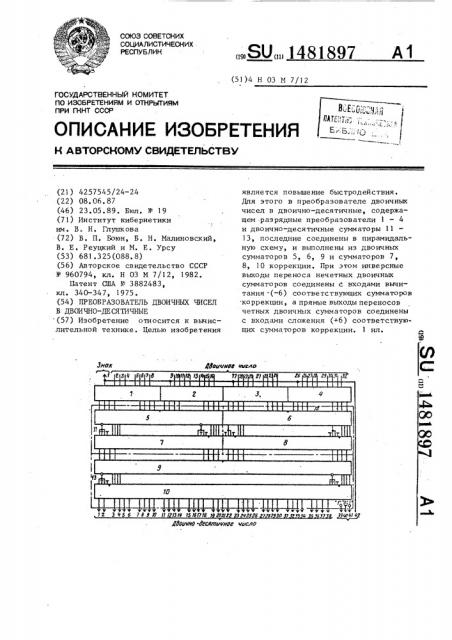

На чертеже изображена блок-схема преобразователя ° 10

Схема преобразователя содержит разрядные преобразователи 1-4, двоичные сумматоры 5 и 6, сумматоры 7 и

8 коррекции, двоичный сумматор 9, сумматор 10 коррекции. Двоичные сум- 15 маторы 5 и 6 и сумматоры 7 и 8 коррекции в совокупности образуют двоично-десятичные сумматоры 11 и 12, которые представляют первую ступень суммирования. Двоичный сумматор 9 и 20 сумматор 10 коррекции в совокупности образуют двоично-десятичный сумматор

13, представляющий вторую ступень суммирования. Разрядные преобразователи 1 — 4 могут быть выполнены на 25 программируемых запоминающих устройства -(ПЗУ) .

Предлагаемый преобразователь работает следующим образом.

При поступлении входного двоичного 30 кода на входы преобразователя на вы-. ходах блоков ПЗУ 4, 2 и 1, 3 появляются соответственно двоично-десятич- . ные коды и двоично-десятичные коды с избытком шесть, эквивалентные слагаемым исходного двоичного числа, Двоично-десятичное сложение осуществляется в коде с избытком шесть и последующей коррекцией результата.

Этот код получается путем прибавления 40 к содержимому каждой тетрады двоичнодесятичного кода числа шесть. Коррекция результата состоит в вычитании .числа шесть из содержимого тех тет-. рад, где отсутствовал межтетрадный перенос.

В каждый из блоков ПЗУ 2 и 4 занесены естественные- двоично-десятичные коды для всех двоичных чисел данной группы. В каждый из блоков ПЗУ 1 и 3 заносятся двоично-десятичные коды с избытком шесть для всех двоичных чисел данной группы. Смешаный код ре. зультата, полученного на выходе двоичного сумматора 5, корректируется в естественный двоично-десятичный код сумматором 7 первой ступени..

Для этого каждая тетрада сумматора 7 суммируется с кодом 0000, если имеется межтетрадный перенос из данной тетрады. в сумматоре 5, и с кодом

1010, если межтетрадный перенос из данной тетрады сумматора 5 отсутствует, Операция вычитания избытка шесть заменена на сложение с его дополнением (1010) . Смешанный код результата, полученного на выходе сумматора 6, корректируется в двоичнодесятичный код с избытком шесть сумматором 8 коррекции. Для этого каждая тетрада сумматора 8 коррекции суммируется с двоичным кодом 0000, если межтетрадный перенос из данной тетрады сумматора 6 отсутствует, и с кодом 0110, если имеется межтетрадный перенос из данной тетрады сумматора 6.

Естественный двоично-десятичный код с выходов сумматора 7 коррекции и двоично-десятичный код с избытком шесть с выходов сумматора 8 коррекции поступают на входы первого и второго слагаемых сумматора 9 второй ступени.

Код, полученный на выходах сумматора

9, корректируется в естественный двоично-десятичный код сумматором 10 коррекции. Для этого каждая тетрада сумматора 10 коррекции суммируется с кодом 0000, если имеется межтетрадный перенос из данной тетрады сумматора 9, и с двоичным кодом 1010 если указанный перенос отсутствует.

В зависимо сти о т зйач ения старше- . го разряда входного числа, поступившего на первые входы блоков ПЗУ 1-4, выбирается область памяти, соответствующая положительному или отрицательному входному числу. Содержимое для ячеек памяти как для положительных, так и для отрицательных двоичных чисел представляет собой положительные десятичные эквиваленты, так как десятичные числа должны быть представлены в прямом коде.

Знак входного числа может передаваться на выход преобразователя в виде четвертого разряда тетрады знака, первый и третий разряды тетрады знака и второй разряд тетрады знака соединены (для кода КОИ- 8) соответственно с входами логической "1" и "0" преобразователя.

Примеры преобразователя двоичных чисел в двоично-десятичные.

Пример 1. 148)897

Двоичное число

Знак числа

Исходный код 0

Код на выходе

ПЗУ 4

Код на выходе

ПЗУ 3

После суммирования

Переносы

Коррекция

1000 10)l

1110 1011 l)00

0000 0011 l)00

1 1 О

0000 0000 )OIO

1000 1 00

О 0

1010 10) О

Код на выходе

ПЗУ 2

Код на выходе

ПЗУ i 1000

После суммирования

Пе рено сы

Ко рр екция

1000

0000

1101 0111

О )

0000 0110

1000 1101 1101 1000 1110 1000 1110 0111 1100

1000 1101 1101

О О О

10) О 1010 1010

ppip 0111 00111 0011 i -0000 1000 1000 0)01 0010

2 7 7, 3 0 8 8 5 2

Прим ер 2.

Двоичное число

Знак числа

Ф1 000

1110 0111 1100 0110

1001 0101 101!

О 1 О

1010 0000 )010 1 110

1010

1000

1010

1000 0111 1001> 0110 »110) 0110 1100 1010 1001 1000

1000 0111 1010 0000 0011

О О. О. 1 1.

0000 0000 0000 0110 0110

1000 0111 1010 0110 1001 1010 01)0 1000 1000 1010 1000 Ql11 1010 0110 1001 I )00

0 О О О 0 О

1010 1010 1010 1010 1010 1010

1110 1011 )101 11)1

О 0 О О

101 Î 10) О 1010 1010

0010 0001 0100 0000 0011 0110 1000 010) 0111 1001

Де ся тично е число,> ) 4 О, 3

5 7 9

После второго суммирования

Переносы

Коррекция

Десятичное число +О.

Исходный код

Код на выходе

ПЗУ 4

Код на выходе

ПЗУ 3

После с уммиров ания

Переносы

Коррекция

Код на выходе ПЗУ 2

Код на выходе ПЗУ 1

После сум. мирования

Переносы

Коррекция

После второго суммиров ания

Переносы

Коррекция

QQI 0000 1000 0111 01)0 0)01 1011 0100

1 )000 0000

0010 0110 0000 0011 0) 10

1000 1000 0160 0)11 0011 0110 0000

1100 1!О 1010 1001 1011 1010 1011 ) 100

0010 1110 0010 1110 0001 1100

1 0 1 О l . 0

0110 0000 0110 0000 0110 00000

1001 0000 1110 1110 1011 0010 .О 1 О О О 1

1010 0000 1010 1010 10) О 0000

000 0000 0110 1)00 100) 0001 0011 1101

1 1001 0101

001 0 1000 0011,0101 0101

L"00I 0110 0011 0011 0111 1001 OQIO

Ю

1010 0000 0010 0010 1010

О.. 1 1 l. О

0000 0110 0110 0110 0000

1897

Со ставитель M. Аршавский Редактор М, Бланар Техред Jl. Олийнык Корректор И. Горная

Заказ 2701/56 Тираж 885 Подпис ное

ВНИИПИ Государственного комитета по изобретениям и открытиям. при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Óærîðîä, ул. Гагарина,101

5 148

Фо рмула из о б ре те ния

Преобразователь двоичных чисел в двоично-десятичные, содержащий ступени двоично-десятичных сумматоров и группу разрядных преобразователей, входы младших разрядов которых соединены с входами соответствующих разрядов преобразователя, знаковый вход которого соединен с входами старшего разряда всех разрядных преобразоватепей и является выходом знака преобразователя,.информационные выходы которого являются выходами последнего . двоично-десятичного сумматора, выходы первого и второго разрядных преобразователей соединены соответственно с первым и вторыми входами первого двоично-десятичного сумматора первой ступени,. выходы первого двоичнодесятичного сумматора каждой ступени соединены с первыми входами первого сумматора соседней старшей ступени отличающийся тем, что, с целью повышения быстродействия, в нем выходы i-ãî (i = 1 — и/m) нечетного разрядного преобразователя соединены с первыми входами (1+)- ()-ro т двоично-десятичного сумматора первой ступени, а выходы i-го четного разрядного преобразователя соединены с

1 вторыми входами — -го двоично-деся2 тичного сумматора первой ступени, 5 где и m — разрядности входного кода

У и разрядного преобразователя соответственно, выходы нечетных двоично-деэ сятичных сумматоров каждой ступени соецинены с первыми входами двоично1р десятичных сумматоров соседней старшей ступени, вторые входы которых соединены с выходами четных двоичнодесятичных сумматоров соседней младшей ступени, причем все двоична-десятичные сумматоры содержат разделенные на тетрады сумматор коррекции и двоичный сумматор, инверсные выходы переноса каждой тетрады нечетных двоичных сумматоров каждой ступени соединены с входами в то ро го и четв ертого разрядов соответствующей тетрады сумматоров коррекции, входы первого и третьего разрядов которых соединены с входом логического нуля преобразо25 вателя, прямые выходы переноса каждой тетрады четных двоичных сумматоров соединены с входами второго и третьего разрядов соответствующих сумматоров коррекции, входы первого и четвертого разрядов которых соединены с входом логического нуля преобразователя.