Преобразователь чисел из модулярного кода в позиционный код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для преобразования числа из системы остаточных классов /СОК/ в позиционный код и определения знака числа. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что преобразователь, содержащий блок 1 модульных накапливающих сумматоров, блок 4 контроля обнуления, позиционный сумматор 8 и мультиплексор 9, содержит блок 2 модульных накапливающих сумматоров, блок 3 преобразования остатков из прямого кода в дополнительный код, блок 5 контроля обнуления, блок 6 определения знака числа и коммутатор 7 с соответствующими связями. Сущность изобретения состоит в том, что преобразование в позиционный код происходит по двум каналам в прямом и дополнительном кодах одновременно. 1 з.п.ф, 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5I) 4 Н 03 М 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHAM

ПРИ ГКНТ СССР (21) 4292794/24-24 (22) 03.08.87 (46) 23.05,89. Бюл. М 19 (72) А.П.Болтков, С.H Хлевной и И.Г.Рыбачук (53) 681,3(088.8) (56) Авторское свидетельство СССР

У 1267625, кл. II 03 M 7/18, 1985.

Авторское свидетельство СССР

11 554536,. кл. Н 03 M 7/18, 1974.

„„SU„„1481898 А1

2 (54):1РЕОБРАЗОВАТЕЛЬ ЧИСЕЛ ИЗ МОДУЛЯРНОГО КОДА В ПОЗИЦИОННЫЙ КОД (57) Изобретение относится к вычислительной технике и предназначено для преобразования числа из системы остаточных классов (СОК) в позиционный код и определения знака числа.

Целью изобретения является повьппение быстродействия. Поставленная цель

1481898 достигается тем, что преобразователь, содержащий блок 1 модульных накапливающих сумматоров, блок 4 контроля обнуления, позиционный сумматор 8 и мультиплексор 9, содержит блок 2 модульных накапливающих сумматоров, блок 3 преобразования остатков иэ прямого кода в дополнительный кад

Изобретение относится к вычислительной технике и предназначено для преобразования числа из системы остаточных классон (СОК) в позиционный кад и определения знака числа, 5

Цель изобретения — повышение быстродействия.

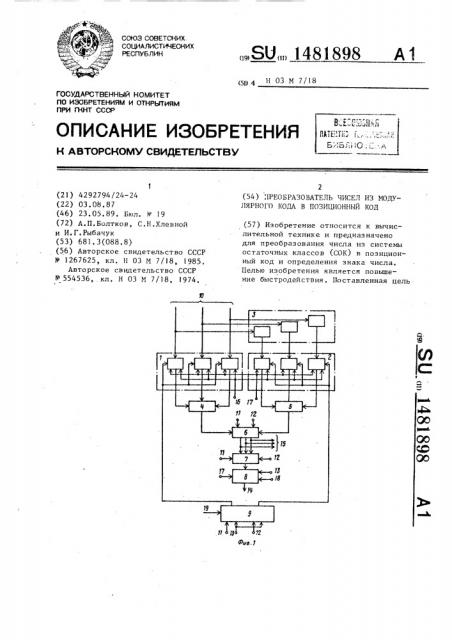

На фиг.l представлена схема преобразователя чисел из модулярного кода в позиционный код, на фиг,2 - 10 схема блока определения знака числа, Преобразователь (фиг.1) содержит первый блок 1 модульных накапливающих сумматоров, второй блок 2 модульных накапливающих сумматоров, блок 3 преобразования остатков иэ прямого када в дополнительный код, первый 4 и второй 5 блоки контроля обнуления, блок 6 определения знака числа, коммутатор 7, позиционный сумматор 8, 20 мультиплексор 9, информационный вход

10 преобразователя, входы ll и 12 дополнительного и прямого кода остатка по младшему основанию преобразователя, вход 13 значения младшего ос- нования преобразователя, выход 14 результата преобразователя, выход 15

1 знака преобразователя, первый тактовый вход 16 преобразователя, вход 17 начальной установки преобразователя, второй тактовый вход 18 преобраэова" теля, Блок 6 определения знака числа (фиг.?) содержит шифратор 20, дешифратор 21 и схему 22 сравнения.

Блоки 4 и 5 комбинационные, на их З5 выходах появляется сигнал логической

"1", если на выходах блоков 1 и 2 нулевые значения, Блок 6 определения знака числа представляет собой комбинационный блок. Па входы дешифратара 21 подаблок 5 контроля обнуления, блок 6 определения знака числа и коммутатор 7 с соответствующими связями. Сущность изобретения состоит н там, что преобразование в позиционный код происходит па двум каналам в прямом и дополнительном кодах одновременно.

1 3 опе ф-лыГ 2 иле Г 3 табл е

4 ются сигналы с выходов блоков контроля обнуления, а на входы схемы 22 сравнения — остатки о, и oC „ . Tpel тий выход дешифратора 21 является уп равляющим для схемы сравнения, при появлении единицы, на котором, что соответствует появлению единицы на обоих входах дешифратора ?1.„ включается в работу схема 22 сравнения.

Дешифратор 21, схема 22 сравнения и шифратор 20 для одного два.ячного разряда (для других — структура сох-. раняется) описываются соответственно табл.1-3.

При одновременном абнулении блоков 1 и 2 определение знака и послед-. него слагаемого о, производится пуГ тем сравнения величин м, и М,,для которых выполнение условия о, может быть только при о, = о, = О.

Но такая ситуация возникает только при приведении всего преобразователя в исходное состояние обнуление . Логика работы блока 6 исключает ложный сигнал при появлении такого состояния. Из табл ° 1 — 3 видно, что если

oC, = et, = О и на входах дешифратора две единицы, соответствующие одновре-: менно обнуленным блокам 1 и 2, то на выходах дешифратора все нули.

Коммутатор 7 выполнен любым известным способом, вариант соответствия управляющего кода и коммутируемых входов представлен в табл.3 так как выходы шифратора являются управляющими входами коммутатора.

Сумматор 8 накапливающего типа тактируемый.

В преобразователе (фиг.l) реализуется следующий алгоритм работы.

I 481898

Число Х „прi. дс T:isa.:tñ nr. в модулярном коле остатками но ОснованияM S.

5,...,8, т.е. (э э э рч) Дополнением числя Х, до величины

Р = Г S ° явпяется число Х, предо= ставленное в дополнительном коде по каждому основанию:

° ° э .м) Х = (Ы,,0,, Х + Х P

g;++I; = S, (2) Если к числу Х„прибавить М или

f к Х прибавить Ы, то полученные числя кратны Б;, т,е.

Х,=kS +i%

Х =n- < ) +ot о (4) где k, n — целые числа.

Приняв все числа Х, удовлетворя-. ющие условию

Р-1

0 (Х:< †вЂ, если Р нечетное, (5)

О

Р-1

+ 1 Х Р, если P нечетное, (6)

+ 1"й Х « Р, если P четное, отрицательными, получают симметричную СОК, т.е. удовлетворяющую условию

Х + Х = Р

lo!

5.

При условии (6) для четного Р в

СОК не входит число P/2, что нарушило бы симметрию.

Таким образом, если число Х, представленной в СОК, расположено в первой половине диапазона, то его дополнение находится ближе к P a расстояние равно Х = оГ, + S, k, Следовательно, преобразование закончится раньше для дополнительно кода.

Если Х расположено во второй половине, а его дополнение в первой, то

I минимальное расстояние равно Х

= ф., + 8, и, и преобразование заI кончится раньше для прямого кода.

Преобра. овятель работает следующим образом.

В исходном состоянии блоки 1, 2

5 и 8 обнулены, ня выходе 15 знака и выходе 14 нули.

Ня вход 10 подаются остатки (oC,, ь,...,e, ), представленные в двоичном коде. При подаче первого такто10 вого импульса на входы 16 и 19 проЬ исходит сложение остатков Ы; и Ы, в блоке 1 и остатков с4 и <, в блоке 2, Последующие тактовые импульсы на вход 19 не поступают, что соот15 ветствует подключению выходов мультиплексора 9 к входу 13 преобразователя. Начиная с второго, тактовые импульсы подаются с входа !8 и на сумматор 8, на первом информационном

20 входе которого присутствует число S<, а на втором "О". Следовательно, состояние сумматора 8 меняется S 2S

1S где 1 наименьшее из чисел

k u n. Ня величину Б„ увеличивается и состояние модульных сумматоров в блоках l.и 2„

Как только один из блоков 1 или 2 обнулится, то соответствующий блок

4 или 5 контроля обнуления выдает

З0 сигнал в блок 6 определения знака, который выдает на выход 15 информацию о знаке числа и подключает тот или иной вход коммутатора 7 к входу сумматора 8. Наличие единицы на первом

35 выходе блока 6 соответствует сигналу

Конец преобразования", по которому подача тактовых импульсов в блоки 1 и 2 прекращается, а в сумматор 8 подается еще один, по которому к вели40 чине 1S, подсуммируется величина с либо М и на выходе 14 получают uct комый результат. После этого происходит обнуление всех сумматоров и процесс преобразования начинается. снова.

45 Количество тактовых импульсов, подаваемых в блоки 1, 2 и 8 одинаково, > но поступающие на последний, задерживаются на один такт. Перевод муль" типлексора 9 происходит между первым

50 и вторым тактовыми импульсами, а обратно после последнего .

Дополнительный положительный эффект изобретения состоит в формировании знака числа.

Формула изобретения

1. Преобразователь чисел из модулярного кода в позиционный код, со1481898

/lE .pR 4ùèÉ пер ный бло к KoHTpo JIB QOHv ления, позиционцый сумматор, первый блок модульных накапливающих сумматоров и мультиплексор, причем информационный вход преобразователя соединен с входом первого слагаемого первого блока модульных накапливающих сумматоров, выход которого соединен с входом первого блока контроля обну- 10 ления, выход позиционного сумматора

Ф является выходом результата преобра"-.îíÿòåëÿ, первый, второй и третий гактовые входы которого соединены соответстВенно с тактовым входом перво- 15 го блока модульных накапливающих сумматоров, с тактовым входом позиционного сумматора и с управляющим входом мультиплексора, первый выход группы которого соединен с входом 20.

Второго слагаемого первого блока модульных накапливающих сумматоров, ".-..õîä установки в "0" которого соединен с входом установки в "Оп позиционного сумматора и является входом 25

;ачальной установки преобразователя, вход дополнительного кода остатка по младшему основанию-преобразователя

".оединен с первым информационным входом первой группы мультиплексора, первый информационный вход второй группы которого соединен с входом первого слагаемого позиционного сумматора и с входом значения младшего основания преобразователя, о т л и— ч а ю шийся тем, что, с целью повышения быстродействия, он содержит второй блок модульных накапливающих сумматоров, блок преобразования остатков из прямого кода в дополни- 10 тельный код, второй блок контроля обнуления, блок определения знака числа и коммутатор, причем информационный вход преобразователя соединен через блок преобразования ос- д татков из прямого кода в дополнительный код с входом первого слагаемого второго блока модульных накапливающих сумматоров, выход которого соединен с входом второго блока контроля обнуления, второй выход группы мультиплексора соединен с входом второго слагаемого второго блока модульных накапливающих сумматоров, вход установки в 0 и тактовый вход которого соединены с соответствующими входами первого блока модульных накапливающих сумматоров, входы первого и второго блоков контроля обнуления соединены соответственно с пер-. вым и вторым управляющими входами блока определения знака числа, первый и второй информационные входы которого соединены с входами дополнительного и прямого кода остатка по младшему основанию преобразователя соответственно, выходы блока определения знака числа являются выходом знака преобразователя и соединены соответственно с управляющими входами коммутатора, выход которого сбединен с входом второго слагаемого позиционного сумматора, вход донолнительного кода остатка по младшему основанию преобразователя соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с вторым информационным входом первой группы мульт:..Влексора и с входом прямого кода остатка по младшему основанию преобразователя, вход значения младшего основания которого соединен с вторым информационным .входом второй группы мультиплексора.

2. Преобразователь по п,1, о л и ч а ю шийся тем, ч-- блок определения знака числа. сорержит шиф ратор, дешифратор и схему сравнения, причем первый и второй управляющие входы, первый и второй информационные входы и выходы блока определения знака числа соединены соответственно с входами разрядов дешифратора, с первым и вторым информационными входами схемы сравнения и с соответствуюшими выходами шифратора, входы которого соединены соответственно с первым и вторым выходами дешифратора и с выходами схемы сравнения, вход разрешения которой соединен с третьим выходом дешифратора, Таблица 1

Депд фратор 21

Входы Выходы

1 2 1 2 3

0 0 0 0 0

0 1 1 0 0

1 0 0 1 0

1 1 0 0!

1481898

Таблица 2

Схема 22 сравнения

Входы

3 2 1 1 2

Таблица 3

Шифратор 23

Знак х, или Ы, Выходы

Входы

1 2 3 4 1. 2 3

О О О О О

l О О О 1 +

О 1 О О 1

О О 1 О 1 +

О О О 1 1

Составитель А.Клюев

Редактор M.Бланар Техред М.Дидык Корректор M. Васильева

Заказ 2702/57 Тираж 885 Подписно е . ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

О О О О

О О 1 О

О 1 О О

О 1 1 О

О О О

1 О 1 1

1 1 О О

1 1 1 О

О О

О О

О 1

1 О

1 1

О

О

О

О

О

О о а, о