Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретной информации и может быть применено в декодирующих устройствах аппаратуры передачи данных. Цель изобретения - повышение быстродействия и упрощение уа. Устройство содержит регистры 1<SB POS="POST">1</SB>÷1<SB POS="POST">D-1</SB>, блоки 2<SB POS="POST">1</SB>÷2<SB POS="POST">D-3</SB> элементов ИЛИ, первый и второй сумматоры 3, 4, блок 5 умножения, дополнительный регистр 6, коммутатор 7 и блок 8 управления, содержащий распределитель 9 импульсов и блоки 10.1÷10. (D-2) элементов И. 1 ил.

(51) 4 Н 03 М 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМ,Ф СВИДЕТЕЛЬСТВУ : ИБЗЗМ

OkTEHT!i -,q,,"„;:-,„:.;,,;

Б!; БЛ1-1(),,.:„.

+ 3 .хХх

1 хф, сока ссвктсних.

:-h Ф" --.- СОЦИАЛИСТИЧЕСКИХ х-х )--. РЕСПУБЛИК

=Ъ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫ ГИЯМ

ПРИ ГННТ СССР (21) 4292272/24-24 (22) 30.07.87 (46) 23,05.89. Бюл. М 19 (72) В.В.Квашенников, Г.П.Шведов и П.H.Þðêoâ (53) 621 ° 394.662(088.8) (56) Авторское свидетельство СССР

В 1116544, кл, Н 03 И 13/02, 27.04.83

t (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МНОГОЧЛЕНА ЛОКАТОРОВ СТИРАНИЙ ПРИ ДЕКОДИРОВАНИИ НЕДВОИЧНЫХ БЛОКОВЫХ КОДОВ (57) Изобретение относится к технике

„„SU„, 1481902 А 1

2 передачи дискретной информации и может быть применено в декодирующих устройствах аппаратуры передачи данных ° Цель изобретения — повышение быстродействия и упрощение устройства. Устройство содержит регистры

1,-1 1,, блоки 2„-2, элементов

И.И, первый и второй сумматоры 3, блок 5 умножения, дополнительный регистр 6, коммутатор 7 и блок 8 управления, содержащий распределитель

9 импульсов и блоки 10, — 10 1 элементов И. 1 ил.

14<11902

Изобретение относится к технике. передачи дискретно>г информации и Может быть применено в декодирующих устройствах аппаратуры передачи данных.

Цель изобретения — повышение быстродействия и упрощение устройства.

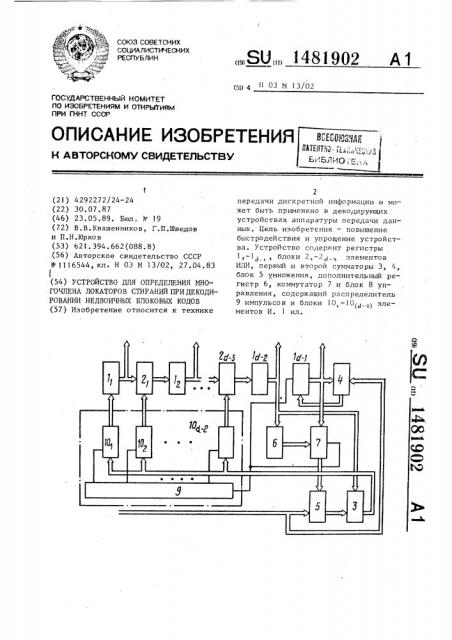

На чертеже представлена структурная электрическая схема устройства, 10

Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов содержит регистры 11 — 1),, блоки 2—

2),„ элементов ИЛИ, первый 3 и вто- 15 рой 4 сумматоры, блок 5 умножения, дополнительный регистр 6, коммутатор 7 и блок 8 управления, содержащий распределитель 9 импульсов и блоки 10 -101,) 1 элементов И. 20

Устройство работает следующим образoM.

Устройство вычисляет коэффициенты многочлена локаторов стираний

25 с)- (Q(Z) = ) ) (1+Х;. Z) .

11

Обрабатываемые локаторы стираний

Х;„последовательно поступают на вход устройства. Вычисления прово- 30 дятся по реккурентным формулам. Если за (k-1) шагов определен многочлен локаторов стираний ,, кк- ,Q„(Z=a„, Z +а, Е +...+a„Z+1, 35 то коэффициент многочлена локаторов стираний на К шаге

) ° ао а = а + Х

t к1

l к к к- 45

Для вычисления требуется провести

k операций сложения и (k-1) операций умножения в поле Галуа. Количество исправляемых стираний для кода не превышает (г)-)), где с1 — кодовое расстояние. Количество двоичных тактов при обработке каждого локатора стираний определяется числом операций умножения. Первый локатор стирания обрабатывается за один такт, второй также за один такт, третий — за два двоичных такта, четвертый — за три и т.д. В первьп такт обработки каждого локатор» стирания коммутатор

7 по!гключ л е 1 к Входу $ множителя 5 и поле Галуа выходы ггоследнего регистра ),, а в остальное время выходы довод IHтельного регистра 6.

Такой режим, работы коммутатора 7 определяется управляющим сигналом с первого выхода распределителя 9 блока 8 управления. Также по этому сигналу с первого выхода распределителя

9, поданному на первый тактовый вход последнего регистра 1),, осуществляется запись информации с выхода второго сумматора 4 в регистр

1) г

При обработке второго локатора стирания единичный сигнал с второго выхода распределителя 9 подан на пер- вые объединенные входы последнего блока 10(,) ) элементов И. При обработке (d — 2) локатора единичный .сигнал с (d-2) выхода распределителя 9 подан на первые объединенные входы второго блока 10 элементов И. При об— работке (d-) )-ro локатора единичный сигнал с (d-1) — го выхода распределителя 9 подан на входы первого блока

10, элементов И. B исходном состоянии все регистры 1 обнулены. Значение первого локатора стирания через вход и выход второго сумматора 4 записывается в регистр )g,, В остальные регистры 1,,, 1) записываются нули, так как на первые входы блоков

10 t,...)0г,),1 элементов И с выходов распределителя 9 подаются нулевые сиг- налы.

На первом такте обработки второго локатора его значение складывается в втором сумматоре 4 со значением первого локатора с выхода регистра 1, и полученная сумма записы1. ) - t вается в регистр 1) <, Одновременно значение второго локатора умножается в блоке 5 умножения в поле Галуа на величину первого локатора, поданного с выхода ком:-1утатора 7, полученное произведение складывается в сумматоре 3 с нулем с выхода регистра 11 и через блок )0 q элементов И записывается в регистр l d q . Обработка второго локатора стирания закончена. ч

Остальные локаторы стирания обрабатываются аналогичным образом. При этом при обработке остальных локаторов стирания на втором и следующих гактах работы на второй вход блока 5

1481902

Фор мул аизобретения вого сумматора.

Составитель С. Берестевич

P едак то р M. Блан ар Техр ед М. Дидык Корректор Т.Малец

Заказ 2702/57 Тираж 885 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1l3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент". r.Óæãoðîä, ул. Гагарина,101 умножения в поле lалуа подается пНформация с выхода дополнительного регистра б через коммутатор 7. Выход первого сумматора 3 по сигналам рас5 пределителя 9 поочередно через блоки ! О(1,..., ) 0 элементов И и блоки

2 g,...2, элементов ИЛИ подключается к входам регистров l 1< .

После обработки всех локаторов стира- 10 ний с выходов регистров 1<,,......,1<1 получают необходимый результат.

Вычисление первого и второго ко— эффицие IToB многочлена локаторов стираний осуществляется одновременно.

Такое построение устройства для определения многочлена локаторов стираний позволяет обработать (d-1) ло1 (d-1 (с1-2 ) катор стираний за " + 1

2 20 двоичных тактов вместо d(d-1)/2 в известном устройстве, т.е. íà (d 2) такта быстрее.

Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов, содержащее (Й-1) регистров, а — 3 бло- 30 ка элементов ИЛИ, дополнительный регистр, выходы которого соединены с первыми входами коммутатора, блок умножения, первые входы которого яв, ляются входами устройства, первый сумматор, выходы которого соединены с соответствующими входами блока управления, первый выход которого соедипен с вторым входом коммутатopc\ вторые выходы блока управления соединены с первыми входами соответствующих блоков элементов ИНИ, выходы которых соединены с входами соответствующих блоков элементов ИЛИ, выходы которых соединены с входами соответствующих регистров, кроме первого и (d-l)-го, выходы регистров, кроме (d-2} — го и (d — 1)-го, соединены с вторыми входами соответствующих блоков ИЛИ и являются первыми выходами устройства, третьи выходы блока управления соединены с соответствующими входами первого регистра, второй сумматор, о т л и ч à р щ е е— с я тем, что, с пелью повышения быстродействия и упрощения yc ðîéñòâà, первый вход (d-1)-го регистра подключен к первому в<ыходу блока управления, выходы (d-2)-го регистра соединены с входами дополнительного регистра, первыми входами первого сумматора и являются вторыми выходами устрбйства, выходы (d-1)-го регистра соединены с первыми входами второго сумматора, третьими входами коммутатора и являются третьими выходами устройства, вторые входы второго сумматора годключены к первым входам блока умножения, выходы второго сумматора соединены с вторыми входами (d-1)- го регистра, выхоцы коммутатора соединены с вторыми входами блока умножения, выхоцы которого соединены с вторыми входами пер