Устройство для сложения и вычитания чисел по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обработки дискретной информации, функционирующих в системах остаточных классов. Целью изобретения является повышение быстродействия. Поставленная цель достигается за счет совмещения во времени процессов определения местоположения операнда А и сдвига содержимого разрядов кольцевого регистра сдвига по значению операнда В. Для этого в устройство для сложения и вычитания чисел по модулю, содержащее вычислитель 5, блоки 7, 8, 25 элементов И, блоки 9, 16 элементов ИЛИ, приемный регистр 10, схему 11 сравнения, счетчик 12, дешифраторы 13, 27, группу элементов И 14, группу блоков 15 элементов И, элементы 21, 26 запрета, умножитель 22 частоты, кольцевой регистр 23 сдвига и группу элементов ИЛИ 28, введены счетчик 24 и шифратор 20 с соответствующими связями. 1 ил.

СОЮЗ СОВЕТСНИХ.

СОИИАЛИСТИЧЕСНИХ

РЕСПУБЛИК. (192 (21) А1

72 (59 4

ЮМШМ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGHOMV СВИДЕТЕЛЬСТВУ

Г(18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГХНТ СССР (21) 430/709/24-.24 (22) 18.09.87 (46) 30.05.89. Вюп. 9 20 (72) В.И.Глушков, В.А.Краснобаев, И.И.Курочка, А.И.Сахно и Г.М.Чугасов (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 1312572, кл. С 06 F 7/72, 1985.

Авторское свидетельство СССР

Ф 1257643, кл. С 06 F 7/72, 1984. (54) УСТРОЙСТВО ДЛЯ СЛОЖБНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУ)НО (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обра.ботки дискретной информации, функционирующих в системе остаточных классов. Целью изобретения является повы2 шение быстродействия. Поставленная цель достигается за счет совмещения во времени процессов определения местоположения операнда А и сдвига содер. жимого разрядов кольцевого регистра сдвига по значению операнда В. Для этого в устройство для сложения и вычитания чисел по модулю, содержащее вычитатель 5, блоки 7,8,25 элементов

И, блоки 9, 16 элементов HJIH, приемный регистр 10, схему 1 1 сравнения, счетчик 12, дешифраторы 13, 27, группу элементов И 14, группу блоков 15 элементов И, элементы 21, 26 запрета, умножитель 22 частоты, кольцевой регистр 23 сдвига и группу элементов

ИИИ 28, введены счетчик 24 и шифратор 20 с соответствующйми связями.

1 иле

1483450 .

Изобретение относится к области автоматики и вычислительной техники и может быть -использовано в системах и устройствах обработки дискретной информации, функционирующих в системе остаточных классов (СОК) .

Целью изобретения является повышение быстродействия.

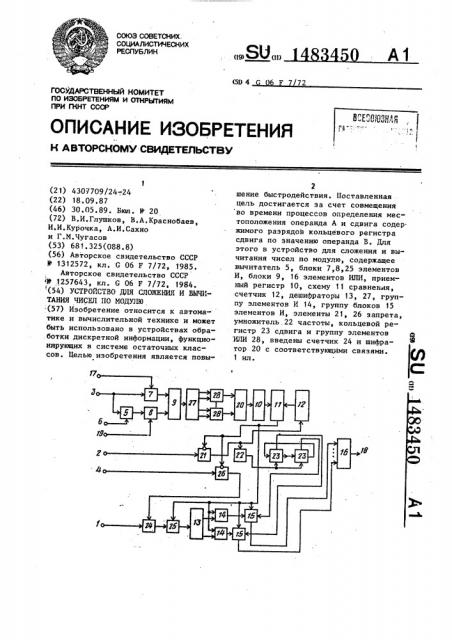

На чертеже представлена схема уст- ip ройства для сложения и вычитания чисел по модулю.

Устройство содержит второй информационный вход 1 устройства, первый тактовый вход 2 устройства, первый 15 информационный вход 3 устройства, второй тактовый вход 4 устройства, вычитатель 5, вход 6 значения модуля устройства, первый и второй блоки 7,8 элемента И, первый блок 9 элементов 2р

ИЛИ, приемный регистр 10, схему 11 сравнения, первый счетчик 12, первый дешифратор 13, группу элементов И 14, группу блоков 15 элементов И, второй блок 16 элементов ИЛИ, вход 17 25 задания операции сложения устройства, выход 18 устройства, вход 19 задания операции вычитания устройства, шифратор 20, первый элемент 21 запрета, умножитель 22 частоты, кольцевой ре- 3р гистр 23 сдвига, второй счетчик 24, третий блок 25 элементов И, второй элемент 26 запрета, второй дешифратор 27, группу элементов ИЛИ 28.

Алгоритм определения результата операции над числами А и В основан на использовании следующих математических соотношений:

А+В А +В =(А+В/2)+(В-В/2) для В чет1

НОГОТЬ,, В i B+i °, 40

А+В=А +В =(А+ )+(В- †-) для В

2 2 нечетного.

Результат операции модульного сложения и вычитания будет определяться операциями А,В, т.е. А+В=(А +В )modm. 45

Не нарушая Общности дальнейших рассуждений, будем считать, что В - неВ 1 t B+1 четно, тогда А =А+

2 2

В = —Устройство работает следующим об- 50 разом.

Исходное содержимое разрядов кольцевого регистра 23 сдвига соответствует содержимому первой стороны матрицы значений (A+B)modm. По входу 1

5S операнд А заносится в счетчик 24. По входу 3 операнд В поступает на вход вычитаемого вычитателя 5. В зависи-; мости от типа реализуемой устройством модульной операции операьд В (либо

B=m-В) .через блоки элементов И 7 (И 8), через блок элементов ИЛИ 9 поступает на вход дешифратора 27, с выхода которого значение В в унитарном коде через соответствующий элемент ИЛИ 28

1 поступает на В -"(В+1) (2-й вход шифратора 20, с выхода которого операнд

В в двоичном коде поступает в приемный регистр 10, С началом работы с входов, 2 и 4 устройства тактовые импульсы, сдвинутые друг относительно друга на такт, поступают на входы элементов 21 и 26 запрета.

С выхода умножителя 22 импульсы поступают на сдвигающий вход регистра 23, сдвигая в положительном направлении (против часовой стрелки) содержимое его разрядов на один раз ряд (n- äâîè÷íûõ разрядов; n=(log<(m-1)+1)) . В случае, когда в счетчиI

:ке 12 будет содержаться значение В

,содержимое разрядов регистра 23 сдвинется на В разрядов в положительном направлении, а в счетчике 24 будет содержаться операнд А =А+(В-1) /2 схема 11 сравнения выдает сигнал, который закрывает элементы 21, 26 запрета и открывает элементы И 14, блоки элементов И 15 и блок элементов

И 25, через которыю значение А с выхода счетчика 24 поступает на вход ! дешифратора 13, с А - ro выхода которого сигнал через А-й элемент И 14 открывает А -й блок элементов И 15, через который содержимое А -ro разряда регистра 23 поступает через блок элементов ИЛИ 16 на выход 18 устройства.

Формула изобретения

Устройство для сложения и вычитания чисел по модулю, содержащее вычитатель, три блока элементов И, два блока элементов ИЛИ, приемный регистр, схему сравнения, первый счетчик., первый и второй дешифраторы, группу элементов И, группу блоков элементов И, два элемента запрета, умножитель частоты, кольцевой регистр сдвига и группу элементов ИЛИ, причем первый информационный вход .устройства соединен с входом вычитаемого вычитателя и с первым входом пер" вого блока элементов И, выход которого соединен с первым входом первого блока элементов ИЛИ, второй вход которого соединен с выходом второго

1483450

Составитель А.Клюев

Редактор О.Спесивых Техред Л. Сердюкова Корректор M.Пожо

Заказ 2834/46 Типаж бб8 Подписное, ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 блока элементов И, первый вход которого соединен с выходом вычитателя, вход уменьшаемого которого соединен с входом значения модуля устройства, входы задания операции сложения и вычитания которого соединены соответственно с вторыми входами первого и второго блоков элементов И, выходы первого дешифратора соединены с пер- 1р выми входами соответствующих элементов И группы, выходы которых соединены с первыми входами соответствуницих блоков элементов И группы, выходы которых соединены с соответствующими 15 входами второго блока элементов ИЛИ, выход которого является выходом уст" ройства, выходы приемного регистра и первого счетчика соединены соответственно с первым и вторым входами 20 схемы сравнения, выход которой соединен с управляющими входами первого и второго элементов запрета, с вторыми входами элементов И группы и с вторыми входами блоков элементов И группы, 25 третьи входы которых соединены с выходами соответствующих разрядов кольцевого регистра сдвига, первый такI товый вход устройства соединен с информационным входом первого элемента 30 запрета, выход которого соединен с входом умножителя частоты, выход первого блока элементов ИЛИ соединен с входом второго дешифратора, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит второй счетчик и шифратор, причем второй информационный вход устройства соединен с информацион ым входом второго счетчика, выход которого соединен с первым входом третьего блока элементов И, выход которого соединен с входом первого дешифратора, выход первого элемента запрета соединен со счетным входом первого счетчика, выход схемы сравнения соединен с вторым входом третьего блока элементов И, выход второго элемента запрета соединен со счетным входом второго счетчика, втор и тактовый вход устройства соединен с информационным входом второго элемента запрета, выход умножения частоты сообщен с входом разрешения сдвига кольцевого регистра сдвига, выходы первой и второй групп второго дешифратора соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с входа" ми шифратора, выход которого соединен с входом приемного регистра.