Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

Изобретение относится к усилительной технике и может быть использовано в качестве приемника электрических сигналов из кабельной магистрали. Цель изобретения - увеличение коэф. ослабления синфазного сигнала (КОСС). Усилитель содержит дифференциальный каскад 1, выходной каскад 2 на транзисторе 3, выходной каскад 4 на транзисторе 5 и введенные резистивный делитель 6 и эммитерные повторители (ЭП) 7 и 8. Так как между каскадами включены ЭП 7,8, то удается увеличить суммарный коэф. усиления по сравнению с прототипом. Включение ЭП 7, 8 однозначно определяет режимный ток транзисторов 3 и 5. Подключение объединенных баз транзисторов 3,5 к средней точке делителя 6 приводит к уменьшению коэф. передачи синфазного сигнала по сравнению с прототипом, т.обр., увеличивается и КОСС. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (191 (11) А1 (51)4 Н 03 F 3/45

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н д BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ fKHT СССР (21) 4317125/24-09 (22) 01.09.87 (46) 30..05.89. Бюл. Р 20 (72) О.И.Зайцев, 6.0.Коньков и В.P.Èâàðöáåðã (53) 621.375.024(088 ° 8) (56) Патент CIJA Ф 4600893, кл. Н 03 F 3/45, 1986. (54) ДИФФЕРЕИ ИАЛЪНИЙ УСИЛИТЕЛЬ (57) Изобретение относится к усилительной технике и может быть использовано в качестве приемника электрических сигналов иэ кабельной магистрали. Пель изобретения — увеличение коэф. ослабления синфазного сигнала (КОСС). Усилитель содержит дифферен2 циальный каскад 1, выходной каскад 2 на транзисторе 3, выходной каскад 4 на транзисторе 5 и введенные резистивный делитель 6 и эмиттерные повторители (ЭП) 7 и 8. Т.к. между каскадами включены ЭП 7,8, то удается увеличить суммарный коэф.усиления по сравнению с прототипом. Включение

ЭП 7,8 однозначно определяет режимный ток транзисторов 3 и 5. Подключение объединенных баз транзисторов

3,5 к средней точке делителя 6 приводит к уменьшению коэф,передачи синфазного сигнала по сравнению с прототипом, т.обр., уве:;и п вается и

КОСС. 1 ил.

1483602

Изобретение относится к усилительной технике и может быть испольСоставитель Ю. Рогаткин

Редактор H. Киштулинец Техред М.Ходанич Корректор Л. Пилипенко

Заказ 2850/54 Тираж 884 Подпис но е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

11303 5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãîpîä, ул. Гагарина,101 зовано в качестве приемника электри— ческих сигналов из кабельной магистрали.

Цель изобретения — увеличение коэффициента ослабления синфазного сигнала (КОСС) .

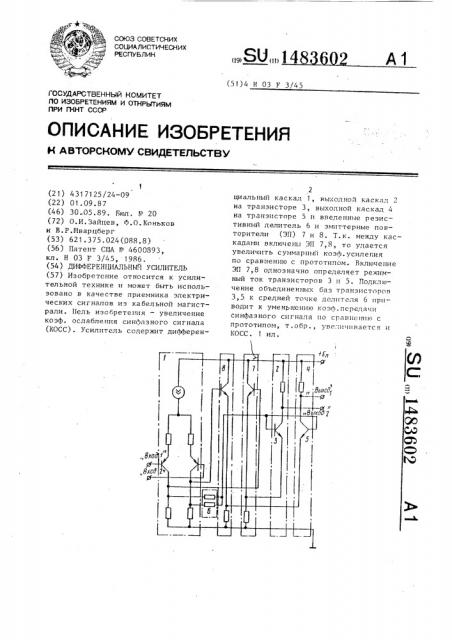

На чертеже приведена принципиаль10 ная электрическая схема дифференциального усилителя.

Дифференциальный усилитель содержит входной дифАеренциальный каскад (ДК) 1, первый выходной каскад 2 на первом транзисторе 3, второй выходной каскад 4 на втором транзисторе 5, резистивный делитель 6, первый 7 и второй 8 эмиттерные повторители (ЭП).

Дифференциальный усилитель работает следующим образом.

Дифференциальный сигнал усиливается входным ДК 1 и выходными каскадами 2 и 4. Поскольку между ними включены развязывающие ЭП 7 и 3, уда- 25 ется увеличить суммарный коэффициент усиления по сравнению с прототипом.

Одновременно включение ЭП 7 и 8 однозначно определяет режимный ток пер30 вого 3 и второго 5 транзисторов первого 2 и второго 4 выходных каскадов.

Подключение объединенных баз первого 3 и второго 5 транзисторов к средней точке резистивного делителя

6 приводит к уменьиению коэффициента передачи синфазного сигнала по сравнению с прототипом, таким образом, увеличивается и КОСС.

Формул а изобретения

Дифференциальный усилитель, содержащий последовательно соединенные входной дифференциальный каскад, первый и второй выходные каскады на первом и втором транзисторах соответственно, включенных по схеме с общей базой, базы которых объединены, о т- л и ч а ю шийся тем, что, с целью увеличения коэффициента ослабле— ния синфаэного сигнала, между входным дифференциальным каскадом и первым и вторым выходными каскадами введены первый и второй эмиттерные повторители соответственно, а между выходами входного дифференциального каскада введен резистивный делитель, к отводу которого подключены базы первого и второго транзисторов.