Многоканальный дискретно-аналоговый фильтр

Иллюстрации

Показать всеРеферат

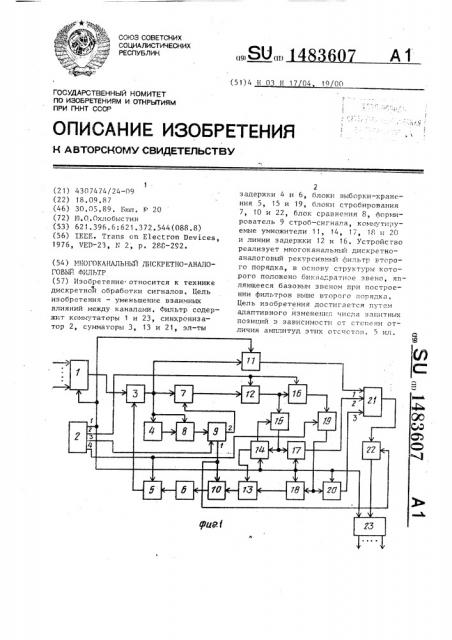

Изобретение относится к технике дискретной обработки сигналов. Цель изобретения - уменьшение взаимных влияний между каналами. Фильтр содержит коммутаторы 1 и 23, синхронизатор 2, сумматоры 3, 13 и 21, эл-ты задержки 4 и 6, блоки выборки-хранения 5, 15 и 19, блоки стробирования 7, 10 и 22, блок сравнения 8, формирователь 9 строб-сигнала, коммутируемые умножители 11, 14, 17, 18 и 20 и линии задержки 12 и 16. Устройство реализует многоканальный дискретно-аналоговый рекурсивный фильтр второго порядка, в основу структуры которого положено биквадратное звено, являющееся базовым звеном при построении фильтров выше второго порядка. Цель изобретения достигается путем адаптивного изменения защитных позиций в зависимости от степени отличия амплитуд этих отсчетов. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51)4 Н 03 И 17 04 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (? 1) 4307474/24 — 09 (22) 18.09.87 (46) 30,05,89. Г)юл. Р 20 (72) 10.0.Охлобыстин (53) 621.396.6:621.372.544(088.8) (56) IEEE. Trans on Electron Devices, 1976, VED-23, 1 ?, p. 288-292. (54) МНОГОКАНАЛЬНЬЙ ДИСКРЕТНО-АНАЛОГОВЫЙ ФИЛЬТР (57) Изобретение относится к технике дискретнои обработки сигналов. Цель изобретения — уменьшение взаимных влияний между каналами. Фильтр содержит коммутаторы 1 и 23, синхронизатор 2, сумматоры 3, 13 и 21, эл-ты

2 задержки 4 и 6, блоки выборки-хранения 5, 15 и 19, блоки стробирования

7, 10 и 22, блок сравнения 8, формирователь 9 строб-сигнала, KoMIp,-ònðóемые умножители 11, 14, 17, 18 и 20 и линии задержки 12 и 16, Устройство реализует многоканальный дискретноаналоговый рекурсивный фильтр второго порядка, в основу структуры кото— рого положено биквадратное звено, являющееся базовым звеном при построении фильтров выше второго погядка °

Цель изобретения достигается путем адаптивного изменения числа зашитных позиций з зависимости ст степени отличия амплитуд этих отсчетов, 5 ил.

1483607

Изобретение относится к технике дискретной обработке сигналов и может использоваться в электросвязи, автоматике и измерительной технике для

5 фильтрации аналоговых сигналов, поступающих по независимым каналам с различными характеристиками канальных фильтров.

Цель изобретения — уменьшение вза- 1г

1.) имных влияний между каналами путем адаптивного изменения числа защитных позиций в зависимости от степени отличия амплитуд этих отсчетов.

На фиг.1 представлена блок-схема предлагаемого многоканального дискретно-аналогового фильтра; на фиг.2— временные диаграммы, поясняющие работу предлагаемого устройства, на фиг.3 — пример реализации блока срав- 20 нения, на фиг.4 — пример построения формирователя стробирования на фиг.5 — один из возможных вариантов построения синхронизатора.

Многоканальный дискретно-аналого- 25 вый фильтр содержит (фиг.1) первый коммутатор i, синхронизатор 2, первый сумматор 3, первый элемент 4 задержки, первый блок 5 выборки-хранения (БВХ), второй элемент 6 задержки, первый блок 7 стробирования, блок 8 сравнения, формирователь 9 строб-сигнала, второй блок 10 стробирования, первый умножитель 11 (коммутируемый), первую линию 12 задержки (ЛЗ), третий сумматор 13, второй умножитель (коммутируемый) 14, второй

15 БЕХ, вторую 16 ЛЗ, третий 17, четвертый 18 умножители (коммутируемые), третий 19 БВХ, пятый умножитель 20 (коммутируемый), второй сумматор 21, третий блок 22 стробирования, второй коммутатор 23.

Блок сравнения 8 содержит (фиг.3) выпрямители 24,«компаратор 25, коммутаторы 26 и 27, блок 28 иэ и аттенюаторов, компаратор 29, сумматор 30, схемы 3 1 и 32 совпадения, реверсивный сумматор 33 (счетчик).

Формирователь строб-сигнал" содержит (фиг.4) двоичный счетчик 34, коммутаторы 35 и 36.

Синхронизатор содержит (фиг.5) тактовый генератор 37, делитель на два 38, делитель 39 на (1+1) делитель на два 40, счетчик на (И+1) 41 и одновибратор 42.

Предлагаемый многоканальный дискретно-аналоговый фильтр работает следующим образом..

Уплотненная во времени последовательность (U, фиг.2а) отсчетов входных сигналов формируется коммутатором 1 как схематически показано на фиг.2я, для случая N = 4. Цифрами ня с фиг,2а обозначен номер к-".наля, отсчет которого подключается на выход коммутатора в данном тактовом интервале Т., периодичность выборки отсчеI тов одного канала равна периоду дискретизации Тд и одинакова для всех каналов. Один из тактовых интервалов (обозначенный на фиг.2а цифрой О) оставлен незаполненным (для реализации этого, например, последний вход коммутатора 1 может бь;ть заземлен), что, как будет пока=-яно ниж †. необходимо для обеспечения во:..можности адаптивного изменения числа защитных

Позиций при сохранении с..нхронности работы всех блоков устройства, В соответствии -. Ьи. .:я частота следования отсчетов сигналов на выходе коммутатора 1 равна (М+!) Т „ .

Тогда„ еслг с целью ум;н. :."ения взаимных влияний ме ду каналами введено

N1 защитных позиций на один цикл дли.тельностью 1 @ (при ран :э. .эрном распределении числа позиц и это соответствует 1 защитным позициям между каждой парой смежных отсчетов, ВВо димьх в линии 12 и 16 задержки, то частота сдвига линий задержки равна „, = (1 + 1) . (И + 1) -;" .

Один иэ возможных вариантов структуры входного или выходного сигналов линий 12 и 16 задержки при 1 = 4 показан на фиг.2n (U „ ). В данном случае отсчеты, подлежащие обработке, следуют на первых иэ 1+1 позиций на каждом интервале, длительностью Т. (i = 1, 2...), В устройстве исполь"овяны две линии 12 и 16 задержки, обеспечивающие сдвиг отс---:.-ов соответств=-нно на

N(1+1) и (N ->)(1+1) интервалов, длительностью Г „,, В соответствии с целью пре,;лага=:мого изобр-=тения структура выходного сигнала сумматора 3 перед вводом в первую линию

12 задержки на (1+И) (1+1) периодов

-1

Гд должна быть изменена в соответствии со степенью отличия смежных отсчетов: если П;+,- " Г;, тп число защитных позиций 1. м-.лу этими отсче1483607,5

15

25 тами может быть уменьшено или оставлено без изменения, если И П., 1+< 1 то число 1 в данном случае желательно увеличить. С этой целью выходной сигнал U,, (фиг.2б) сумматора 3 подается на первый элемент 4 задержки, обеспечивающий задержку Отсчета на

Т.; выходной сигнал первого элемента

4 задержки показан на фиг.2в, Входной и выходной сигнал первого элемента 4 задержки подается на входы блока 8 сравнения, в котором определяется, какой из входных отсчетов больше (предыдущий Ь ; или I,, последующий) и оценивается, во сколько раз больший отсчет превышает меньший.

На основании сравнения модулей входньгх отсчетов П;, Б., сформирован! 1+1 ных выпрямителями 24) компаратор 25 принимает решение, какой из отсчетов больше, в соответствии с чем на выход коммутатора 26 проключается меньший из отсчетов, а на выход коммутатора 27 — больший, который подается на блок 28 из и аттенюаторов, Па каждом последующем отводе блока 28 вносится большее ослабление выходного сигнала коммутатора 27, чем на предыо дущем, поэтому сигнал на выходах компараторов 29 содержит, как правило, несколько нулей и несколько единиц, причем, чем больше единиц содержится на выходах компараторов 29, тем в большей степени отличаются модули отсчетов U;, Б .. . и, наоборот, чем

1, больше нулей и меньшей един щ в выходных сигналах компараторов 29, тем меньше степень отличия модулей указанных отсчетов. В соответствии с приведенной на фиг,3 схемой включения схем 3 1 и 32 совпадения и реверсивного сумматора 33 выходной сигнал сумматора 33 выходной сигнал сумматора 30, вычисляющего число единиц на выходах компаратора 29, может быть подан на вход прямого либо на вход обратного счета реверсивного сумматора 33, в первом случае двоичное число ча выходе реверсивного сумматора 33 увеличивается на число единиц, присутствующих на выходах компаратора 29 на данном интервале, во втором случае соответственно уменьшается. Выходы нескольких старших разрядов реверсивного сумматора 33 подаются далее на вход формирователя 9 строб-сигнала, который выбирает, на какой из 1+1 тактовых позиций в дан30

55 ном интервале Т. необходимо подать

i выходной сигнал сумматора 3 . на первую. линию 12 задержки. Формирователь 9 строб-сигнала может быть выполнен, например, как показано на фиг.4, на базе двоичного счетчика 34, циклически просчитывающего 1+1 импульсов, поступающих с третьего в»в ода синхронизатора 2, и обеспечивающего управление коммутатором 35, который формирует на своих выходах сигналы Х1-Х5 (фиг.2 д-н). Коммутатор 36, управляе- мый выходным сигналом блока 8 сравнения, обеспечивает выбор одного из сиг. налов Х1-Х5 для подачи на управляющий вход блока 7 стробирования. Поэтому в зависимости ОT величины отсчета У„ последующий отс-Ie-. Г, мо + 1 жет быть подан на вход линии 12 за— держки на любОй тактОвой пОзиции дан ного интервала

Сказанное можно пояснить на следующем примере.

Как видно из фиг.2б, на выходе сумматора 3 1, - 1",, поэтому в результате сравнения Отсчетов П, II в блоке 8 сравнения на прямом выходе компаратора 25 (фиг.3, выход 11 появляется единица, разрешающая работу реверсивного сумматора 33 в режиме прямого счета, Так как l.„ 1 .„ то на выходах компараторов 29 (фи.-,3) появляется значительное число единиц и двоичное число на выхсде регсрсивного сумматора 33 существенно увеличивается.

В предлагаемом устройстве испол"зован следующий алгоритм выбора тактовых позиций: чем больше двоичное число на выходе реверсивного сумматора 33 (т.е. на выходе блока 8 сравнения), тем ближе расположен строб— импульс, выдаваемый формирователем 9, строб †сигна к концу данного интервала Т (число защитных позиций между

1 отсчетами, подаваемыми на вход линии

12 задержки, увеличивается), и, наоборот, с уменьшением двоичного числа на выходе блока 8 сравнения стробирующий импульс смещается к началу данного интервала (число защитных позиций уменьшается). В рассматриваемом случае (U v U 2) число на выходе блока 8 сравнения увеличивается и формирователь 9 строб-сигнала выбирает последовательность Х р (фиг,2д-н) с большим индексом P (с большей задержкой), чем в предыдущем интервале, 1483607 например Х (фиг,2д). В этом слУчае выходной отсчет И первого суммато2 ра 3 поступает на вход линии задержки на четвертую тактовую позицию интервала Т (фиг. 2r ) . В данном случае

1 может быть выбрана и другая позиция, например Х или Х, (фиг. 2ж, и) . Это

3 зависит от того, во сколько раз отличаются отсчеты U, U и соответствен- 10 но насколько сильно изменилось двоичное число на выходе блока 8 сравнения в начале интервала Т . Важно то, что задержка отсчета относительно начала интервала Т введена и число защитных позиций увеличивается.

Следующий отсчет U (фиг.26),.как, показано на фиг.26, мало отличается от предыдущего (U > " U <), В этом cvy ае двоичное число на выходе блока 8 сравнения практически не изменяется (так как число единиц на выходах компараторов 29 (фиг.3) мало), и на ин" тервале Т выбирается та же тактовая позиция, что и на предыдущем интер вале Т (формирователь 9 строб-сигнала подает на управляющий вход блока . стробирования сигнал Х (фиг.2,о)).

Следующий отсчет lJ (фиг.26) больше предыдущего (U < > U ), поэтому вли- 30 яние отсчета U на П„мало, и число защитных позиций между ними может быть уменьшено. В этом случае двоичное число на выходе блока 8 сравнения уменьшается, формирователь 9 строб-сигнала выбирает последователь35 ность Х с меньшим индексом Р, чем в предыдущем интервале Т, например

Х (фиг.2ж), В этом случае, хотя модули отсчетов заметно отличаются и число единиц на выходах компараторов 29 (фиг.3) велико, компаратор 25 (фиг.5) выдает единицу уже на своем инверсном выходе (так как U4 > U ) и выходной сиг45 нал сумматора 30 (фиг.3) поступает уже на вычитающйй вход (вход обратного счета) реверсивного сумматора 33 (фиг.3).

Соответствующий приведенным выше .примерам сигнал на выходе блока 7 стробирования и на выходе линии 12 задержки приведен на фиг.2г (сигнал

U„ ). Из фиг.2г видно, что число защитных позиций между смежными отсче-тами U; U;+„ ïåðåä вводом в линию

12 задержки увеличилось при U; U;„„, не изменилось (или мало изменилось) при U = U;. и уменьшилось при

И . а U т. е. распределение защитных позиций приблизилось к оптимальному.

Входные сигналы линий 12 и 16 задержки подаются на входы блоков 15 и 19 выборки-хранения, осуществляющих запоминание величин отсчетов до конца текущего интервала Т;. В данном случае каждый такой Ьлок может быть выполнен просто в виде пикового детектора, сбрасываемого в начале каждого интервала Т,. Выходные сигналы блоков 15 и 19 выборки †хранен поступают на входы коммутируемых умножителей 14, .17, 18, 20 соответственно, каждый из которых может быть выполнен, например, в виде коммутатора, N выходов которого подключены к взвешивающим резисторам„ включеннык на входе операционно i.,:."ил.:толя. Па данном интервале Т ;.аждый кзмкутатор умножителей 11, .4, 17 18, 20 обеспечивает подключение взвешивающих резисторов, определяющих соответствующие весовые козффициен ь именно для того канала, отсчеты кото опo obpa6avb>aaexcs на данном временном интернале т;, В соотве.: т ии со с.; у . урой биквадратного звена второго порядка, на основе которой построено предлагаемое устройство, выходные сигналы умножителей 14 и 18 должны быть поданы на первый сумматор 3, для чего эти сигналы предварительно складываются в третьем сумматоре 13. Благодаря наличию блоков 15 и 19 выборки-хранения полученные на данном интервале Т, результаты умножения сохраняются до к. конца текущего интервала Т;, в связи с чем возможно стробирование выходного сигнала третьего сумматора 13 на последней тактовой позиции текущего интервала Т . с помощью второго бло1 ка 10 стробирования, управляющим сигналом для которого коже f служить, например, по=ледний из сигналов Х (при

1 = 5 — слгнал Х фиг.2и).- После ука5 эанного стробирования сигнал задерживается вторым элементом 6 задержки на длительность одной тактовой позиции Т,1+;), за счет чего результат умножения переносится в начало следующего интервала Т;„, после чего запоминается с помощью первого блока 5 выборки-хранения на весь интервал

T . Примеры выходных сигналов тре1 4 тьего сум;-атора 13, второго блока 10

1483607

10 стробиравания, второго элемента 6 задержки и первого блока 5 выборки-хранения приведены соответственно на фиг. 2к-н (снгналы U „, 11, <, Б, вв, .5

11Б в )

Перенос результатов умножений в интервале Т; на следующий интервал

Т;,, необходим для обеспечения выбора произвольной тактовой позиции, на которой отсчет может быть передан в первую линию 12 задержки. Без вве-. дения указанного процесса возможен, например, следующий случай: результат умножения появился на соответствую- 15 щем входе первого сумматора 3 лишь на последней тактовой позиции интервала Т., в этом же интервале этот

1 результат, сложенный с входным отсчетом, должен быть снова подан на 20 первую линию 12 задержки. Очевидно, что независимо от решения, принятого блоком 8 сравнения, этот результат может быть введен, в первую линию 12 задержки только на той же последней тактовой позиции интервала Т;, поскольку время остальных тактовых позиций уже истекло.. Для обеспечения синхронности работы устройства при введении указанного сдвига результа- 30 тов умножений, естественно, необходимо соответствующим образом видоизменить временную структуру выходного сигнала первого коммутатора 1. С этой целью и был введен незаполненный временной интервал в конце каждого цикла длительностью Т, обозначен,ый на фиг,2а цифрой О, Как видно из фиг.2а,н, введение указанного сдвига обеспечивает строгую синхрон- 40 ность проявления отсчета i-ro канала на выходе первого коммутатора 1 (U „, фиг.2а) и результата обработки предыдущих отсчетов этого же канала на выходе первого блока 5 выборки-хране- 45 ния (Б йиг.2 ), Выходные сигналы коммутируемых умножителей 11, 17 и 20 складываются во втором сумматоре 21. Поскольку выходные сигналы умножителей 17 и 20 аналогичны сигналу 1с в (фиг.4к) и могут заполнять на весь текущий интервал Т; (но обязательно присутствуют на последней тактовой позиции этого интеРвала), ."о для выравнивания длительностей периодов дискретизации в каждом канале на выходе устройства вводится стробирование выходного сигнала второго сумматора 21 последней тактовой позицией каждого интервала

Т; (при 1 = 4, например, возможно стробирование сигналом Х, для фиг.2и), что осуществляется третьим блоком 22 стробирования, выходной сигнал которого показан на фиг.20. С целью выделения обработанных фильтром последовательностей отсчетов каждого канала выходной сигнал третьего блока 22 стробирования подается на второй коммутатор 23, аналогичный входному коммутатору, но включенный наоборот (как демультиплексор).

Таким образом, предлагаемое устройство реализует много-.;анальный дискретно-аналоговый рекурсивный фильтр второго порядка. В основу структуры фильтра положено биквадратное звено, являющееся базовым звеном при построении фильтров выше второго порядка. Кроме того, исключая из блок-схемы фиг.1 все звенья, расположенные между блоками (например, 15, 19) выборки-хранения и входом сумматора 3, и, увеличивая соответствующим образом число линий задержки и умножите.— лей, на основе предлагаемого устройства можно реализовать также и нерекурсивгый многоканальный c ëëüòð произвольного порядка.

На фиг.5 приведен пример построения синхронизатора " на базе тактового генератора 37, формирующего на выходе меандр частоты (N+1) (1+1)Т вЂ” ф которая после деления на 2 делителем 38 в прямой.и инверсной форме подается на тактовые входы линий 12 и 16 задержки (имеется в виду, что эти линии построены на двухфазных

ПЗС). На делителе 39 на 1+1 и одновибраторе 42 формируются в начале каждого интервала Т короткие импульсы, обеспечивающие сброс блоков 5, 15, 19 выборки-хранения. С помощью делителя 40 на два и двои- ного счетчика 4 1 (циклически просчнтывающего

N+1 импульс) формируются адресные сигналы в виде периодически повторяющегося набора двоичных кодов для управления коммутаторами 1 н 23 и умножителями 11, 14, 17, 18 и 20.

Сигнал с прямого выхода делителя 38 на два подается на формирователь 9 строб-сигнала, Формула изобретения

Многоканальный дискретно — аналоговый фильтр, содержащий синхронизатор, 1483607 последовательно соединенные первый коммутатор, входы которого являются входами многоканального дискретноаналогового фильтра, первый сумматор, 5 первый умножитель и второй сумматор„ к второму и третьему входам которого подключены соответственно выходы третьего умножителя, к входу которого подключен вход второго умножителя, и пятого умножителя, к входу которого подключен вход четвертого умнох,и-. теля, а к управляющим входам первого коммутатора, первого — пятого умножителей, второго коммутатора, заходы которorо являются выходами многока, нального дискретно-аналогового фильт-, ра, годключен первый выход синхронизатора, второй выход которого подключен к тактовым входам последовательно соединенных первой и второй линий задержки, отличающийся тем, что, с целью уменьшения взаимных влияний между каналами путем адаптивного изменения числа защитных 25 позиций в зависимости от степени с-личия амплитуд этих отсчетов, введены первый блок стробирования, выход которого подключен к информационному входу первой линии задержки,. поспедо- 1 вательно соединенные первый элемент задержки, блок сравнения, к второму входу которого, входу первого э.-.::мента задержки и первому входу первого блока стробирования подключен выход первого сумматора, и формирователь строб-сигнала, второй выход которого подключен к управляющему входу первого блока стробирозания,, а между вторым входом первого сумматора и выходом четвертого умножителя введены последовательно соединенные третий сумматор, к второму входу которого подключен выход второго умножителя, второй блок стробирования, к управляющему входу которого подключен первый выход формирователя строб-- -.игнала, второй элемент задержки и первый блок выборки-хранения, между выходом первой линии задержки и входом второго умножителя BBp ен BTGpc. блок выборки-хранения, между зьс.одом второй линии задержки и r.х::.:. че е.зтого умножителя введен третий блок выборки-хранения,,между вь.x ы:;."м второго сумматора и входом зторог< коммутатора введен третий блок стробирования, к упразляьщему зх- !у к .. . ого по,клю чен цервь и выход формирователя стробсигнала, к управляющему входу которого подклю-.ен третий Bf:L.;ñ;:, синхронизатора ч.. .г -.тий зьа,, .: рс го подключен к управляющим входам перзсBTopor0 H третьег )J:o!:.os Hbl6opzv-хранения.

1483607

Фиг, Ч

1483607

Составитель Л.Тимошина

Техред М. Ходанич Корректор М.Васильева

Редактор Н.Кинтулинец

Заказ 2850/54 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, R-35, Раувская наб. д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул:. Гагарина, 101