Преобразователь импульсов

Иллюстрации

Показать всеРеферат

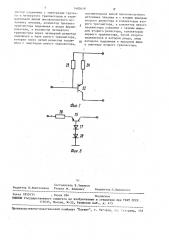

Изобретение относится к вычислительной технике и микроэлектронике, в частности к высоковольтным интегральным формирователям для управления нелинейными элементами. Целью изобретения является уменьшение потребляемой мощности и повышение быстродействия. Для достижения этой цели в устройство дополнительно введены форсирующий блок, второй и третий согласующие элементы. На чертеже показаны: RS Триггер 1, первый согласующий элемент 2, формирователь 3 выполненный на транзисторах 4 и 5 N - P - N - типа проводимости диод 6, резисторы 7, 8, 18, 19 и 20, выходная шина 21. Источник 9 питания, форсирующий блок 10, второй и третий согласующие элементы 11 и 12, входные шины 13 и 14, транзисторы 16 и 17 форсирующего блока 10. Резкое сокращение фронта нарастания выходного сигнала достигается за счет уменьшения времени выключения выходного формирователя 3. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) (51) 4 H 03 К 5/156

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

21 код

СС

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

llO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

Н А ВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ (21) 4107739/24-21 (22) 22.08,86 (46) 30.05.89. Бюл, л"- 20 (72) Б.А.Гарбуз, В.И.Громов и С,А.Коновалов (53) 621.373 (088.8) (56) Гребен А.Б. Проектирование аналоговых интегральных схем. — N.:

Энергия, 1976. с.131 рис.6-7б, ЭАТА ВООК. 811Т-503.формы "Spraque", 1984, с.5r49 (микросхема HCS-4801Н). (54) ПРЕОБРАЗОВАТЕЛЬ ИИПУЛЬСОВ (57) Изобретение относится к вычислительной технике и микроэлектронике, в частности к высоковольтным интегральным формирователям для управления нелинейными элементами. Целью изобретения является уменьшение потребляе2 мой мощности и повышение быстродействия. Для достижения этой цели в устройство дополнительно введены форсирующий блок, второй и третий согла сующие элементы. На чертеже показаны:

PiS-триггер 1, первый согласующий элемент 2, формирователь 3, выполненный на транзисторах 4 и 5 и-р-п-типа проводимости диод 6, резисторы 7, 8, 18, 19 и 20, выходная шина 21, источник

9 питания, форсирующий блок 10, второй и третий согласующие элементы 11 и 12, входные пины 13 и 14, транзисторы 16 и 17 форсирующего блока 10.

Резкое сокращение фронта нарастания выходного сигнала достигается за с ет «а уменьшения времени выключения выходного AopMHpoBBTeëÿ 3. 3 HJI, 1483619

Изобретение относится к вычислительной технике и микроэлектронике, в частности к высоковольтным интегральным формирователям для управле5 ния нелинейными элементами, Цель изобретения — уменьшение потребляемой мощности и увеличение быстродействия.

На фиг. 1 — электрическая принципиальная схема устройства; на фиг,2 и 3 — возможные варианты согласующих элементов.

Преобразователь импульсов содержит RS-триггер 1, выход которого че рез первый согласующий элемент 2 подключен к входу формирователя 3, -вы- . полненного на первом 4 и втором 5 транзисторах и-р-и-типа проводимости, диоде 6, первом 7 и втором 8 резисто- 2п рах, причем база первого транзистора

4 соединена с входом формирователя 3 и через первый резистор 7 — с эмиттером первого транзистора 4 и отрицательной шиной высоковольтного источ- 25 ника 9 питания, а база второго транзистора 5 соединена с первым выводом второго резистора 8; форсирующий блок

10, второй 11 и третий 12 согласующие элементы, причем вход второго согласующего элемента 11подключен к первой . входной шине 13 и первому входу RS-триггера 1, а выход — к первому входу формирователя 3, вход третьего согласуюцего элемента 12 подключен к второму входу RS-триггера 1 и второй входной шине 14, а выход — к входу форсируюцего блока 10, который выполнен на третьем 15 и четвертом 16 транзисторах . n-р-п-типа и пятом О транзисторе 17 р-п-р-типа; третьем

18, четвертом 19, пятом 20 резисторах, причем третий 15 и четвертый

16 транзисторы имеют общую базу и подключены к входу форсирующего блока 10 и через третий резистор 18 ñîåдинены с эмиттерами третьего 15 и четвертого 16 транзисторов и с отрицательной шиной высоковольтного ис-= точника 9 питания, коллектор третьего транзистора 15 подключен к входу формирователя 3, а коллектор четвертого транзистора 16 через четвертый резистор 19 подключен к базе пятого транзистора 17, которая через пятый резистор 20 соединена с эмиттерам

55 пятого транзистора 17, с положительной шиной высоковольтного источника

9 питания и с вторым выводом второго резистора 8 и коллектором второго транзистора 5, а коллектор пятого транзистора соединен с первым выводом второго транзистора 8, коллектором первого транзистора 4, базой второго транзистора 5 и катодом диода

6, анод которого подключен к выходной шине 21 и эмиттеру второго транзистора 5.

На фиг. 2, 3 представлены возможные варианты согласующих элементов

2, 11 и 12 для случаев: фиг. 2 — построение RS-триггеров на элементах

И: транзистор 22, резисторы 23 и 24; на фиг. 3 — построение RS-триггеров на элементах ИЛИ:- транзистор 25, резистор 26, диоды 27 и 28.

Устройство работает следующим образом.

Пусть триггер построен н " лементах И, тогда при подаче на R-вход установки его в нуль ("0 ") на выходе

RS-триггера формируется уровень "0", который через согласующий элемент 11 (фиг.i) задает ток в ба-"..: транзистора 4 формирователя 3, примерно равный

0gb т влекл эл- та и skw. эл--:а И

+ t

На S-вход 1<5-триггера в это время подается уровень "1 " !,одновременная

n LT эв.т; " . . .. «9" кт R

У

2 где Е в — напряжение питания логической -части; .- прямое падение напряжения на базе-эмиттерном переходе транзистора 22 (фиг.2); и ве, U вх "о" уровень — ток коллектора транзискт тора 22 (фиг.2).

При "0" .íà R-входе в базу транзистора 4 задается также ток через согласующий элемент 11 (фиг,1), Такий образом, при обычном управлении формирователем 3 время его включения определяется следующей суммой задержек в„ик„.„„и+ " е ц вот(„: j) вкл. ОГл. gA- " o

+ вкв. тра ": стара 4

Ири введении согласующего элемента 11 время включения определяется только Свк в, согрчр вю;: его в;асиент.%

+ t, и следовательно, ggq трц виствpa. выиграны во времени включения выходного формирователя 3 составляет

5 143361 подача уровней 0 есть запрещенная комбинация RS-триггера, построенного на элементах И), поэтому согласующий элемент 12 не задает ток в базы транзисторов 15 и 1б, что соответствует закрытому состоянию транзисторов

15-17.

Так как транзистор 4 открыт, транзистор 5 закрыт, на выходе формирует- 10 ся напряжение низкого уровня, равное

11 aux xo" 11 сс U кэ нэ + Ugg э где -Ucc — отрицательное значение напряжения высоковольтного источника питания;

U — напряжение между коллек юнз тором и эмиттером транзистора 4 в,режиме насыщения (фиг.1);

U — прямое падение напряжеD6 ния на диоде 6.

При изменении входного напряжения, подаваемого на R-вход,на "1" ток в базе 25 транзистора 4 поддерживается только

sa счет включенного согласующего элемента 2.

Пусть теперь на входную шину 14 подается уровень ".логического нуля", а на Е-вход "логическая единица", тогда согласующий элемент 11 находится в отключенном состоянии и не влияет на работу схемы.

Время выключения выходного Аормирователя 3 определяется выражением

35 выел ФормNрователя — вкл.эл-То м +

Ьйкл. Эл-та и Ьыкл,соглмс ющего влтава

+ С . вьал . тро н ьнстора 4, 40

Время выключения транзистора 4 определяется рассасыванием неосновных носителей заряда из области его базы.

При меньшем значении резистора 7 время рассасывания неосновных носителей заряда меньше.

При введении дополнительного согасующего элемента 12 и форсирующего блока 10 время выключения выходного высоковольтного Аормирователя определяется выражением

Вы кл. ф ор м и ро à а те л л

55 вмл,тронзмотораь Sя+

ВКЛ. Согл, Эл- та I2 выкл . Транзистора Ф

Учитывая, что практически

Т Ввл, согласующего 3n- ro ВЫКЛ. СОГЛаСуЮщ ЕГО ЗЛЕм ЕНта и вкn, трслнЭисто ро в 1Х! то Вкл. ЛогиЧЕСкОго ЗлЕме нта что задержка до начала выключения транзистора 4 сократилacI на время

+ t «лыкл 3п-та И "выкл.согласующего эл-.та 2 Вил. согласующ е гл элЕмен-а

Время выключения транзистора 4 уменьшилось из — за активного рассасывания неосновных носителей заряга транзистором 15 и из-за включения транзисторов 16 и 17, что приводит к значительному увеличению тока коллектора транзистора 4 °

Таким образом, уменьшается время выключения выходного Аормирователя 3 и резко сокращается Аронт нарастания выходного сигнала, Аналогично строятся рассуждения при построении RS-триггера 1 на элементах ИЛИ. формула изобретения

Преобразователь импульсов, содержащий ЙБ-триггер, выход которого через первый согласующий элемент подключен к входу Аормирователя, выполненного на первом и втором транзисторах п-р-II-типа проводимости, диоде, первом и втором резисторах, база первого транзистора соединена с входом

Аормирователя и через первый резистор с эмиттером первого транзистора и отрицательной шиной высоковольтного источника питания, а Cаза второго транзистора соединена с первым выво— дом второго резистора, о т л и ч а ю щ и Й с я тем, что, с целью уменьыения потребляемой мощности и увеличения быстродействия, введены форсирующий блок, второй и третий согласующие элементы, причем вход второго согласующего элемента подключен к первой входной шине и первому входу

RS-триггера, а выход — к первому входу формирователя„ вход третьего согласующего элемента подключен к второму входу RS-триггера и второй входой шине, а выход — к входу Аорсирующего блока, который выполнен на третьем и четвертом транзисторах и-р-и-типа и пятом транзисторе р-п-р-типа и третьем, четвертом, пятом резисторах, причем третий и четвертый транзисторы имеют общую базу и подключены к входу

Аорсирующего блока и через третий ре1483619 положительной шиной высоковольтного

Составитель В,Чижиков

Редактор Н,Киштулинец Техред И. Ходанич Корректор Л.Пилипенко

Заказ 2850/54 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 эистор соединены с эмиттерами третьего и четвертого транзисторов и отрицательной шиной высоковольтного источника питания, коллектор третьего транзистора подключен к входу формирователя, а коллектор четвертого транзистора через четвертый резистор подключен к базе пятого транзистора, которая через пятый резистор соединена с эмиттером пятого транзистора, источника питания и с вторым выводом второго резистора и коллектором второго транзистора, а коллектор пятого транзистора соединен с первым выводом второго резистора, коллектором первого транзистора, базой второго транзистора и катодом диода, анод которого подключен к выходной, шине и эмиттеру второго транзистора. !