Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

Изобретениие относится к импульсной технике и может быть использованов синтезаторах частот, а также в многоканальных системах передачи информации. Целью изобретения является уменьшение времени установления синхронной работы умножителя частоты следования импульсов. Устройство содержит генератор 1 импульсов, пересчетный блок 2 фазовый детектор 3, элементы И 4, 5, реверсивный счетчик 6, преобразователь 7 код-напряжение, RS - триггеры 8 и 9, входную и выходную шины 10 и 20 устройства, формирователь 11 короткого импульса, элемент 12 задержки, регистр 13 хранения. Фазовый детектор 3 содержит триггеры 14 и 15 и элементы И-НЕ 16-19. Введение дополнительных элементов: формирователя 11 короткого импульса, элемента 12 задержки и регистра 13 хранения позволяет вводить в реверсивный счетчик 6 код средней частоты полосы захвата из регистра 13 при нарушении синхронной работы, что уменьшает время установления синхронной работы умножителя и обеспечивает на выходе умножителя возможность получения выходного сигнала со средней частотой полосы захвата при нарушении синхронной работы. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК д ц 4 Н 03 К 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н двто скоью свидктельствм

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4137869/24-21 (22) 13.06.86 (46) 30.05.89. Вюл. И 20 (72) Г,А. Томилов и В.М. Волосюк (53) 621.374 ° 4 (088.8) (56) Авторское свидетельство СССР

М 1119165, кл. Н 03 К 23/00, 1983, Авторское свидетельство СССР

В 1429316, кл. Н 03 К 23/00. (54) УИНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и может быть использовано в синтезаторах частот, а также в многоканальных системах передачи информации. Целью изобретения является уменьшение времени установления синхронной работы умножителя частоты следования импульсов. Устройство содержит генератор 1 импульсов, пересчетный блок 2, фазовый детектор 3, „„Я0„„1483630 А 1

2 элементы И 4, 5, реверсивный счетчик

6, преобразователь 7 код-напряжение, RS-триггеры 8 и 9, входную и выходную шины 10 и 20 устройства, формирователь 11 короткого импульса, элемент 12 задержки, регистр 13 хранения, фазовый детектор 3 содержит триггеры 14 и 15 и элементы И-НЕ

16-19. Введение дополнительных элементов: формирователя 11 короткого импульса, элемента 12 задержки и регистра 13 хранения, — позволяет вво- дить в реверсивный счетчик 6 код средней частоты полосы захвата из регистра 13 при нарушении синхронной работы, что уменьшает время установления синхронной работы умножителя и обеспечивает на выходе умножителя возможность получения выходного сигнала со средней частотой полосы захвата при нарушении синхронной работы, 1 ил, - 1483630

Изобретение относится к импульс- ной технике и млжет быть использовано в синтезаторах частот, а также в многоканальных системах передачи информации.

Целью изобретения является повышение быстродействия путем уменьшения времени установления синхронной работы умножителя частоты за счет ввода в реверсивный счетчик кода средней частоты полосы захвата из регистра хранения при нарушении синхронной работы, что обеспечивает на выходе умножителя выходной сигнал со средней частоты полосы захвата.

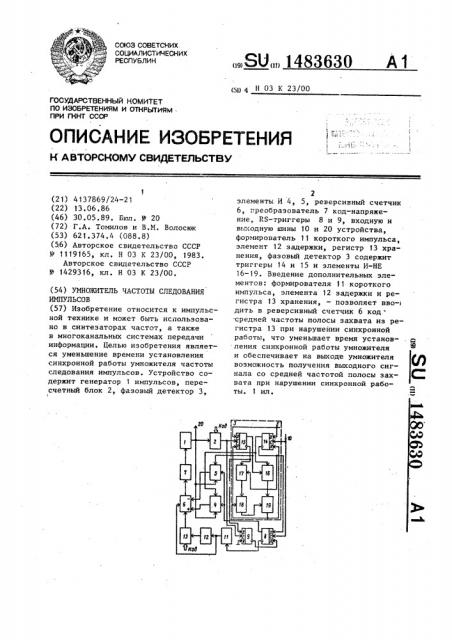

Структурно-электрическая схема устройства представлена на.чертеже.

Устройство содержит генератор 1 импульсов, пересчетный блок 2, фазовый детектор 3, первый и второй элементы И 4 и 5, реверсивный счетчик 6, преобразователь: 7 код — напряжение, первый и второй триггеры

8 и 9„ входную шину 10 устройства, формирователь 11 короткого импульса, элемент 12 задержки и регистр 13 хранения. Фазовый детектор 3 содержит триггеры 14 и 15 и элементы И-НЕ

16-19. .R-вход второго D-триггера 9 соединен с общей шиной, С-вход — с выходом пересчетного блока 2 и первым входом фазового детектора 3, D-вход— с первым выходом фазового детекто ра 3, а инверсный выход — с R-входом первого D-триггера 8, С-вход которого соединен с вторым входом фазового детектора 3 и входной шиной 10 уст-. ройства, à D-вход — с вторым выходом 40 фазового детектора 3, третий выход которого соединен с первым входом первого элемента И 4, а четвертый выход — с первым входом второго элемента И 5, второй вход которого соеди- 45 нен с третьим входом первого элемента И 4 и с прямым выходом первого

D-триггера 8, третий вход соединен с выходом генератора 1 импульсов, входом пересчетного блока 2 и вторым входом первого элемента И 4, а выходс входом вычитания реверсивного счетчика 6, вход суммирования которого . соединен с выходом первого элемента

И 4. Выход реверсивного счетчика 6 соединен с входом преобразователя 7 код - напряжение, выход которого соединен с управляющим входом генератора 1 импульсов, выход которого соединен с выходной шиной 20 устройства, Вход формирователя короткого импульса соединен с инверсным выходом первого D-триггера 8, а выход — с

R-входом реверсивного счетчика 6.

Информационный выход регистра 13 хранения соединен с информационным входом реверсивного счетчика 6, а вход Считывание" — с выходом элемента 12 задержки, вход которого соединен с выходом формирователя 11 короткого импульса.

Устройство работает следующим образом.

В исходном состоянии в пересчетный блок 2 (делитель частоты) вводится код требуемого коэффициента умножения, а в регистр 13 хранения - код, соответствующий умноженной частоте входного сигнала и равный средней частоте полосы захвата генератора 1.

Данный код вводится и в реверсивный счетчик 6.

Рассмотрим работу умножителя в синхронном режиме. Контроль за синхронной работой умножителя осуществляет устройство на триггерах 8 и 9.

При поочередном поступлении импульсов с входной шины 10 и импульсов с выхода пересчетного блока 2 оба триггера 8 и 9 находятся в состоянии

"1", обеспечивая формирование логической " 1" на соответствующих входах элементов И 4 и 5. При появлении на первом входе фазового детектора 3 входного импульса, триггер 14 переключается в состояние "1", а появившийся на втором входе импульс с выхода блока 2 переключает триггер 14 в состояние "0" ° Таким образом, на втором входе элемента И 4 формируется импульс длительностью, равной разности фаз сравниваемых частот.

Тогда импульсы с выхода генератора

i через первый вход элемента И 4 поступают на шину сложения реверсивного счетчика б,.за счет чего происходит увеличение выходного напряжения формируемого преобразователем код — напряжение, что приводит к возрастанию частоты следования импульсов генератора 1. Следующий импульс с выхода блока 2 появляется раньше, чем в предыдущем случае, что приводит к уменьшению разности фаз срав- ниваемых частот. Этот процесс продолжается до тех пор, пока разность

1483630 фаэ сравниваемых частот не станет равной нулю. Если импульс с выхода блока 2 появляется на втором входе фазового детектора 3 раньше, чем импульсы на его первом входе, то триггер 15 переключается в состояние.

"1" и формирует на прямом выходе импульс, который поступает на вход элемента И 5 и обеспечивает прохождение импульсов с выхода генератора.

1 на шину вычитания реверсивного счетчика 6. Сигналы с выхода. реверсивного счетчика 6 поступают на преобразователь 7, его выходное напряжение уменьшается, что приводит в конечном счете к уменьшению частоты следования импульсов генератора 1.

Указанные циклы повторяются до тех пор, пока разность фаз сравниваемых частот не станет равна нулю, При нарушении синхронизации, например, на С-вход триггера 8 поступают подряд два импульса с входа 16 устройства, тогда триггер 8 переключается под воздействием второго импульса в состояние "0" и на входах элементов И 4 и 5 формируется "0", обеспечивая тем самым разрыв кольца

ФАПЧ. При этом появляется напряжение на инверсном выходе триггера .8 и на входе формирователя 11 короткого импульса формируется импульс сброса в "0" реверсивного счетчика

6 и записи исходного кода из регистра 13 хранения в реверсивный счетчик

6 с некоторой задержкой, осуществляемой элементом 12 задержки для повышения надежности записи кода в реверсивный счетчик 6. При этом выходное напряжение преобразователя 7 код— напряжение обеспечивает формирование генератором 1 средней частоты полосы захвата ФАПЧ, При поступлении на Свход триггера 9 подряд двух импульсов с выхода блоха 2 переключаются в состояние "0" триггеры 8 и 9. Далее устройство функционирует, как и в первом случае нарушения синхронизации. При появлении синхронной работы триггеры 8 и 9 переключаются в состояние "1", замыкается кольцо ФАПЧ.

Таким образом, предлагаемое устройство по сравнению с прототипом позволяет уменьшить время вхождения в синхронизм за счет формирования частоты управляемого генератора равной средней частоте полосы захвата

ФАПЧ при нарушении синхронизации и обеспечения умноженной частоты на выходе устройства независимо от состояния системы синхронизации.

Формула изобретения мени установления синхронной работы устройства, в него введены формирователь короткого импульса, вход которого соединен с инверсным выходом первого D-триггера, а выход — с R-входом реверсивного счетчика, элемент задержки и регистр хранения, информационный выход которого соединен с информационным входом реверсивного счетчика, а вхбд "Считывание" - с выходом эле45

50 мента задержки, вход которого соединен с выходом формирователя короткого импульса, причем третий вход первого элемента И соединен с прямым выходом первого D-триггера, а вьжод генератора импульсов соединен с выходной шиной устройства.

Умножитель частоты следования импульсов, содержащий генератор импульсов, пересчетный блок, фазовый детектор, первый элемент И, второй элемент

И, реверсивный счетчик, преобразователь код — напряжение, первый триггер, второй D-триггер, R-вход которого соединен с общей шиной, С-вход— с выходом пересчетного блока и первым входом фазового детектора, D-вход— с первым выходом фазового детектора, а инверсный выход — с R-входом первого D-триггера, С-вход которого соединен с вторым входом фазового детектора и входной шиной устройства, а

D-вход — с вторым выходом фазового детектора, третий выход которого сое25 динен с первым входом первого элемента И, а четвертый входом -с первым входом второго элемента И, второй вход которого соединен с прямым выходом первого D òðèããåðà, третий вход соединен с выходом генератора импульсов, входом пересчетного блока и.вто. рым входом первого элемента И, а выход — с входом вычитания реверсивного счетчика, вход суммирования кото35 рого соединен с выходом первого элемента И, выход реверсивного счетчика соединен с входом преобразователя код — напряжение, выход которого соединен с управляющим входом генера40 тора импульсов, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия путем уменьшения вре