Интегрирующий аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых приборах и измерительных информационных системах. Изобретение позволяет повысить точность и стабильность интегрирующего аналого - цифрового преобразователя путем автоматической компенсации в каждом цикле преобразования погрешностей, вызванных неидеальностью элемента сравнения и задержкой включения опорного напряжения U<SB POS="POST">O</SB>. После окончания интегрирования интегратором 2 преобразуемого напряжения U<SB POS="POST">X</SB> и определения его знака под управлением контролера 5 реализуется фаза интегрирования U<SB POS="POST">O</SB>: сначала в течение небольшого фиксированного интервала времени интегрируется U<SB POS="POST">O</SB>, по знаку совпадающее с U<SB POS="POST">X</SB>, а затем - U<SB POS="POST">O</SB>, по знаку противоположное U<SB POS="POST">X</SB>, разряжающее интегратор. Момент разряда интегратора определяется элементом 3. Длительность разряда интегратора кодируется, и код запоминается в контролере 5. Последний затем устанавливает интегратор 2 в исходное состояние. Далее повторяется фаза интегрирования U<SB POS="POST">O</SB>. Результат преобразования формируется контролером 5 как разность кодов, полученных при первом и втором интегрировании U<SB POS="POST">O</SB>. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1483639

А1 (.Ч) 4 Н 03 М 1/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

APH ГКНТ СССР

f (21) 4247201/24-24 (22) 18.05.87 (46) 30.05.89. Бюл. 11! 20 (71) Московский энергетический институт (72) Ю.H. Евланов и А.А. Шатохин (53) 681.325 (088,8) (56) Высокочастотная цифровая измерительная система постоянного тока:

Экспресс информация ВИНИТИ, сер. Контрольно-измерительная техника, вып. 61, M. 1976, с ° 27-30.

Бухтияров Г.Д. Аналого-цифровые преобразователи. M. Сов.радио, 1980, с. 167, рис. 7,6. (54) ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых приборах и измерительных информационных сис,темах. Изобретение позволяет повы сить точность и стабильность интегрирующего аналого-цифрового преобразоИзобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых приборах и измерительных информационных системах.

Целью изобретения является повышение точности и стабильности.

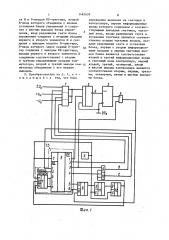

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — временные диаграммы, поясняющие его рабо ту в течение одного цикла преобразования.

2 вателя путем автоматической компенсации в каждом цикле преобразования погрешностей, вызванных неидеальностью элемента сравнения и задержкой включения опорного напряжения U .

После окончания интегрирования интегратором 2 преобразуемого напряжения

U è определения его знака под управлением контроллера 5 реализуется фаза интегрирования U,: сначала в течение небольшого фиксированного интервала времени интегрируется U,, по знаку совпадающее с V „, а затем U, по.знаку противоположное U », разряжающее интегратор ° Момент разряда интегратора определяется элементом 3. Длительность разряда интегратора кодируется, Я и код запоминается в контроллере 5. р,

Последний затем устанавливает интегра- @PE тор 2 в исходное состояние. Далее пов- горяется фаза интегрирования U„,. Pe- 1 зультат преобразования формируется ф контроллером 5как разность кодов, полученных при первом и втором интегриМ М ровании Uq. 1 з,п.ф-лы, 2 ил.

Аналого-цифровой преобразователь содержит коммутатор 1, интегратор 2, элемент 3 сравнения, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, контроллер 5, генератор

6 импульсов, счетчик 7, RS-триггер 8, элементы И 9, 10, D-триггеры 11 и 12.

Контроллер 5 и счетчик 7 образуют блок 13 управления. В качестве контроллера может быть использована однокристальная микраЭВМ KP 1816 ВЕ 48, .выводы которой соединены с входами и выходами контроллера 5 следующим

1483639 образом: вывод 1 с тактовым входом контроллера, выводы 27-32 — с выходами 1-6 соответственно, выводы 33 и 34 — с информационными входами 1

5 и 2, информационные входы с 3 по п контроллера соответствуют выводам

21-24, 35"38, 12"19 микроЭВМ.

На фиг. 2 обозначено: IP — второй информационный вход контролле- ip ра 5; ОР1- ОР— соответственно выходы 1-6 контроллера 5; А, В, С вЂ” выходы соответственно интегратора 2, элементов И 9, 10; IP — первый информационный вход. 15

Устройство работает следующим образомм.

Интегратор 2 находится в исходном состоянии, что обеспечивается уровнем напряжения "1" только на вто- 20 ром выходе контроллера 5. Сигнал, появляющийся на шине внешнего запуска, подается на второй информационный вход контроллера 5, который переводит второй выход контроллера 5 в состояние "0", а первык выход— в "1". В результате на информационный вход интегратора 2 через коммутатор 1 подается преобразуемое напряжение U„. При отрицательном П „ выход- ЗО, ное напряжение интегратора линейно нарастает. По истечении фиксированного интервала времени Т,, задаваемого контроллером 5, например, посредством программной задержки, первый выход контроллера 5 переходит в состояние "0", В результате прекращается пода U „ на информационный вход интегратора. Затем производится определение знака напряжения щ0 путем опроса контроллером 5 вых6да элемента 5. При положительном напряжении на выходе интегратора 2 (U <0) на выходе элемента 4 формируется уровень "1".

Для исключения влияния внутренних коммутационных помех при малых значениях Uy после определения знака ГГ в течение короткого интервала времени д, длительность которого

; программно задается контроллером 5, 1производится интегрирование опорноI го напряжения U того же знака, что и U . Это достигается тем, что контроллер 5 сначала устанавливает в

"1" пятый выход, а затем с небольшой задержкой (на фиг. 2 не показана) четвертый или третий выход в зависимости от знака U„, В случае, покаэанном на фиг. 2, контроллер устанавливает "1" на четвертом выходе.

По окончании dt все выходы, кроме шестого, устанавливаются контроллером 5 в нулевое состо::.ние. Этим очищается счетчик 7, переводятся в нулевое состояние триггеры 8, 11 и

12 и дается запрет на вторые входы элементов 9 и 10. Далее выполняется разряд интегратора 2 путем интегрирования U, по знаку противоположного U для чего на третьем или четвертом выходе в зависимости от знака

U „ контроллером 5 устанавливается

"1", на шестом выходе — "0", на пятом выходе формируется короткий положительный импульс. Последнии.переводит триггеры 8, 11 и 12 в единичЪ ное состояние, чем разрешается интегрирование U и подсчет импульсов генератора б счетчиком 7. Триггеры 11 и 12 осуществляют синхронизацию включения U и начала подсчета импульсов счетчиком 7. В случае, показанном на фиг. 2, активизирован элемент 9, под действием выходного сигнала которого на информационный вход интегратора 2 поступает через коммутатор 1 напряжение +U . При достюкении выходным напряжением интегратора порога срабатывания элемента 3 на выходе элемента 4 формируется положительный перепад напряжения, под действием которого RS-триггер 8 переходит в нулевое состояние, а затем синхронно с фронтами импульсов генератора 6 переходят в нулевое состояние D-триггеры — оканчивается интегрирование

U Последовательность действий на с интервале времени от начала интегрирования Ua того же знака,что и U до окончания интегрирования U, по знаку противоположного U составляет фазу интегрирования опорных напряжений. Опрос контроллером 5 вь|хода элемента 4 на интервале разряда интег ратора позволяет определить окончание этой фазы. Затем контроллером 5 производится считывание и запоминание выходов разрядов счетчика 7. Далее контроллером на интервале dt устаЬ навливается в исходное состояние интегратор 2. Для этого только на, втором выходе устанавливается "1"., По окончании интервала 4t повторя-, ется фаза интегрирования опорных напряжений. Результат преобразования

1483639 формируется контроллером 5 как разность кодов, полученных при первом и втором выполнении фазы интегрирования опорных напряжений.

При первом выполнении фазы интегрирования опорных напряжений длительность Т разряда интегратора равна

Т,= T,— + dt + dt,, (1)

U» о где Т, — длительность интегрирования преобразуемого напряжения;

U †ойорное напряжение . Ux — преобразуемое напряжение;

ht, — приращение длительности Т за счет интегрирования U на интервале В t — приращение Т из-за неидеальности элемента сравнения и задержки включения U0.

Поскольку повторение фазы интегрирования опорных напряжений следует непосредственно после интервала d t и занимает малый промежуток времени, то условия работы элемента 3 практически не изменяются. Поэтому при втором выполнении фазы интегрирования опорных напряжений длительность Т i разряда интегратора равна

Т, =dt + 1 т 2 (2) Учитывая кодирование временных интервалов Т и Т, выражения (1) и (2) можно представить в виде: N,=N- + Ы, +dN + q (3)

U о

N = dN„+dN + q (4 ) N„= N, „-- + (q,— q ). (5)

П»

Пo

Таким образом, результат преобразования АЦП оказывается свободным от погрешностей, обусловленных неидеальностью элемента 3 и задержкой включения опорного напряжения, с точностью до значения (q,-q ), которое определяется разрешающей способгде q u q — погрешности дискретнос1 ти при кодировании соответственно интерва--. лов Т и Т .

Результат преобразованйя N„ определяется как разность N — N согЯ ласно формулам (3) и (4):

15 ностью АЦП, Погрешность АЦП из-за неидеальности элемента 3 и задержки включения может достигать 1000 ступеней квантования. В предлагаемом

АЦП, как следует из формулы (5), погрешность уменьшается до 1 ступени квантования. Указанное преимущество обеспечивает повышение точности и стабильности АЦП и цифровых приборов на их основе, а также позволяет снизить требования к параметрам элемен-: та 3 и устранить связанные с рассмот ренной погрешностью ручные калибро вочные операции H состве". — вующие им регуяировочные элементы.

Формула изобретения

Интегрирующий аналого-цифровой

2р преобразователь, содержащий коммутатор, первый, второй и третий информационные входы которого являются со-ответственно входной шиной и шинами напряжения положительной и отрица25 тельной полярности, первый выход коммутатора соединен с информационным входом интегратора, вход начального значения интегрирования которого объединен с первым входом элемента сравЗ0 нения и является шиной нулевого потенциала, выход интегратора соединен с вторым входом элемента сравнения, генератор импульсов, выход которого соединен с первым тактовым входом блока управления, первый выход которого соединен с первым управляющим входом коммутатора, о т л и ч а— ю шийся тем, что, с целью повышения точности и стабильности, в него

40 введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два

D-триггера, два элемента И, RS-триггер, второй выход блока управления соединен с входом установки в исходное состояние интегратора, третий выход соединен с первым входом первого элемента И и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которога соединен с выходом элемента сравнения, а выход соединен с пер50 вым R-входом RS-триггера и первым информационным входом блока управления, второй информационный вход которого является шиной внешнего запуска, второй тактовый вход блока управления объединен с его первым тактовым входом, с входами первого и второго Dтриггеров, четвертый и пятый выходы блока управления соединены соответственно с первым входом второго элемен1483639 та И и S-входом RS-триггера, второй

R-вход которого объединен с входом установки блока управления и соединен с шестым выходом блока управ5 ления, вход разрешения счета блока управления соединен с вторыми входами первого и второго элементов И и соединен с выходом второго D-триггера, D-вход которого. через первый D-триггер соединен с выходом RS-триггера, выходы первого и второго элементов И соединены соответственно с вторым и третьим управляющими входами коммутатора, второй и третий выходы ком- 15 мутатора объединены с его первым выходом

2. Преобразователь по п. 1, о т— л и ч а ю шийся тем, что блок управления выполнен на счетчике и контроллере, первые информационные входы которого соединены с соответствующими выходами счетчика, тактовый вход, входы разрешения счета и установки счетчика являются соответственно вторым тактовым входом, входами разрешения счета и установки блока, первым и вторым информационными входами и первым тактовым входом блока являются соответственно второй и третий информационные входы и тактовый вход контроллера, первый второй, третий, четвертый, пятый и шестой выходы контроллера являются соответственно вторым, первым, третьим, четвертым, пятым и шестым выходами блока.

1483639

Составитель А. Титов

Редактор И. Рыбченко Техред Л.Сердюкова Корректор М; Максимишинец

Заказ 2851/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

QPg

ОР>

gled