Преобразователь двоичного кода в код по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и является усовершенствованием устройства по авт. св. N 902013. Его использование в вычислительных устройствах, работающих в системе остаточных классов, позволяет расширить область применения за счет преобразования целых комплексных чисел в вычет по целому комплексному модулю. Преобразователь содержит входной регистр 1, шифраторы 2 двоичного кода в код по модулю и сумматор 3 по модулю. Благодаря введению блоков 4, 5 коммутации, блоков 6, 7 умножения действительной и мнимой частей, накапливающего модульного сумматора 8 и блоков 9, 10 преобразования кодов действительной и мнимой частей в преобразователе реализуется новый алгоритм вычисления остатка целого комплексного числа по целому комплексному модулю. 3 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛЧСТИЧЕСНИХ

РЕСПУБЛИК

А2 (5114 Н 03 M 7/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (61) 902013 (21) 4264334/24-24 (22) 27.04.87 (46) 30.05.89. Бюл. Ф 20 (72) А.П.Болтков (53) 681.325.53(088.8) (56) Авторское свидетельство СССР

М -902013, кл. Н 03 N 7/18, 1980 ° (54) ПРЕОБРАЗОВАП;11Ь ДВОИЧНОГО КОДА

B"-КОД ПО МОДУЛ!О (57) Изобретение относится к вычислительной -.åõíèêå и является усовершенствованием устройства по авт. св.

9 902013. LI o использование в вычислительных устройствах, работающих в системе остаточных классов,,позволяет

„„SU„„4s

2 расширить область применения за счет преобразования целых комплексных чисел в вычет по целому комплексному модулю. Преобразователь содержит входной регистр 1, шифраторы 2 двоичного кода в код по модулю и сумматор

3 по модулю. Благодаря введению блоков 4,5 коммутации, блоков 6,7 умножения действительной и мнимой частей, накапливающего модульного сумматора 8 и блоков 9, 10 преобразования кодов действительной и мнимой частей в преобразователе реализуется; новый алгоритм вычисления остатка целого комплексного числа по целому комплексному модулю. 3 ил.

1483643

Изобретение относится к вычислительной технике, является усовершенствованием устройства по авт. св.

Р 902013 и может быть использовано в вычислительных устройствах, работающих в системе остаточных классов (COK) .

Цель изобретения — расширение области применения за счет преобразования целых комплексных чисел в вычет по целому комплексному модулю.

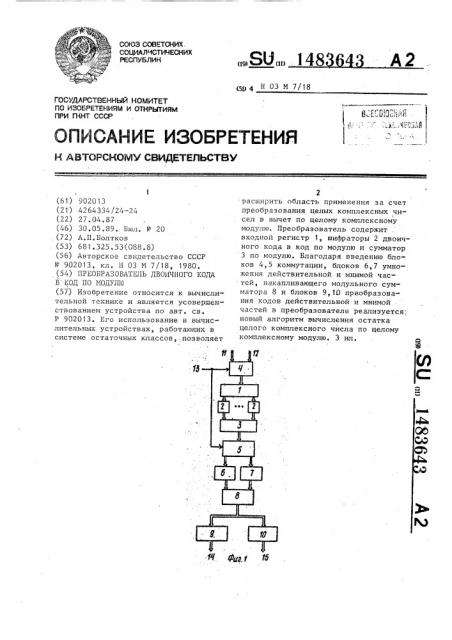

На фиг. 1 приведена блок-схема преобразователя; на фиг. 2 и 3 — таблицы, поясняющие алгоритм работы пре" 15 образователя.

Преобразователь двоичного кода в код по модулю содержит входной регистр 1, шифраторы 2 двоичного кода в код по модулю, сумматор 3 по моду- 20 лю, первый и второй блоки 4 и 5 коммутации, блок 6 умножения действительной части,-блок 7 умножения мнимой части, накапливающий модульный сумматор 8, блок 9 преобразования ко- 25 да действительной части, блок 10 преобразования кода мнимой части, входы 11 и 12 действительной и мнимой частей, управляющий вход 13, выходы

14 и 15 действительной и мнимой час» 30 тей, В основу работы преобразователя положены следующие правила.

Пусть A=a+bi — целое комплексное число, подлежащее преобразованию, 35

m=p+qi — целый комплексный модуль, В=

=х+у . — наименьший вычет, равный наименьшему целому положительному остатку от деления числа А на число m.

Деление А на ш дает следующий ре- 40 зультат:

А а+М ап+Ьп Ьв-ац. (1)

m P+qi Р2 + 12 Р2 +q2

А

Если -. — целое число, то можно заm 45 писать

ap+bq=0mod(p +qu)f

bp-ац=0шоД(р +q ) ( (2)

Если А не делится нацело на m, то

° ° существует такое В, что А-В делится ацело на m. Тогда получив разность ф

-В, разделив ее íà m по правилу (1) приведя к виду (2), получим

ap+bq (xp+yq)mod(p2+q )

Ьр-aq=(yp-xq)mod(p +q2) (3) где B x+yi.

Для определения х и у необходимо решить два уравнения с двумя неизвестными.

Пусть

ap+bq=Zmîd(ð +qã ) f

bp-aq=Vmod(p +q )J

Тогда

xp+yq--7. ур-xq=V ( (4) (s) (7) задачи.

Аналогичная таблица составляется для расчета значения х. На фиг. 3 представлена сводная таблица соответствия значений Z, у, х. Пусть необходимо найти В от числа A=29+Si, где а=29; b=S. По формуле (4) определим Z:

Z=ap+bq=(29modf3x3+Smodf3x2)mod13=

=12mod13. По таблице на фиг, 3 определим величины х и у, соответствующие Z=12. Получим х=2; y=3. Таким образом, B=2+Çi. .Если полученный результат является верным, то должны выполняться два условия: разность А-В должна нацело делиться на рг +qг; модуль комплексноro числа В не должен превышать величины р +я

Используя формулу (1), разделим разность на m:

А-В 29+Si-2-Çi — 7 Çi.

Умножив первое уравнение систем (5) на q, а второе на р, сложив их и выразив у, получим

Zq+Vp

У= (6)

p2+q2

Аналогично определяем

4р-Ча х= —— рг +<1г

Геометрической интерпретацией решения системы (5) является пересечение двух отрезков, длина которых ограничена величиной модуля комплексного числа, следовательно, достаточно получить только одно из значений Z или V, а затем, составив таблицу соответствия, получить другое значение, а далее искомые величины у и х. Количество возможных пар х и у для данного основания СОК постоянно и равно (рг + 1г )

Пример, Пусть комплексный модуль m=3+2i, где р=З; q=2, тогда рг+q2=13. Следовательно, Z=0,12 и

7=0,1 !. Таблица значений у, рассчитанных в зависимости от комбинаций

V u Z по формуле (6), представлена на фиг. 2, где пустым клеткам соответствуют дробные значения величины у, что выходит за пределы решаемой

7-3i — целое комплексное число, т. е. первое условие выполняется.

2 . +3 =13 рг +ог =13 — второе условие выполняется. Следовательно, полученный результат является верным.

Блок 6 умножения реализует операцию умножения величины атоЙ(рг+цг) на константу р по модулю (p +q ).

Блок 7 реализует операцию умножения величины bmod(p +q ) на константу по модулю (р +q ). Блок 9 преобразует значение величины Z в величину х согласно сводной таблицы соответствия (подобная таблица для модуля m=3+2i показана на фиг. 3). Блок 10 преобразует значение величины Z в величину у согласно сводной таблице. Сумматор 8 производит суммирование по модулю (,г qz)

Преобразователь работает следующим образом.

В исходном состоянии блоки 4 и 5 коммутируют входы 11 и блок 6, сумматор 8 обнулен. На выходах 14 и 15 нули. На входы 11 и 12 подаются соот" ветственно величины а и Ь. Шифрато-.. ры 2 и сумматор 3 преобразуют величину а (целую часть комплексного числа) в величину al =amod(p +ог), которая подается на входы блока 6.

По окончании переходного процесса на выходе блока 6 устанавливается величина a pmod(p +q ), которая складывается с нулем накапливающего сумматора 8.

Затем блоки 4 и S переключаются в иное положение, при этом величина Ь 1 преобразуется в вычет по модулю

Ь =bmod(p +q ) .

На выходе блока 7 устанавливается величина Ъ qmod(p +q ), которая складывается с содержимым сумматора 8, на выходах которого появляется результат а .р+Ъ ° q=Zmod(p +q ).

Блоки 9 и 10 преобразуют величину Е в величины х и у по вышеизложенному алгоритму.

Таким образом, предлагаемый преобразователь позволяет преобразовать

83643 6 комплексные числа в вычет по целому комплексному модулю.

Так как целые действительные числа являются подмноЖеством целых ком5 плексных чисел вида А=а+Ьг. при Ь=О, рассматриваемый преобразователь преобразует и действительные числа в вычет по комплексному мЬдулю, а на выходах сумматора 3 формируется вычет по целому действительному модулю, равному (p +qã ) 15

Формула изобретения

Преобразователь двоичного кода в код по модулю по авт. св. У 902013, отличающийся тем, что, с целью расширения области примене20 ния за счет преобразования целых.комплексных чисел в вычет по целому комплексному модулю, в преобразова тель введены блок умножения действительной части, блок умножения мнимои .части, накапливающий модульный сумматор, блок преобразования кода действительной части, блок преобразования кода мнимой части и первый и второй блоки коммутации, управляющие входы которых объединены и являются управляющим входом преобразователя, первые и вторые информационные входы первого блока коммутации являются входами соответственно действительной и мнимой частей преобразователя,. выходы первого блока коммутации соединены с входами входного регистра, выходы сумматора по модулю подключены к информационным входам второго блока коммутации, первые и вторые выходы которого через блоки умножения соответственно действительной и мнимой частей соединены с первыми и вторыми входами накапливающего мо45 дульного сумматора, выходы которого подключены к входам блоков преобразования кода действительной и мнимой частей, выходы которых являются выходами соответственно действительной и мнимой частей преобразователя.

1483643.Г

Составитель О. Ревинский

Техред Л. Олийнык Корректор N, Âàðèër,åâà

Редактор И.Рыбченко

Заказ 2852/56

Тираж 884

Подписное

ВНИИПИ Государственного комитета по изобретенинм и открытилм при ГКНТ СССР

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 10l