Устройство для кодирования информационного сигнала и передачи его в первичную цифровую систему связи

Иллюстрации

Показать всеРеферат

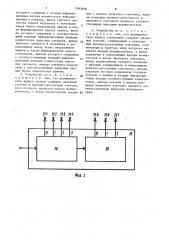

Изобретение относится к вычислительной технике и технике связи. Его использование для передачи сигналов звукового вещания в тракте стандартной первичной цифровой системы передачи позволяет повысить помехоустойчивость сигнала. Устройство содержит блок 1 выделения синхросигнала, коммутатор 2 информационного сигнала, делитель 3 частоты, регистр 5 сдвига и элементы И 8-10. Благодаря введению делителя 4 частоты, регистров 6, 7 сдвига, элемента НЕ 11, блока 12 оперативной памяти, коммутатора 13 адресных сигналов, формирователя 14 адреса считывания и формирователя 15 адреса записи в устройстве обеспечивается перемежение октетов с максимально разнесенными символами информационного сигнала. 2 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU„„1483648

OIlHGAHHE HSOEPETEHHFI

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ и э, .

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4191195/24-24 (22) 05.02.87 (46) 30 ° 05.89. Бюл, 1 - 20 (72) И.М.Дворецкий и И.H.Äðèàöêèé (53) 621.396.97:621.376.037(088.8) (56) Дворецкий И.М., Дриацкий И.Н.

Цифровая передача сигналон звукового вещания. N. Радио и связь, 1987, с. 96-98.

МККТТ Зеленая книга, т. III-4.

Рекомендация J. 41 ° (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ИНФОРМАЦИОННОГО СИГНАЛА И ПЕРЕДАЧИ ЕГО

В ПЕРВИЧНУЮ ЦИФРОВУЮ СИСТЕМУ СВЯЗИ (57) Изобретение относится к вычислительной технике и технике связи. его использование для передачи сигналов (ду 4 Н 04 В 1/66, Н 03 М 13/22

2 звукового вещания в тракте стандартной первичной цифровой системы передачи позволяет повысить помехоустойчивость сигнала. Устройство содержит блок 1 выделения синхросигнала, коммутатор 2 информационного сигнала, делитель 3 частоты, регистр 5 сдвига и элементы И 8-10. Благодаря введению делителя 4 частоты, регистров 6,7 сдвига, элемента НЕ 11; блока 12 one" ративной памяти, коммутатора 13 адресных сигналов, формирователя 14 адреса считывания и формирователя 15 адреса записи в устройстве обеспечивается перемежение октетов с максимально разнесенными символами.инфор- д мационного сигнала. 2 з.п. ф-лы, 4 ил.

1483648

Изобретение относится к вычислительной технике и технике связи и может быть использовано для передачи, например, сигналов знуконого вещания (ЗВ) в тракте стайдартной первичной цифровой системы связи (ПЦСС).

Цель изобретения — паньппение помехоустойчивости инАормационного сигналя. 1Р

На фиг. 1 приведена Аункциональная схема устройства; на Аиг. 2 и 3 - примеры выполнения формирователей адреса записи н адреса считывания; на Аиг.4сигнал ПЦСС, объединенный с информационным сигналом, Устройство (фиг.1) содержит блок 1 выделения синхросигнала, коммутатор 2 информационного сигнала, первый и второй делители 3 и 4 частоты, первый — 2p третий регистры 5-7 днига, первый— третий элементы И 8-t"2,,элемент НЕ 11, блок 12 оперативной памяти, коммутатор 13 адресных сигналов, Аормнрователи 14 адреса считывания и 15 адреса 5 записи, вход 16 информационного сигнала, вход 17 сигнала ПЦСС, тактовый

Йход. 18.

В основе работы устройства лежит поканальное объединение источников 30 информации, при котором общий канал связи предоставляется не отдельным цифровым символам, а октетам симво" лов каждого источника. В конкретной реализации отсчеты инАормационного сигнала, например сигнала ЗВ, являются десятираэрядными, причем на один цикл работы ПЦСС (на 32 октета) приходится четыре отсчета сигнала ЗВ, нулевой и шестнадцатый октеты являют- 4р ся служебкыми. 3То определяет следую" щее выполнение блоков устройства, Делители 3 и 4 имеют коэффициент деления 8. Регистр 5 сдвига имеет 16 разрядов, регистры 6 и 7 — по. шесть. 45

Каждый из регистров 5-7 выполняет функцию выделения каждого шестнадцатого (шестого) импульса, поступающего на его вход. Блок 1 выделения синхро" импульсов служит для привязки работы делителей 3,4 и регистров 5 6 к кулевому и шестнадцатому октетам.

Формирователь 15 адреса записи (фиг.2) содержит двоична-десятичный счетчик 19 и двоичный счетчик 20. Выходы разрядов двоична-десятичного счетчика 19 с нулевого по третий и вы ходы разрядон двоичного счетчика 20 с нулевого по второй образуют выхоны

21 формирователя 15 с первого по седьмой.

Формирователь 14 адреса считывания (фиг. 3) содержит триггер 22, двоичный счетчик 23, суммирующий счетчик

24, вычитающий счетчик 25, коммута" торы 26, выходы 2? (выходы первого четвертого коммутаторов 26 и выходы второго, нулевого и первого разрядов двоичного счетчика 23).

Устройство работает следующим образом.

Входной цифровой сигнал ПЦСС поступает на вход 17, информационный сиг" нал (сигнал ЗВ) — на вход 16. В коммутаторе 2 осуществляется временное объединение цифрового сигнала первичной ЦСС с цифровым сигналом от внеш" него источника, например с сигналом

ЗВ. При этом сигнал ЗВ вводится н сигнал первичной ЦСС актетами беэ нарушения структуры цикла ПЦСС и с необходимым перемежением символов, осуществляемым в других блоках устройства.

Блок 1 выделения синхросигнала осуществляет при обнаружении синхросигнала установку в нулевое состояние делителей 3,4 н регистров 5 и 6. Тем самым обеспечивается цикловая синхронизация устройства.

Тактовые импульсы поступают на вход 18. Сигналом с инверсного выхода регистра 5 поступление тактовых импульсов прерывается, чем обеспечивается блокировка ввода информации в специальные канальные интервалы цикла ПЦСС (н нулевой и в 16-й канальные интервалы, см. фиг. 3), Регистр 6 обеспечивает равномерное размещение вводимой информации в сигнале ПЦСС, т.е. максимальное разнесение по времени октетов вводимого сигнала между собой. Сигнал с выхода регистра 6 управляет работой коммутатора 2. При наличии этого управляющего сигнала коммутатор 2 осуществляет замену циАровых символов сигнала

ПЦСС на символы внешнего сигнала, поступающие от блока 12 памяти. На вход алака 12 памяти поступает сигнал от внешнего источника, причем за счет управляющего сигнала от регистра 6, подаваемого через элемент НЕ 11, осуществляется блокировка входа блока 12 памяти в интервалы времени, когда выходной сигнал блока 12 памяти вводится в тракт ПЦСС, Считывание сигнала из блока 12 памяти осуществ1483648 ляется тактовыми импульсами с выхода элемента И 8 в интервалы времени, определяемые регистром 6. Запись в блок 12 памяти осуществляется сигна5 лом с выхода регистра 7. Формирователи 14 и 15 адреса считывания и запи" си поочередно подключаются через коммутатор 13 адресных сигналов к адресным входам блока 12 памяти. Наличие этих формирователей, синхронно и поочередно подключаемых к блоку 12 памяти, обеспечивает необходимое перемежение символов вводимого сигнала, так как порядок записи символов в блок 12 отличается от порядка их считывания. В рассматриваемом устройстве за счет управления работой фор" мирователей 14 и 15, коммутатора 13 адресных сигналов и блока 12 памяти от регистров 6,7 и делителя 4 реали- зуется октетный ввод внешнего сигнала с максимальным разнесением во времени цифровых символов соседних отсчетов вводимого сигнала. 25

Формирователь 1S адреса записи (см. фиг. 2) формирует на адресных выходах упорядоченную двоичную последовательность адресов (0,1,2,...,19).

При этом нулевой символ входного .сиг- Зо нала записывается в нулевую ячейку памяти блока 12, первый символ — в первую, второй — во вторую и т.д.

Формирователь 14 адреса считыва- . ния (cM. фиг. 3) формирует специальную последовательность адресов (0,9, 35

20,29,40,49,60,69,10,19,30,39 и т.д.), обеспечивая считывание символов в по" рядке, отличном от порядка записи.

При этом обеспечивается максимальное 40 разнесение символов соседних отсчетов вводимого сигнала без нарушения октетной структуры цикла сигнала ПЦСС.

На фиг. 4 показан ввод десятиразрядных отсчетов сигнала звукового 45 вещания. В двух циклах ПЦСС размещается 8 отсчетов сигнала 3В (всего

80 символов). Сигнал ЗВ размещается октетами по пять октетов в каждом из двух циклов (всего 10 октетов). В каж- 50 дом октете размещены четыре пары символов разных отсчетов, причем либо только четных, либо нечетных.

Пачка ошибок, возникшая в первичном цифровом тракте, не может исказить два соседных отсчета сигнала 3В, если длительность пачки меньше или равна 48 символам. Таким образом, достигается увеличение помехоустойчивости по отношению к воздействию пачек ошибок.

Формула изобретения

1. Устройство для кодирования информационного сигнала и передачи

его в первичную циАровую систему связи, содержащее коммутатор информационного сигнала, первый инАормационный вход которого объединен с входом блока выделения синхросигнала и является первым инАормационным входом устройства, выход блока выделения синхросигнала подключен к входам обнуления первых регистра сдвига и делителя частоты, выход которого соеди" нен с информационным входом первого регистра сдвига, инверсный выход которого подключен к первому входу первого элемента И, второй вход которого объединен со счетным входом первого делителя частоты и является тактовым входом устройства, второй элемент И, первый вход которого является вторым информационным входом устрой-„ ства, выход первого элемента И соединен с первым входом третьего элемента И, второй вход которого объединен с управляющим входом коммутатора информационного сигнала, выход которого является выходом устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости информационного сигнала, в него введены блок оперативной памяти, коммутатор адресных сигналов, формирователь адреса записи, формирователь адреса считывания, элемент НЕ, второй и третий регистры сдвига и второй делитель частоты, счетный вход которого объединен с информационным входом третьего регистра сдвига и подключен к выходу первого элемента И, выход второго делителя частоты соединен с информационным входом второго регистоа сдвига, вход обнуления которого объединен с входом обнуления второго делителя частоты и подключен к выходу блока выделения синхросигнала, прямой выход второго регистра сдвига соединен непосредственно и через элемент НЕ соответственно с управляющими входами коммутаторов информационного и адресных сигналов и с вторым входом второго элемента И, выход которого подключен к инйормационному входу блока оперативной памяти, выход

1ч 83648 которого соединен с вторым информационным входом коммутатора информационного сигнала, выход третьего регистра сдвига подключен к тактовому входу блока оперативной памяти и входу формирователя адреса записи, выходы которого соединены с соответствующими первыми информационными входами коммутатора адресных сигналов, выход третьего элемента И подключен к уп" равляющему входу блока оперативной памяти и входу формирователя адреса считывания, выходы которого соединены с соответствующими вторыми информационными входами коммутатора адресных сигналов, выходы которого подключены к соответствующим адресным входам блока оперативной памяти.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что формирователь адреса записи содержит двоичный счетчик и двоично-десятичный счетчик, вход которого является входом формирователя, а выход переполнения соединен с входом двоичного счетчика, выходы разрядов двоично-десятичного и двоичного счетчиков являются соответствующими выходами. формирователя.

3. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что формирователь адреса считывания содержит двоичный счетчик, суммирующий и вычитающий двоично-десятичные счетчики, коммутаторы и триггер, вход которого является входом формирователя, а выход подключен к управляющим входам коммутаторов и входу двоичного счетчика, выход переполнения которого соединен с входами суммирующего и вычитающего двоично-десятичных счетчиков, выходы разрядов которых подключены соответственно к первым и вторым информационным входам соответствующих коммутаторов, выходы которых и выходы разрядов двоично1о счетчика являются соответствующими выходами формирова2, теля.

1483648

Р5 П6 Щ УП Пг гИ г .ч

I-0юрткщ 7-й аапт 13й юкка 23-д папесс 25-Одопом

Составитель О.Ревинский

ТехРед Л.Олийнык КоРРектоР M.Пожо

Редактор И.Рыбченко

Заказ 2853/56 Тираж 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, l01