Устройство для регистрации формы однократных электрических сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано для исследования кратковременных однократных электрических сигналов. Цель изобретения - повышение точности регистрации однократных электрических сигналов. Входной сигнал усиливается во входном устройстве и поступает на первые входы первого, второго и третьего коммутаторов, на первые входы четвертого, пятого и шестого коммутаторов подается контрольный сигнал калиброванной амплитуды. Исследуемый и контрольный сигналы подключаются на входы аналоговой памяти. Далее начинается процесс медленного считывания из аналоговой памяти, усреднения в блоках усреднения, корректирования в блоке коррекции, преобразования в код в АЦП и записи в ту же аналоговую память. Таким образом, информация, считываемая из аналоговой памяти, замыкается в кольцо, обеспечивая циркуляцию кода записанного сигнала и его циклический вывод. 1 ил.

СОЮЗ СОВЕТСНИХ

COLLHAfIHCT VHECHVI X

РЕСПУБЛИК (19) (11) А1 (51) 4 (01 R 29/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPGKOlVIV СВИДЕТЕЛЬСТВУ (21) 4362830/24-21 (22) 11.01.88 (46) 07,07.89. Вюл. Н 25 (71) Рязанский радиотехнический институч (72) В.Г.Кряков, Е.М,Прошин и В.Н.Штырков (53) 621.317.75(088.8) (56) Рехин Е.И. и др, Измерение однократных сигналов н современной ядерной физике. — M Энергоатомиздат, 1983.

Авторское свидетельство СССР

Ф !406533, кл. G 01 R ?9 02, 1988, (54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ФОРMbI ОДНОКРАТНЫХ 3JIi:ÊTÐÈ×ÅÑÊÈÕ СИГНАЛОВ (57) Изобретение относится к измерительной технике и может быть использовано для исследования кратковременных однократных электрических

Изобретение относится к измерительной технике и может быть использоваьо для исследования кратковременных однократных электрических сигналов.

Целью изобретения является повышение точности регистрации однократных эпе ктриче ских сигналов.

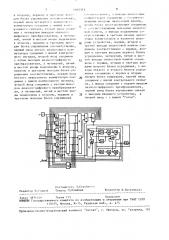

На чертеже приведена функциональная схема предлагаемо. о устройства.

Устройство содержит блок 1, «наJIoI îâûå коммутаторы 2-7, блок 8 аналоговой памяти, первый 9 и второй 10 блоки усреднения, блок 11 коррекции, сигналов. Цель изобретения — повышение точности рр гистрации однократ ных эле ктриче ских си гн алов, Входной сигнал усиливается во входном устройстве и поступает на первые входы первого, второго и третьего коммутаторов, на первые входы четвертого, пятого и шестого коммутаторов подается контрольный сигнал калиброванной амплитуды. Исследуемый и контрольный сигналы подключаются на входы аналоговой памяти. Далее начинается процесс медленного считывания из аналоговой памяти, усреднения в с блоках усреднения, корректирования в блоке коррекции, преобразования в код в АЦП и записи в ту же аналоговую память. Таким образом, информация, считываемая из аналоговой памяти, з амыкае тся в кол ьцо, обе спечивая циркуляцию кода записанного сигнала и его циклический вывод. I ил. аналого-цифровой преобразователь 12, блок 13 восстановления, генератор 14 тактовых импульсов, блок 15 управления, причем первый вход блока 15 управления подключен к выходу входного блока 1, а нторой вход связан с шиной "Готов", вход генератора 14 тактовых импульсов соединен с первым выходом блока управления, а выход со вторым входом аналого-цифроного преобразователя 12, первый нход первого аналогового коммутатора 2 сое- динен с выходом входного блока 1, второй нход соедин(.н с первым выхо14923I3

55 и »и ;»палого-цифр» ного иреобраэовате—

)я I 2,,третий вход соединен с первым нь;ходом блока 13 восстановления, nt >вый вход второго коммутатора 3 . .оедии» H с вь»ходом входного блока 1, в-.орой вход — с вторым выходом аналого-цифрового преобраэователя 12, третий вход — с вторым выходом блок;:. 13 носстанонления. Первый вход

-.ðåòüåãî коммутатора 4 соединен с выходом нходно го блока l, второй вход — с тр ет ьим выходом ан алогоцифрового преобраэователя 12, третий вхол — с третьим выходом блока 13 восстановления, первый вход четвертого коммутатора 5 соединен с контрол ьным си гналом, второй вход — с четвертым выходом аналого-цифрового преобраэователя 12, третий вход — с четнертым выходом блока 13 восстановления, первый вход пятого коммутатора 6 соединен с контрольным сиги «иом, второй вход — с пятым выходом аналого-цифрового преобраэователя 12, третий вход — с пятым выходом блока

13 восстановления, первый вход шестого коммутатора 7 соединен с контрольным сигналом, второй вход — с шестым выходом аналого-цифрового пре. образователя 12, третий вход — с шестым выходом блока 13 восстановления, причем четвертый, пятый и шестой входы первого 2, второго 3, третьего 4, четвертого 5, пятого 6 и шестого 7 коммутаторов соединены с вторым, первым и третьим выходами блока l 5 управления, выходы первого

2, второго 3, третьего 4, четвертого 5, пятого 6, шестого 7 коммутаторов соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым входами блока 8 аналоговой памяти, а седьмой вход — с выходом генератора 14 тактовых импульсов, иервь»й, второй, третий выходы блока 8 аналоговой памяти соединены с первым, вторым, третьим входами первого блока 9 усреднения, а четвертый, пятый, шестой выходы блока 8 аналоговой памяти соединены с первым, вторым, третьим нходами второго блока 10 усреднения соотнетственно, выход первого блока 9 усреднения соединен с первым нходом блока 11 коррекции, выход второго блока 10 усреднения соединен с вторым входом блока 1! коррекции, третий вход бл» ка коррекции соединен с входом

10 !

50 контрол ьио го си гнал а, а ных» д — с первым входом «налого-цифрового ир» обраэонателя 12.

Блок 15 управления содержит (фиг. 1) первый триггер 16, первый коммутатор 1 7, иервый счетчик 18, второй триггер !9, комиаратор 20, первый элемент ИЛИ 21, второй элемент ИЛИ 22, второй коммутатор 23, второй счетчик 24, третий триггер 25, причем первый вход компаратора 20 является первым входом блока 15 управления, второй нход соединен с шиной синхрониэации, а выход — со ВТо рым входом первого триггера 16, первый вход первого элемента ИЛИ 21 является вторым входом блока 15 управления, первый вход первого триггера

16 соединен с выходом первого элемента ИЛИ 21 а выход является вторым выходом блока 15 управления, первый вход первого коммутатора подключен к выходу первого триггера 16, второй вход — к первому входу второго коммутатора 23 и является третьим входом блока 15 управления, а выход соединен с первым входом первого счетчика 18, второй вход которого соединен с первым входом второго элемента ИЛИ 22 и с первым входом первого триггера !6, выход первого счетчика 18 подключен ко второму входу второго триггера и ко второму входу первого элемента ИЛИ 21, а выход второго триггера 19 подключен ко второму входу второro коммутатора 23 и является первым выходом блока 15 управления, а выход второго коммутатора 23 соединен с вторым входом второго счетчика 24, первый вход которого соединен с перными входами третьего триггера 25 и первого элемента ИЛИ

21 а выход второго счетчика 24 соединен со вторым входом третьего триггера 25, выход которого является третьим выходом блока 15 управления, и со вторым входом второго элемента

ИЛИ 22, ныход которого подключен к пер ному входу второ го три г гера 19.

Устройство работает следу»»ицим обривом.

Перед началом работы обнуляется первый 18 и второй 24 счетчики, первь»й 1Ь, второй 19 и третий 25 триггеры устанавлинаются в исходное состояние.

1492 313

Вх<)дн го 3, тр с.— ть< го 4 коммутаторов, на первые входы четверт«го 5, пятого 6 и шестого 7 коммутаторов подается контрольный си гнал калиброванной амплитуды °

При превышении входным си гн алом уровня синхронизации Ь, компаратор

20 вь<рабать<вает импульс, который переводит триггер 16 в единичное состояние, подключая тем самым исследуе мый и контрольный си гн алы н а входы блока 8 аналоговой памяти, сигнал с первого триггера 16 разрешает прохождение импульсов записи с генератора тактовых импульсов 14 через первый коммутатор 17 на вход первого счетчика 18.

Емкость первого счетчика 18 равна емкости блока 8 аналоговой памяти.

Импульс пере полнения первого счет чика IS поступает на вход второго триггера ) 9 и переводит его в единичное состояние, а также поступает на вход первого триггера через первый элемент ИЛИ 21 и переводит его в нулевое состояние, на этом э аканчивается процесс быстрой записи мгновенных значений исследуемо го сигнала в аналоговом виде в блок 8 аналоговой памяти. Выход второго триггера 19 подключен к пятым входам аналоговых коммутаторов, обеспечивая тем самым подключение выходов ан ало го-цифро вого преобразователя 12 к соответствующимм входам аналоговых коммутаторов. Одновременно с этим сигнал со второго триггера 19 поступает íà генератор 14 тактовых импульсов, который начинает вырабатывать

С данного момента начинаются процессы медленного считывания из блока 8 аналоговой памяти, усреднения в блоках 9 и 10 усреднения, корректирования в блоке 11 коррекции, преобразования в код в АЦП 12 и записи в ту же аналоговую память, Одновременно с началом считывания информации си гн алом со второ г<> три ггера 19 разрешается прохождение импульсов считывания через вз орой коммутатор 23 на вход второго счет ика 24. Емкость второго счетчика 24 равна емкости аналоговой памяти. Импульс пере полнения второго счетчика

24 поступает на вход гретьего триггера 25 и устанав <ия;и т его в едияичное с«ст«ян«<,;< т;«<: < по< тупас т и» вх«л вт«ро«г1и<(J ерл 19 чс.рея второй элемент 1П11 2 и переводит

5 его в нуле вое « с.т<. яиие. Выход третьего тригг< pa 25 подключен к шестым входам аналоговых коммутаторов 2- 7, чем обеспечивается прохождение информации с вь<хода блока 8 аналого10 вой памяти через блок 13 восстановления, выполняющий функцию восстановления логических уровней для записи обратно в блок 8 аналоговой памяти

Таким образом, информация, считы— ваемая из блока 8 аналоговой памяти, замыкается в кольцо, обестечивая циркуляцию кода записанного сигнала и ег< циклический вывод.

20 Ф о р м у и а и з о б р е т е н и я

Устройство для регистрации формы однократных зле кт ри че с ких сигналов, содержащее входной блок, три аналоговых коммутатора, блок аналоговой памяти, блок корре кции, аналого-цифровой преобразователь, блок восстановления, блок управления, генератор тактовых импульсов, вход котороз0 го соединен с первым выходом блока управления, а выход — с вторым входом аналого-цифрового преобразователя, с управляющим входом блока аналоговой памяти и третьим входом блока управления, о тл и ч а юще

) е с я тем, что, с целью повышения точности, в него введены три аналоговых коммутатора, два блока усред„нения, причем первый вход первого аналогового коммутатора соединен с выходом входного блока, второй вход соединен с первым вь<ходом аналогоцифрового преобразователя, а четвертый, пятый и шестой входы лодключены

45 к втоРому, пеРвому и тРетьему выходам блока управления соответственно, первый вход второго аналогового коммутатора соединен с выходом входного блока, второй вход соединен с вторым

50 выходом аналого-цифрового преобразователя, а четвертый, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления соответственно, первый вход третьего аналогового коммутатора соединен с выходом входного блока, второй вход соединен с третьим выходом аналогоцифрового преобразователя, а четвертый, пятый и шестс и входы подключены

I 4Ч2313 с<1< < т l<< т от Бе ll ll<< < 11 I

<- «< твет отвую1шсми выходами аналогоBoI! памяти, а выходы подключены соотв<.гственно к третьим входам аналоговых коммутаторов и являются выходами устройства, первый, второй и третий выходы аналоговой памяти соек второму, первому и третьему выхо- 10 дам блока управления соответственно, первый вход пятого аналогового коммутатора соединен с шиной контрольного сигнала, второй вход соединен с пятым выходом анэлого-цифрового преобразователя, а четвертыш, пятый и шестой входы подключены к второму, первому и третьему выходам блока управления соответственно, первый вход шестого аналогового коммутатора соединен с шиной контрольного си гнала, второй вход соединен с шестым выходом аналого-цифрового преобразователя, а четвертый, пятый и шестой вхо— ды подключены к второму, первому и 25 третьему выходам блока управления динены соответственно с первым, вторым и третьим входами первого блока усреднения, четвертый, пятый и шестой выходы аналоговой памяти соединепы с первым, вторым и третьим входами второго блока усреднения, а выходы первого и второго блоков усреднення соединены с первым и вторым входом блока коррекции, третий вход соединен с шиной контрольного сигнала, а выход соединен с первым входом аналого-цифрового преобразователя, первый вход блока управления связан с выходом входного устройства, а второй вход — с шиной "Готов".

Составитель !1. Стройко .<а

Редактор И. Горная Техред Л.Олийнык Корректор Н. Бугренкова

Заказ 387«! 4<3 Тирам 713 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производствеl(HQ-è÷IIàòåëüñêèÈ комбинат ")1атент", r . У1кгорс>д, ул. Гагарина, 101