Устройство для передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники ,в частности, к устройствам передачи информации. Цель изобретения - повышение функциональной надежности устройства путем обеспечения синхронизации управляющих импульсов. Устройство содержит группу формирователей, формирователь импульса "сброс", две группы триггеров, два триггера, генератор импульсов, группу счетчиков, шифратор, регистр адреса, блок постоянной памяти, регистр, четыре группы элементов И, три элемента И, группу инверторов, шесть элементов ИЛИ, два элемента задержки. Устройство позволяет за счет обеспечения синхронизации управляющих импульсов поступающих с формирователей на элементы и узлы устройства повысить стабильность длительности импульсов, формирующих адрес сообщения, хранящегося в блоке постоянной памяти, и, как следствие, снизить вероятность ложной выдачи сообщения на объект. 3 илл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5у 4 0 08 С 19/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А8ТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

IlPH ГКНТ СССР (21) 4321395/24-24 (22) 26.10.87 (46) 07.07.89. Бюл.й 25 (72) О.К,Фомичев, А.Н.Романов, Ю.Ю.Бельских и 0.Б.Грабовский (53) 621.398(088.8) (5e) Авторское свидетельство СССР

У 1300540, кл. G 09 G )/00, 1987. (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ (57)Изобретение относится к автоматике и вычислительной технике, в частности к устройствам передачи информации. Цель изобретения — повышение функциональной надежности устройства путем обеспечения синхронизации управляющих импульсов. Устройство

Из обретение относится к автоматике и вычислительной технике, в частности к устройствам передачи информации, и может быть использовано для передачи сообщений между объектами автоматизированной системы.

Цель изобретения — повышение функциональной надежности устройства путем обеспечения синхронизации управляющих импульсов.

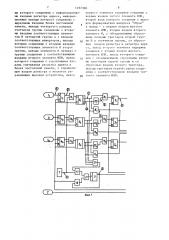

На фиг.1 и 2 представлена функциональная схема устройства; на фиг.3 временные диаграммы, поясняющие работу устройства.

Устройство содержит группу формирователей 1,-1„, формирователь 2 импульса "Сброс", первую 3,-3 „ и вторую 4 -4„ группы триггеров, первый 5

„„SU„„1492360 А 1 содержит группу формирователей, формирователь импульса "Сброс", две группы триггеров, два триггера, генератор импульсов, группу счетчиков, шифратор, регистр адреса, блок постоянной памяти, регистр, четыре группы элементов И, три элемента И, группу инверторов, шесть элементов ИЛИ, два элемента задержки. Устройство позволяет за счет обеспечения синхронизации управляющих импульсов поступающих с формирователей на элементы и узлы устройства повысить стабильность длительности импульсов, формирующих адрес сообщения, хранящегося в блоке постоянной памяти,и, как следствие, снизить вероятность ложной выдачи сообщения на объект. 3 ил. и второй 6 триггеры, генератор 7 импульсов, группу счетчиков 8„-8„, шифратор 9, регистр 10 адреса, блок 11 постоянной памяти, регистр 12, пера орут 14 -14 „ тью 15, †15 и четвертую 16» 16„ группы элементов И, первый 17, второй 18> и третий 19 элементы И, группу 20420 инверторов, первый 21, второй 22, и третий 23, четвертый 24, пятый 25 и шестой 26 элементы ИЛИ, первый 27 и второй 28 элементы задержки, информационный 29 выход устройства и управляющий выход 30 устройства.

Устройство работает следующим образом.

После включения устройства оператор переводит его в исходное состоя1492360

4 ние нажатием клавиши формирователя 2 импульса "Сброс". Импульс

"Сброс" с выхода формирователя 2 поступает через элемент ИЛИ 25 на

R-входы триггеров 4» -4 „, счетчиков 8,-8„, регистра 12, регистра 10 адреса, а также на вход элемента

ИЛИ 26, с выхода которого импульс

"Сброс" поступает на R-входы триггеров 3,-3,„ и триггера 6. В исходном состоянии на прямом выходе триггеров 5 (Т-триггер) устанавливается

Низкий потенциал (логический ноль).

Если по каким-либо причинам после включения устройства на выходе триггера 5 будет высокий потенциал (логическая "1"), то импульс "Сброс", пройдя через открытый элемент И 18 и элемент ИЛИ 21, поступает на счетный вход триггера 5 и устанавливает его в исходное состояние.

В процессе работы при необходимости немедленного формирования и передачи сообщения оператор нажимает клавишу соответствующего формирователя (например, 1„ с мнемоническим названием сообщения).

Весь цикл формирования устройством сообщения можно разделить на два этапа ° Первый — формирование кода адреса сообщения, второй — выборка из блока 11 постоянной памяти кода сообщения го соответствующему адресу и выдача в канал связи с объектом с информационного выхода регистра 12.

Импульс с выхода формирователя 1< (диаграмма А, фиг.3) поступает на установочный Я-вход триггера 4»,устанавливая его в состояние, при котором на прямом выходе триггера 4 по» является высокий потенциал (диаграмма В, фиг.3). Этим потенциалом открывается элемент И 13,, через кото рый тактовые импульсы с выхода генератора 7 (диаграмма Б, фиг.3) поступают на счетный вход счетчика 8». В момент поступления второго тактового импульса на счетный вход счетчика 8 на его выходе "2" появляется высокий потенциал (диаграмма Г, фиг.3), который через открытый элементИ14, поступает на установочный S-вход триггера 3», устанавливая его в единичное состояние. Элемент И 14» открыт высоким потенциалом, поступающим на него с выхода инвертора 20„(диаграмма К, фиг.3), на вход которого пода5

55 ется низкий потенциал с выхода "4" счетчика 8 (диаграмма И, фиг.3).

На прямом выходе триггера 3» появляется высокий потенциал (диаграмма Д, фиг.3) которым через элемент

ИЛИ 23 устанавливается в единичное состояние триггер 6 (диаграмма Д, фиг.3) и открывается элемент И 15» .

Кроме того, высокий потенциал с выхода "2" счетчика 8, поступает через элемент ИЛИ 24 на вход элемента

И 17 (тем самым открывая его). Тактовые импульсы с выхода генератора 7 поступают через открытый элемент И 17 и элемент ИЛИ 21 на синхровход триггера 5, причем триггер 5 срабатывает по заднему фронту импульса, поступающего на его вход (диаграмма Е фиг.3).

Первый импульс, сформированный триггером 5 после нажатия клавиши формирователя 1,, проходит через открытый высоким потенциалом с прямого выхода триггера б элемент И 19 на втовторые входы элементов И 15, — 15 .

Открыт только элемент И 15» . Пройдя элемент И 15,, импульс поступает на первый информационный вход (разряд) шифратора 9, на остальных входах логические "0", На выходе шифратора 9 из комбинации "10.. ° 0" формируется код адреса сообщения, записанного в блоке 1! постоянной памяти.

Кроме того, импульс с выхода элемента И 19 (диаграмма Ж, фиг.3) поступает на вход элемента 28 задержки и на управляющий вход записи регистра 10 адреса, в который записывается код адреса сообщения, поступающий с информационного выхода шифратора 9 на информационный вход регистра 10 адреса.

С выхода элемента 28 задержки (диаграмма 3, фиг,3) импульс поступает через элемент ИЛИ 26 на сбросовые

R-входы триггеров 3»-3 и триггера 6, устанавливая (подтверждая) их в нулевое состояние, К тому же моменту времени на выходе "4" счетчика 8, появляется высокий потенциал (диаграмма И, фиг.3), который открывает элемент И 16, и закрывает через инвертор 20 эле» мент И 14» (диаграмма К, фиг.3) . С поступлением на счетный вход счетчика 8, шестого тактового импульса на его выходе "2" появляется второй импульс (диаграмма Г, фиг.3), который проходит через открытый элемент И 1», 5 149 (диаграмма Л, фиг.3) и поступает на управляющий вход записи регистра 12, на управляющий выход 30 устройства (для синхронизации выдачи устройством и приема объектом сообщения), через элемент ИЛИ 22 на вход элемента 27 задержки и управляющие входы считывания регистра 10 адреса и блока 11 постоянной памяти.

Код сообщения, считанный из блока 11 постоянной памяти по соответствующему адресу, поступает в регистр 12,а с информационного выхода регистра 12 по информационной шине на выход устройства 29. С выхода 29 сообщение поступает в канал связи с объектом.

Следует отметить, что информационные выходы регистра 12 не блокируются при записи в него информации, а следовательно, уже при записи в регистр 12 информации, на его выходах присутствует информация (например, если регистр выполнен на RS-триггерах), После окончания процесса перезаписи кода сообщения из блока 11 постоянной памяти в регистр 12 и выдачи его в канал связи, импульс (диаграмма М, фиг,3) с выхода элемента 27 задержки проходит через элемент

ИЛИ 25 и устанавливает устройство в исходное состояние.

Выдача любого другого сообщения осуществляется аналогично.

Таким образом, предлагаемое устройство позволяет синхронизировать управляющие импульсы, поступающие от формирователей и генератора импульсов на элементы и блоки устройства, и тем самым повысить надежность его функционирования °

Ф о р м у л а и з о б р е т е н и я

Устройство для передачи информации, содержащее группу формирователей, формирователь импульса пСброс", первую группу триггеров, первый и второй триггеры, генератор импульсов, блок постоянной памяти, регистр, первую, вторую и третью группы элементов И, первый элемент И, с первого по пятый элементы ИЛИ, первый и второй элементы задержки, выход генератора импульсов соединен с первым входом перього элемента И, выход перво2360

6 го элемента ИЛИ вЂ” с входом первого триггера, выход третьего элемента

ИЛИ вЂ” с установочным входом второго триггера, выход второго элемента ИЛИ— с входом первого элемента задержки, выходы элементов И второй группы- с установочными;.входами соответствующих триггеров первой :руппы, прямые выходы которых соединены с первыми

10 входами соответствующих элементов И третьей группы, информационные выходы блока постоянной памяти соединены с соответствующими информационными входами регистра, информационные выходы которого являются группой информационных выходов устройства, о т— л и ч а ю щ е е с я тем, что, с целью повышения функциональной надежности устройства путем обеспечения синхронизации управляющих импульсов, в него введены вторая группа триггеров, группа счетчиков, шифратор, регистр адреса, четвертая группа элементов И, второй и третий элемен15

25 ты И, группа инверторов, шестой элемент ИЛИ, выход каждого формирователя соединен с установочным входом соответствующего триггера второй группы, выход каждого иэ которых соеди30 нен с первым входом соответствующего элемента И первой группы, вторые входы которых соединены с выходом генератора импульсов, а выходы — со счетными входами соответствующих

35 счетчиков группы, выход второго разряда каждого из которых соединен с первым входом соответствующего элемента И второй группы, с первыми вхо40 дами соответствующих элементов И четЭ вертой группы и с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход которо45 го соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого объединен с первым входом третьего элемента И и со50 единен с выходом первого триггера, второй вход третьего элемента И соединен с выходом второго триггера,а выход — с входом второго элемента задержки, с управляющим входом записи

55 регистра адреса и с объединенными вторыми входами элементов И третьей группы, выходы которых соединены с соответствующими информационными входами шифратора, информационные выхо)492360 ды которого соединены с информационными входами регистра адреса инфарма1 ционные выходы которого соединены с адресными входами блока постоянной памяти, выходы четвертого разряда счетчиков группы соединены с вторыми входами соответствующих элементов И четвертой группы и с входами соответствующих инвертарав, выходы которых соединены с вторыми входами соответствующих элементов И второ . группы, выходы элементов И четверт;й группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с управлюшими вха— дами. считывания регистра адреса и блока постоянной памяти, с управляющим входом регистра и является управляющим выходом устройства, выход первого элемента задержки соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходам формирователя импульса "Сброс"

5 а выход — с первым входом шестого элемента ИЛИ, вторым входам BToporo элемента И, с объединенными сбросо— выми входами триггеров второй группы И и счетчиков группы, со сбросавым входом регистра и регистра адрес а, ныхад в арага элемента задержки соединен с вторым входам шестого эл е мент а ИЛИ, выход катар or о с а единен с объединенными сбрасовыми входами триггеров первой группы и са сбрасовым входом второго триггера, выходы триггеров первой "руппы соединены с соответствующими входами тре2о тьега элемента ИЛИ, l 492360

Составитель В.Струков

Редактор Г.Волкова Техред А.Кравчук Корректцр Н.КоРоль

Заказ 3879/51 Тираж 518 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 1

11 II

Г н 101