Устройство для измерения электрических параметров в цепях переменного тока

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и может быть использовано в энергетических информационно-измерительных системах. Цель изобретения - повышение точности. Преобразование входных сигналов производится в параллельных аналоговых и цифровых каналах. В устройстве отсутствуют высокоточные нелинейные блоки и аналого-цифровые (АЦП) и цифро-аналоговые преобразователи (ЦАП) большой разрядности. Для обработки в параллельных каналах в устройство введены второй - пятый сумматоры 2-5, второй - шестой ЦАП 7-11, второй - пятый АЦП 13-16, первый и второй блоки 18 и 19 памяти, множительный блок 20, первый - третий фильтры 21-23 нижней частоты, первый и второй квадраторы 26 и 27. Кроме того, устройство содержит первый сумматор 1, первый ЦАП 6, первый АЦП 12, умножитель 17 частоты, определитель 24 периода, вычислительный блок 25 и перемножитель 28. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИЯ

РЕСПУБЛИН (51) 4 С 01 R 21/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ГТНРЫТИЯМ

ПРИ ГКНТ СССР

К Д ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4342449/24-21 (22) 14.12.87 (46) 15.07.89. Бюл. F9 26 (71) Куйбышевский политехнический институт им, В.В.Куйбышева

1-72) А.М.Косолапов, В.С,Баскаков, В.С.Мелентьев и В.С.Шутов (53) 62 1,3 17,382(088,8) (56) Авторское свидетельство СССР

М 1064221, кл, G 01 R 21/06, 1983.

Авторское свипетельство СССР

Р 1126890, кл. G 01 R 21/06, 1984, (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ В ЦЕПЯХ ПЕРЕМЕННОГО ТОКА (57) Изобретение относится к электроиэмернтельной технике и может быть использовано в энергетических информационно-измерительных системах, „„SU„„1493956 A 1

Цель изобретения — повышение точности. Преобразованйе входных сигналов производится в параллельных аналоговых и цифровых каналах. В устройстве отсутствуют высокоточные нелинейные блоки и аналого-цифровые (АЦП) и цифроаналоговые преобразователи (ЦАП) большой разрядности. Для обработки в параллельньм каналах в устройство введены второй — пятый сумматоры 2-5, второй — шестой ЦАП 7-11, второй — пятый АЦП 13-16, первый и второй блоки 18 и 19 памяти, множительный блок 20, первый — третий фильтры 2 1-23 нижней частоты, первый и второй квадраторы 26 и 27. Кроме того, устройство содержит первый сумматор 1, первый ЦАП 6, первый

АЦП 12, умножитель 17 частоты, определитель 24 периода, вычислительный блок 25 и перемножитель 28. ил.

Изобретение относится к электроизмерительной технике и может быть использовано н энергетических инфор-. мационно-измерительных системах.

Цель изобретения — поньппение точности измерения электрических параметров.

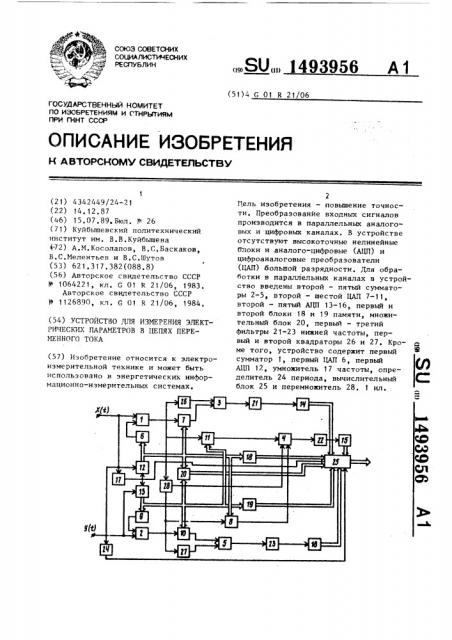

На чертеже представлена структурная схема устройства для измерения электрических параметров в цепях переменного тока.

Устройство содержит первый-пятый аналоговые сумматоры 1-5, первый-шестой цифро-аналоговые преобразователи (ЦАП) 6-11, первый-пятый аналого-цифровые преобразователи (АЦП) 12-16, ум»»ожитель 17 частоть», первьп и второй блоки 18 и 19 памяти, множительный блок 20, первый-третий фильтры

21-23 нижних частот (ФНЧ), определитель 24 периода, вычислительный блок 25, первый и второй квадраторы

26 и 27 и перемножитель 28, причем первый вход первого сумматора 1 сое- 25 динен с выходом первого ЦАП 6,кодовые входы которого соединены с выходами первого АЦП 12, тактирующий вход которого соединен с выходом умножителя 17 частоты и тактирующим 30 входом вычислительного блока 25, дополнительный тактирующий вход которого соединен с выходом определителя

24 периода, вход которого соединен с входом умножителя 17 частоты и

35 подключен к входной шине напряжения контролируемой цепи, вход первого

АЦП 6 соединен с входной шиной напряжения контролируемой цепи и вторым входом первого сумматора ), выход 40 которого соединен с первым входом перемножителя 28, входом первого квадратора 26, аналоговым входом шестого ЦАП 11 и аналоговым входом нтоРОГО ЦАП 7, кОДОВые ВХОДИ KQTopoI o 45 соединены с выходами первого АЦП 12, нходами первого сомножителя множительного блока 20, кодовыми входами третьего ЦАП 8 и входами первого блока 18 памяти а выход — с первым вхоФ

50 дом третьего сумматора 3, второй вход

l которого соединен с выходом первого квадратора 26, а выход — с входом первого ФНЧ 21, выход которого соединен с входом третьего АЦП 14, выходы

55 которого соединены с четвертыми кодовыми входами вычислительного блока 25, третьи кодовые входы которого соединены с вьпсодами множительного б»»ока 20, входы второго сс.-»»: жи которого с<>единень» с ныхлламц BT . го АЦП 13, кодовыми входа"ill »еTBeгтого, пятого и шестого 1!АП 9,»О и 11 и входами»»тс>рого блока 19 памяти, выхлды кс тлрлго следил цы лл вторыми кодовыми входами»»ь»ч»»с>»>»» .»нного блока 25, выход четвертлго ЦАП 9 соединен с первым вхлдлм втсрогo сумматора 2, второй вход ко> »лрсгл соединен с входной шиной тока»li>»» Tpo>tèpóåмой цепи и входом нторог > АI!П »3, а выход — с вторым входом llcремнлжителя 28, аналоговыми вхл;»ам»» третьего и пятого ЦАП 8 и 1О и вхолэм второго квадратлра 27, »»ых»д » лтлрогл соединен с пернь»м »»хог»л . я . »:> сумматора 5> второй вход клторого соединен с выходом пятого ПА!1 1О, а выход — с входом третьего ФНЧ 23, выход котлрог» соединен л вхлллм пятого

АЦП 16, выходы котлрогл сс,п»н Hb» с шестыми кодовыми входам»» вь»»»»с>»>»тельного блока 25, тактирующий вход которого соединен с тактирую»»»>»» входом второго AI!II 13, вьгход .»ерсмножителя 28 соединен с первым нх д:и четвертого сумматора 4 второй и третий входы которого слеп»»>»ечь» с выходами третьего и шестого 1\АП 8 и 11, а вы-. ход — с входом второго Ф1!Ч 22, выход которого соединен с вхс>лом »етвертого АЦП 15, выхлдь» » лтлрлгc соединены с пятыми кодов>»»»» н.сдами вычислительного блока 25> первые кодовь»е входы которого с (>päöí ны с выходами первого блока 18 памяти, а выходы являются ныхлдл.» устрой"тва.

Устройство для измерения электрических параметров в целя.. 1ер менного тока, работает с»»с-»»ую»»»»»м обра зом.

Сигнал х(г.)=KOBU(t ),. со: гt»eтствуюший напряжению I (t) клнгрл.» ируемой цепи, подается:на пер>мй вход сумматора 1, на первый вход ЛПП 12, на вход определителя 24 перис>да. Сигнал

y(t)=K,i(t),соответствующий току

1(с.) контролируемой цепи, плдается на первые входы сумматора 2 и АЦП 13.

На тактирующие нходы АЦП 12, 13 и вычислительного блока 2 подается сигнал с выхода умножителя 17 частоты. На выходе АЦП 12 сформируется

КОД N,>,КотОРЬ»И ПРИ ПОГ» УПЛР»»И»» Очсредного тактирующего импульса подается на цифровые вхолы ПАП 6,7,8, а также на вход блока 18 памяти и нход

1493956

)верного сомножителя множительного блока 20. На вьгходе 1(А((6, в соответствии с кодом N, сформируется сигнал Х, который подается на второй вход сумматора 1. На выходе сумматора 1 будет дPécòíëi)ÿòb сигнал

Cx(t)-X,1. На вьгходе А((П 13, в зависимости от неличины сигнала y(t)) сформируется код И. который при х поступлевии очс р< дногo тактирующего импулн(-я, п<)да(-тся ttа управляющие (цифровыг) входь) ЦАП 9, 10, 11, а такж н<1 вход бл ка 19 памяти и вход вто()ОГО сомножитРля множительного блока 20. На выходе ЦАЛ вЂ” 9, в соответс rifi(it с кодом J сформируется сиг1 нал Y, который подается на второй вход сумматора 2. На выходе сумматора 2 будет действовать сигнал t y(t)—

-Y 7. Аналоговьл1 сигttaa (x(t)-Х; 7 подается на входы: перв)го квадратора 26, 1(АЛ 7,11, первь(й вход перемножителя 28. Аналоговый сигнал (у(t) Y. )подается на входы: второго квадратора 27, ЦАП 8, 10, второй вход перемножителя 28. На вьгходах перечисленных блоков будут действовать =игналы:

К 1. б (-х () " х7= к2м;Гх(t) х 7

Х„= К N гх()- X)J

11

Х., = К„(У((,-у 1

Х9 = Кв. (y(.)-,)

Х„= K„(;(У(с)-Y,)

Х вЂ” К- l-(t)-Х (y(t)- )) где i, j — номера опорных сигналов н каналах Х и У соответственно °

Если положить ко-1ффициенты передачи указанных блоков равными Кгб =1, =2Y ; К 1 =1, то их выходные сигналы запишутся в ниде:

У =(x(t) Х,.12

Х = 2X;(x(t)- XI J

Y, (x(t) X,J

Х„= (y(t)-Ъ,)1

Х, = X;(y(t)-Yi)

Х,. = 2Y (y(t) -у, )

Х„=(х()-XJ)(y(t)- )

Одновременно будут с(рормированы следую(((ие цифровые сигналы: на выходе блока 18 памяти сигнал N<<,соответствующий величине Х .; на вьжоХ1.

t де блока 19 памяти — сигнал N,соот1 |j ветствующий величине Y ., на выходе множительного блока 20 сигнал N 1<, соответствующий величине )(;7 1, кото" рь)е подаютс tta первы)(, второй, третий кодовые входы вычислительного блока 25 соответственно, 5

Сигналы Хгби Х .„подаются на первый и второй входы сумматора 3, выход которого через ФНЧ 21 соединен с входом А((П 14. На входе АПП 14 действует сигнал т

1 (Х, = — ) (2X,. (x(t)-X;)+(x(t)-Х ) фс а на его выходе — коц (2 соответf1 ствующие сигналу

Сигналы )(„, )(, )(1 подаются на первый, второй и третий входы сумматора 4,вь(ход которого через ФН { 22 соединен с входом А((П-15. На выходе

20 Ailll 15 действует сигнал:

t х = -)(Jx(<.)-х J(y(t)-y ) +х,(y(t)—

1 — Y, ) + Y, (x (t) -X; ) Ji d t, 25 à íà его выходе — код N, соответствующии сигналу Х1

Сигналы Х27и Х, подаются на первый и второй входы сумматора 5, выход которого через ФНЧ 23 соединен с вхо30 дом АЦП 16, На выходе А((П 16 действует сигнал:

1

X„= ò †) " У()-YJ7 +jy(t)-Y>) dt, а на его выходе — код N соответ(б

35, ствующий сигналу )(< 1б

Сигналы М,, ()<, "J1 подаются на

1<) четвертью, пятый и шестой кодовые входы вычислительного блока 25, в кото40 ром осуществляется их цифровое интегрирование эа период входного сигнала Т

1 л

И, = — > (N«)Ä(1), 1Ф (45 „1

N -;Е (Nyo).,(2)

П it1,1

И,,- - ;Å (и„) (3)

<1 >

5О где и — число тактирующих импуЛьсов на выходе умножителя 17 частоты эа период входного сигнала, Затем в вычислительном блоке 25 вь2полняются операции суммирования слеДующих Сигналов ((),, )," N г + N 1 (4) (Nag)g = Ng+ ()(1 (5) (Nгg) э = Nг + N1б (6) 14939>б чинам:

+ Х

25)2

+ X).(y((-) Т (N ) v )+v

20 получим

30

40 (8) (9) Учитывая линейность операции интегрирования, результаты суммирования будут соответствовать следую)яим нели $ ((x(t) — >() +2 X,(x(t)-А.7 °

О т .) dt = — (x (t) dt; т

;, ) ((.(<) >f,)(y(t) <,f+ о — У;7+ Ъ, (x(t)-Õ, ) +Х,.У IdC= т

x(t)(t)dt;

О т

t (y(t)-Y 7 +2y (y(t) .(dt = — t y (t)dt. о

При выполнении условия К „ = К; = 1 т (>> „), = — 3 и (t) dt; е (> 25) 2 NP

<) т (N ) = — ) i (t) d(:. (>

В ходе дальнейшей обработки кодов, производимой в вь)числительном блоке 25, выполняются следующие операции: извлечение квадратного корня из сИГнаЛОВ (.< 2g) ) И (N 25) з прИ ВЬ!ЧИСленин деЙствующих значений тока и напряжения соответственно: умножение сигнала ()(2,)2 на интервал времени 2Т, за который определяе.<ся величина энергии

4 ) N f =dT(N 25) g = д ТРср = b TNp; (7) вычисление значений полной и реак тивной мощности согласно соотношениям соответственно

Ng =

25 < 25 3

5)

Формула изобретения

Устройство для измерения электрических параметров в цепях переменного тока, содержащее 1) ерс)(но>к <к ( сумматор, перный вхо„хитер )1 О нен с выходом цифроана furoI»n).n преобразонатечя кот(О <>:е нхо-»ь» fto Tope ãî

C O P JI l » l f P H hi C 1! Ь»Х О;(а МИ:3 H tf! I < > f O П 1» <)) Р О В < >

Г<> 1lpf Об<;а 3 Г»ат:»я, ТЯКТИр,> я(ИЙ чХОД

KOT ЗРОГ<) СОЕДИНЕН С Bb»<1»теля HB т ..т<1 ?? ??????????????????l>»M нхо)<гм в. 1QH(I ч»»т льнРГo бл<)ка > л(>г)< пlптс.)l.ный

TAHITI»pwca: (пп вход кот орс>гn < г,>жи<ен с. вьгходом Опрс .(JIIITpля Ili (и» да,:)ХО>I

KOTOPO 1 O CAP ) ИЛЕ Н С ВХО, 1,)") I."f1 0>Iючен к входной шине напря кения кон f po!IHpVP.»ой цепи, о т л и-Ч а Ю Ш С < O Я TPM„ С Ц(ЛЬК) ПО—

НЬШ»Е Нl»Я < i ) ti ><О(Т) f f . i< - I; ) (>ПО 11;1 > < ПЬ но введены !зторой, трез»<Й, чет(зертый и ЛЯтый ан <логo-"IJèI тый,ff»ры, г-,opof», тр тий, четгертьгi пя тк)Й и:11 - - т(;Й ц И<3) р с 1(Н 1)-, > О Г o R f I! П р Е o t ) p d ) i ) В, З ", t JI l l > д 1 td блока памяти, множитепьнып б ток,два кнадратора и трн фильтра нижних час-. тот, причем вход пер»зог< а 1:<лого-цифPOB At ПР O(>PB 3

ВХОДНОЙ <П»НОй» Нат<РЯжЕН».-1 К»тРОЛИР EMOlf ЦЕ ПИ И В TOPhlM Б ХО!I ) 1 t> t »В )1 О С >dtfi матора, выход которогo <"динан ( первым Bxo)I(>M перемнс>ж»»те>ля. Вхо

ДОМ ПЕРВОГО КН().<тРато)з..з >» Я»»а-IC>-Г 0 Н ЬП» B Х (1Д О М В ТО Р (Г 1 it< r P О i i, а

ЛОГ ОНОГО i!Peon(yaxo>IB TP КОДОВЫЕ вх:;ды которого соединены «pf I . Ода)(и первого аналого-цифроно О прео()г)язс-вателя, входами первого с;м<ожителя множительного блока, к О):<>Bf»I»i» Bxn;(aMH третьего цифг>оаналог )ного Iip! . браз<)вателя и входами перв<- ???? ?? 1 ???? .-(1)????. ????, ?????????? ???????????????????? 1)??????????????:???????????????? !!pp???????????????????????? ?????? a??fft>I C первым

В Х ОДОМ R T 0 P O Г О С УММ а Т О Р -з 13 1 О Р < > и B X O r которого сopдинен с B>xoяlii-Й 1)и)«з<» то ка контролируем(>й l!=, (п I f .((>äoM зтА рого аналого-цизрового прообраз,BaTPля, а выход — с вторы) нхi), (oì п< ремнОжите пя, аналОГARhMH Входами третьего и пятого »ифрг>аналогоньгх преобразователей и входом нт»рого кнад-ратора, выход второго цифроана.тоговс>:— го !зреобразонателя < Оединен с первь)м входом третьего сумматора, второ><

ВХОД тРЕтЬЕГО СУММатОРа <-зЕДИНЕН С выходом перно го к в адра то;> а, а н).»ход с входом первого филь Тра 11»>кнггх час. тот, ньгх<зд кот<зрого соединен с входом третьего аналого-)IH(tpo))oro преобразователя, третьи кодовые гходы ны1493956

1.0

Составитель С.Сафохин

Техред Л.Олийнык Корректор И,Муска

Редактор И.Сегляник с

Заказ 4004/42

Тираж 713 Подписное комитета по изобретениям и открытиям прн ГКНТ СССР

Москва, 1к-35, Раушская наб., д. 4/5

ВЧИИПИ Государственного

113035, Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101 числительного блока соединены с выходами множительного блока, входы второго сомножителя которого соединены с выходами второго аналого-цифрового

5 преобразователя, кодовыми входами четвертого, пятого и шестого цифроаналоговых преобразователей и входами второго блока памяти, выходы которого соединены с вторыми кодовыми входами вычислительного блока, выходы третьего аналого-цифрового преобразователя соединены с четвертыми кодовыми входами вычислительного блока, выход перемножителя соединен с первым 15 входом четвертого сумматора, второй и третий входы которого соединены с выходами третьего и шестого цифроаналоговых преобразователей, а выход— с входом второго фильтра нижних частот, выход которого соединен с входом четвертого аналого-цифрового преобразователя, выходы которого соединены с пятыми кодовыми входами вычислительного блока, первые кодовые входы которого соединены с выходами первого блока памяти, а выходы являются выходом устройстаа,выход второго квадратора соединен с первым входом пятого сумматора, второй вход которого соединен с выходом пятого цифроаналогового преобразователя, а выход— с входом третьего фильтра нижних частот, выход которого соединен с входом пятого аналого-цифрового преобразователя, выходы которого соединены с шестыми кодовыми входами вычислительного блока, тактирующий вход которого соединен с тактирующим входом второго аналого-цифрового преобразователя, выход первого сумматора соединен также с аналоговым входом шестого цифроаналогового преобразователя.