Регулирующий узел преобразователя электрической энергии

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может использоваться в стабилизаторах напряжения или тока, а также в устройствах преобразования энергии постоянного тока в энергию постоянного или переменного тока, регулирующий узел которых построен на N параллельно включенных транзисторах. Цель изобретения - улучшение динамических характеристик путем повышения точности распределения токов и мощностей между параллельно включенными цепями при повышении К.П.Д. Устройство содержит N параллельно включенных транзисторов, в эмиттерные цепи которых включены одинаковые резисторы, а также N - входовый инвертирующий сумматор, дифференциальный усилитель, N двухвходовых инвертирующих сумматоров и N - канальную схему задержки включения, обеспечивающие автомическое установление равномерного распределения токов и мощностей параллельно включенных транзисторов. 2 з.п. ф-лы, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) 9 А1 511 4 С 05 F 1/56, гг

;)I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ fHHT СССР (21) 4289140/24-07 (22) 27.07 ° 87 (46) 15.07.89. Бкл. 11 26 (71) Ленинградский электротехничес кий институт им. В.И. Ульянова (Ленина)

° ° ° °

72) П. E. Иванов и С. Г. Семушин

53) 621. 316. 722. 1 (088. 8) (56) Додик С.Д. Полупроводниковые стабилизаторы постоянного напряжения и тока. И.: Советское радио, 1980, с. 55-57.

Бычков В.А. Схема выравнивания токов параллельно включенных силовых транзисторов./Под ред. И.Ф. Николаевского. Полупроводниковая электроника в технике связи. Выпуск 20. H.:

Связь, 1Д80, с. 201-204.

Патент США 11 3675114, кл. С 05 F 1/56. (54) РЕГУЛИРУ10ЩИЙ УЗЕЛ ПРЕОБРАЗОВАТЕЛЯ ЭЛЕКТРИЧЕСКОЙ ЭНЕР ГИИ (57) Изобретение относится к электИзобретение относится к электротехнике и может использоваться в стабилизаторах напряжения или тока, а также в устройствах преобразования энергии постоянного тока в энергию постоянного или переменного тока, регулирующий узел которых построен на параллельно включенных транзисторах.

Цель изобретения — улучшение динамических характеристик путем повышения точности распределения токов и мощностей между параллельно включенротехнике и может использоваться в стабилизаторах напряжения или тока, а,также в устройствах преобразования энергии постоянного тока в энергию постоянного или переменного тока, -регулирующий узел которых построен на N параллельно включенных транзисторах. Цель изобретения - улучшение .динамических характеристик путем повышения точности распределения токов и мощностей между параллельно включенными цепями при повышении КПД. Устрво содержит N параллельно включенных транзисторов, в эмиттерные цепи кото" рых включены одинаковые резисторы, а

1 также Н-входовый инвертирующий сум- Я матор, дифференциальный усилитель, Н двухвходовых инвертирующих сумматоров и N-канальную схему задержки включения, обеспечивающие автоматическое установление равномерного распределения токов и мощностей параллельно включенных транзисторов. 2 э.п. ф-лы, 1 ил. ными цепями, состоящими из последовательно соединенных транзистора и резистора, при повьппении КПД.

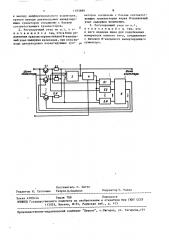

Функциональная электрическая схема регулирующего узла преобразователя электрической энергии представлена на чертеже.

Регулирующий узел преобразователя электрической энергии содержит N pe. гулирующих транзисторов 1 ° 1-1 ° N, к эмиттерам. которых подключены одина. ковые резисторы 2.1-2Л, причем кол лекторы транзисторов соединены с

l 493989 входной силовой шиной, а свободные выводы резисторов — с выходной силовой шиной устройства, последовательно соединенные N-входовой инвертирую5 щий сумматор 3 N входов которого подключены к эмиттерам транзисторов, а выход соединен с шиной для подключения измерителя полного тога, дифференциальный усилитель 4, неинвертирующий вход которого соединен с выходом инвертирующего сумматора 3 и шиной для подключения измерителя полного тока, а инвертирующий вход соединен с шиной для подключения источ- 15 ника управляющего сигнала, а также блок управления, включающий в себя

Б двухвходовых инвертирующих сумматоров 5.1-5.N один вход каждого из которых подключен к выходу дифферен- 20 циального усилителя 4, вторые входы каждого из сумматоров соединены с эмиттерами соответствующих транзисторов, а выходы каждого иэ инвертирую, щих сумматоров соединены с базами соответствующих транзисторов через

N-канальный узел 6 задержки включения.

Регулирующий узел преобразования электрической энергии работает следу- 30 ющим образом.

На входную силовую шину подается питающее напряжение. При этом, на шину для подключения источника управляющего сигнала подается напряже- 35 ние V, которое поступает на инвертирующий вход дифференциального усилителя 4, где инвертируется. Проинвертированное управляющее напряжение—

Ч поступает на инвертирующие сумма- 40

М торы 5. i (i = Г,М), где повторно инвертируется и усиливается в К раэ.

Модуль коэффициента передачи дифференциального усилителя 4 равен единице. . После второго инвертирования и уси- 45 ления в инвертирующих сумматорах 5.1 напряжения К„ V через N " канальный узел 6 задержки включения поступают на базы транзисторов l,i. В результате этого через каждый из транзисторов 50

l.i. В результате этого через каждый из транзисторов 1.i течет ток I который создает на соответствующем эмиттерном резисторе 2.i (i I.N) l с малым сопротивлением R падение напряжения V < = I ° «Р.. Инвертирующий

1 Э сумматор 3 осуществляет суммирование напряжений на эмиттерных резисторах

2 ° i с весами 1/N и формирует на своем выходе напряжение и величина ср> которого прямо пропорциональна среднему току I «(а также суммарному току) через транзисторы I.x

ы н

V p= — — Е I. R - — —, I . й,, Й

=-R «I Э СР

Сигнал с выхода инвертирующего сумматора 3 подается на шину для подключения измерителя полного тока, прямо пропорционального среднему току, протекающему через транзисторы регулирующего узла преобразователя электрической энергии, а также на неинвертирующий вход дифференциального усилителя 4. Дифференциальный усилитель 4 формирует на своем выходе разностный сигнал

r 1

Qy eP Jf 1 поступающий на один иэ входов каждого из инвертирующих сумматоров 5.i

Каждый инвертирующий сумматор 5.i осуществляет сложение сигнала, поступающего с выхода дифференциального усилителя 4, с напряжением, поступающим с выхода соответствующего эмиттерного резистора 2.i — датчика тока, усиление в К раз и инвертирование суммарного сигнала. В результате на выходе каждого из инвертирующих сумматоров 5.i формируется сигнал управления V „; соответствующим транзистором l.i состоящий из суммы сигнала управления током транзистора l.i (К.V ), н сигнала рассогласования (К ° DV у;), направленного на уменьше-. ние разности среднего тока через транзисторы и тока через транзистор

l.i

V Ф К(ЧA„+V,) = К Vy + К R (I p-I ) = К V — К IV

У У

Сигналы управления транзисторами

l,i с выходов инвертирующих сумматоров 5.i поступают через, N-канальный узел 6 задержки включения на базы соответствующих транзисторов 1.i Bo время работы устройства N-канальный уэсл 6 задержки включения передает все N входных сигналов на соответствующие выходы с коэффициентом передачи, близким к единице. Однако, при подключении питающего напряжения к устройству, в начальный момент време1493

Тимд и N T асмо. маркс

20

-25

50 ни вследствие протекания переходнь1х процессов во всех инвертирующих сум- маторах, дифференциальном усилителе

4, а также в цепях питания устройства, на выходах некоторых инвертирующих сумматоров 5.1 могут появиться сигналы, открывающие на короткое время один или несколько транзисторов 1.i. Это может привести к выходу из строя соответствующих открытых транзисторов 1.i (вследствие протекания через них тока, превышающего допустимый) или нагрузки (вследствие того, что ток через нее может оказаться существенно выше требуемого).

Поэтому N-каналып1й узел 6 задержки включения осуществляет задержку подачи открывающего напряжения с выходов инвертируюших сумматоров 5.1 на время протекания переходных процессов во всех сумматорах, дифференциальном усилителе 4 и цепях питания после подключения схемы к источникам питающих напряжений, на входы (базы) тран транзисторов 1.i

По сравнению с регулирующим узлом известного устройства, данное устройство, вследствие подачи управляющего сигнала одновременно на все регулирующие транзисторы, позволяет обеспечить существенно более равномерное динамическое распределение токов и мощностей между параллельно включенными транзисторами. Поскольку в регулирующем узле известного устройства управляющий сигнал подается вначале на один транзистор, а затем на остальные, то, при резком изменении управляющего сигнала или нагрузки, в течение времени задержки подачи сиг нала на все, кроме первого транзисторы, ток через первый транзистор может оказаться существенно больше токов остальных транзисторов. Если при этом ток через первый транзистор окажется больше предельно допустимого импульсного тока для данного типа транзистора, то он может выйти из строя. Таким образом, в динамическом режиме, в течение времени задержки подачи сигнала на остальные транзисторы, значительная часть всего тока нагрузки может протекать через единственный первый транзистор. Поэтому, максимальный ток нагрузки для такого устройства не может быть существенно вьппе предельно допустимого импульсного тока одиночного транзисто989 6 ра I Man макс ЛЛя данного устройства, вследствие одновременной работы всех транзисторов, импульсный ток в нагрузке может достигать величины

Кроме того, благодаря введению

N-канального узла задержки включения, в описываемом устройстве устранен укаэанный ранее недостаток регулирующего узла устройства прототипа, связанный с плохими динамическими характеристиками при его подключении к источнику питания.

Формула изобретения

1. Регулирующий узел преобразователя электрической энергии, содержаший N параллельно включенных цепей, состоящих из последовательно соединенных транзистора и резистора, подключенного одним выводом к эмиттеру транзистора, коллекторы транзисторов подключены к входной силовой шине, а свободные выводы резисторов к выходной силовой шине, и блок управления транзисторами с N входами и N выходами, соединенными с базами транзисторов, причем блок управления транзисторами включает в себя N узлов сравнения и усиления, первый вход

1 каждого из узлов, за исключением первого, подключен к эмиттеру соответствующего транзистора, о т л и ч а юш и и с я тем, что, с целью улучшения динамических характеристик путем повышения точности распределения токов и мощностей между параллельно включенными цепями при повьппении КПД, в блок управления введены N-входовой инвертируюший сумматор, входы которого подключены к эмиттерам соответст" вующих транзисторов, и дифференциаль ный усилитель, один вход которого подключен к выходу инвертирукпцего сумматора, а другой — к шине для подключения источника управляющего сигнала, а узлы сравнения и усиления выполнены в виде двухвходовых инвертирующих сумматоров, первый вход первого из которых является первым входом первого узла сравнения и усиле55 ния, подключенного эмиттеру первого транзистора, а вторые входы всех двухвходовых инвертирующих сумматоров являются вторыми входами всех узлов сравнения и усиления, подключенными

1493989

Составитель С. Ситко

Редактор И. Сегляник Техред П.0лийнык Корректор Т. 11алец

Заказ 4109/44 Тирж 788 Подписное

ВНИИПЙ Государственного комитета по изобретениям и открытиям йрн ГКНТ СССР

113035, Москва, Ж-ÇS, Раушская наб., д. 4/5

Производственно-издательский комбинат "патент", г.уагород, ул. Гагарина,101 к выходу дифференциального усилителя, причем выходы двухвходовых инвертирующих сумматоров соединены с базами соответствующих транзисторов.

2. Регулирующий узел по п.1, о тл и ч а ю шийся тем, что в блок управления транзисторами введен N-канальный узел задержки включения, при этом выходы двухвходовых инвертирующих сум- р маторов соединены с базами соответствующих транзисторов через N-канальный узел задержки включения.

3. Регулирующий узел по п.1, отличающийся, тем, что в него введена шина для подкЛючения измерителя полного тока, соединенная с выходом N-входового инвертирующего сумматора.