Устройство для вычисления квадратного корня

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике ,в частности, к устройствам специализированного назначения, и может быть использовано в самых различных областях народного хозяйства в системах автоматизированного управления при решении уравнений. Цель изобретения - сокращение аппаратурных затрат. Сущность его заключается в установлении новых связей и дополнительных элементов, позволяющих сократить аппаратурные затраты на реализацию устройства для вычисления квадратного корня. Устройство содержит два преобразователя прямого кода в дополнительный 2.1, 2.2, комбинационный квадратор 3, сумматор 4, блок синхронизации вычислений 6, группу триггеров 5. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

КаЪЬ ЛИК (su4 С 06F 7 552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCKOMY СВИ4ЕТЕЛЬСТВУ

4ь

CO

Ю вЬв

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЭОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4367329/24-24 (22) 25.01.88 (46) 15.07.89. Бюл. Р 26 (71) Институт проблем моделирования в энергетике АН УССР и Специальное конструкторско-технологическое бюро средств моделирования с опытным производством Института проблем моделирования в энергетике АН УССР (72) Ю.А.Плющ, З.А.Джирквелишвили, А.П.Стеканов и А.И.Притака (53) 681.325(088.8) (56) Авторское свидетельство СССР

11" 970381, кл. G 06 F 7/552, 1981.

Авторское свидетельство СССР

М 1254476, кл. G 06 F 7/552, 1984. (54) УСТРОЙСТВО ДИ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ

„„SU„„1494004 А 1

2 (57) Изобретение относится к цифровой вычислительной технике, в частности к устройствам специализированного назначения, и может быть использовано в самых различных областях народного хозяйства в системах автоматизированного управления при решении уравнений, Цель изобретения — сокращение аппаратурных затрат. Сущность его заключается в установлении новых связей и дополнительных элементов, позволяющих сократить аппаратурные затраты на реализацию устройства для вычисления квадратного корня.

Устройство содержит два преобразователя прямого кода в дополнительный

2.1, 2.2, комбинационный квадратор

3, сумматор 4, блок 6 синхронизации вычислений, группу триггеров 5. 1 ил.

1494004

Изобретение относитСя к цифровой вычислительной технике, в частности к устройствам специализированного назначения, и может быть использовано в специализированных вычислительных автоматизированных системах управления при решении уравнений.

Цель изобретения — сокращение аппаратурных затрат. 10

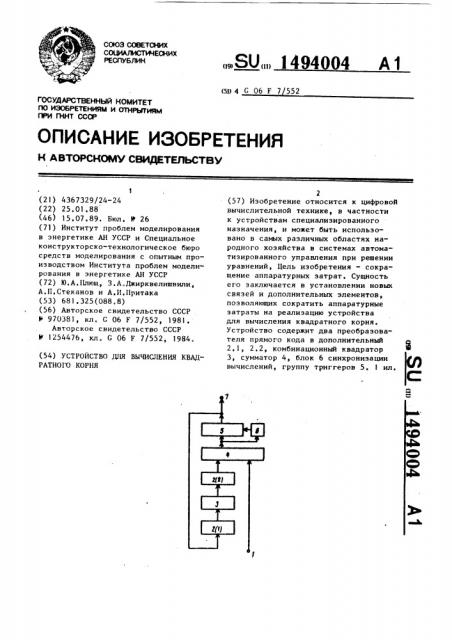

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит вход 1 подкоренного выражения, первый 2.1 и второй 2,2 преобразователи прямого кода 15 в дополнительный, комбинационный ,квадратор 3, сумматор 4, группу триггеров 5, блок 6 синхронизации и выход 7.

Вход 1 устройства предназначен для 20 подачи в устройство числа F из которого необходимо извлечь квадратный корень.

Сумматор 4 представляет собой двухвходовой многоразрядный параллельный сумматор и предназначен для суммирования числа, поданного на вход устройства с числом, поступающим с выхода второго преобразователя 2,2 прямого кода в дополнительный, сдви- 30 нутого на два разряда вправо.

Первый 2.1 и второй 2„2 преобразователи прямого кода в дополнительный предназначены для получения дополнения чисел, поданных на их входы. 35

Комбинационный квадратор 3 предназначен для возведения в квадрат числа, поданного на его вход.

С входами группы триггеров 5 и блока 6 синхронизации вычислений сое- 40 динены старшие и разрядов (и — разрядность искомого) выхода сумматора 4.

Блок 6 синхронизации вычислений предназначен для блокирования пере- 45 записи значения информации с выхода сумматора 4 на входы группы триггеров. Выходы группы триггеров соединены со входом первого преобразователя прямого кода в дополнительный, сдвинутый на один разряд влево. Все блоки устройства могут быть реализованы по любым, широко известным в вычислительной технике схемам. При возникновении зацикливания решения очевидно, что алгебраическая разность невязок на каждом шаге больше или равна единице младшего разряда искомого решения. Таким образом, необходимое условие возникновения зацикливания решения можно записать в виде ю

ДГ,-Х,— F (1) (2) Учитывая, что второе возможное значение Х отличается от Х, на единицу младшего разряда, т.е.

Х,=Х„+ 2 (3) то BFz=(Х„-2 ") -F (4) Вычитая (2) иэ (4), и подставив результат в (1) получим (5) откуда

1,— 2

-и

Х з

2 (6) записав зто выражение через F получим

2 (1-2

F = Х

1

4

I (7) следовательно, значение

Р(— = 0,25, 1 (8) будет необходимым условием отсутствия зацикливания решения.

Устройство работает следующим образом.

Проиллюстрируем работу устройства на примере: при представлении информации четырьмя двоичными разрядами с фиксированной запятой перед старшим разрядом, Подадим на вход устройства число

F равное

F = 0,00110010 с 0,25

После прохождения в устройстве переходного процесса схема установится в состоянии Х 0,0111.

Рассмотрим работу устройства при установившемся значении искомого Х.

Согласно вышеописанным схемным соединениям на вход первого преобразователя прямого кода в дополнительный с выхода группы триггеров поступает значение кода 2Х 0,1110, на вход комбинационного квадратора с выхода первого преобразователя прямого кода в дополнительный будет поступать число, определяемое как дополнение до единицы числа 2Х, т.е. (F-2Х)

=0,0010. С выхода комбинационного квадратора на вход второго преобразователя прямого кода в дополнительй ный будет поступать код числа (F-2X) R

1494004

Составитель 3.Джирквелишнили

Редактор А.Ренин Техред Л.Сердюкова Корректор 3.Лончакова

Заказ 4111/45 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москна, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

0,0000 0100. Второй преобразователь прямого кода в дополнительный сформи. рует величину дополнения до единицы реэультата с выхода квадратора 3, т.е, 1-(1-2Х) =О,llll 1100, которая, 5 будучи сдвинутой на два разряда вправо, поступает на второй вход сумматора, Таким образом, на сумматор будут подаваться числа F--O,OOII 0010 с нхода устройства и число 0,0011111! с выхода второго преобразователя прямого кода в дополнительный. С ныхода сумматора получим число, равное

7+1/4/1-(1-2Х) =0,0111 0001, старшие и (n=4) разряды которого соответствуют установившемуся состоянию схемы, т.е. Х 0,0111.

Ф о р м у л а и э о б р е т е н и я

Устройство для вычисления квадратного корня, содержащее сумматор, первый информационный нход которого соединен с нхсдом подкоренного выражения устройстна, а выход — с нходами группы триггеров и блока синхронизации, выход последнего иэ которых подключен к входу синхронизации группы триггеров, выход которой соединен с входом первого преобразователя прямого кода в дополнительный и с ныходом устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, в него дополнительно введен комбинационный квадратор, вход и выход которого соединены соответственно с выходом первого и входом второго преобразователей прямого кода в дополнительный, выход последнего иэ которых соединен с вторым информационным входом сумматора.