Асинхронный последовательный регистр на кмдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра. Для достижения этой цели в регистр, выполненный на КМДП-транзисторах и содержащий ячейки памяти, состоящие из двух инверторов и двух логических элементов, каждый из которых состоит из четырех транзисторов P-типа и четырех транзисторов P-типа, введены элемент ИЛИ-НЕ и группа из пяти инверторов, а в каждый логический элемент введен пятый транзистор P-типа. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦ)1АЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU„„1494041 (5))4 G 11 С 19/00

: "..)1:) ) )) ) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (2)) 4178570/24-24 (22) 08.01.87 (46) 15.07.89. Бюл. И 26 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина ) (72) В.И.Варщавский, А.Ю.Кондратьев

Н.И.Кравченко и Б.С.Цирлин (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

)) 66)606, кл„ О 11 С 19/00, 1976.

Авторское свидетельство СССР

)) 1136216, кл. G ll С )9/00, 1985. (54) АСИНХРОН))ЫИ ПОСПЕДОВАТЕЛЬН)!Й

РЕП1СТР НА КИДН-ТРАНЗИСТОРАХ (57) Изобретение относится к автомаИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных вычислительных устройств приема и передачи информации, Э

Цель изобретения — упрощение асинхрснного последовательного регистра.

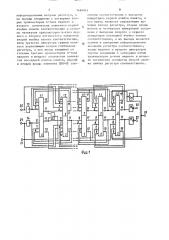

))а фиг.l приведена схема регистра; на фиг.2, 3 и 4 — схемы первой, второй и -й (i ) 2) ячеек памяти регистра, Регистр выполнен на КМДП-транзисторах и содержит ячейки 1 памяти, каждая из которых состоит иэ двух симметричных цепочек 2. Каждая цепочка состоит из логического элемента 9 и инвертора 4. Ячейки имеют: улравля ющие входы 5 (только вторая ячейка памяти), 6, 7 и 8 (кроме первой ячейки памяти), информационный вход 9, инверсный 10 и прямой 11 информацион- тике и вычислительной технике и может быть использовано лри построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра. Для достижения этой цели в регистр, выполненный на КИДП-транзисторах и содержащий ячейки памяти, состоящие из двух инверторов и двух логических элементов, каждый из которых состоит из четырех транзисторов и-типа и четырех транзисторов р-типа, введены элемент ИЛИ-HF. и группа из пяти инверторов, а в каждый логический элемент введен пятый транзистор р-типа.

4 ил. ные выходы, Регистр содержит также элемент ИЛИ-}Б 12 и группу из пяти инверторов 13-17, На фиг.) показаны также управляющий выход 18 записи, управляющий вход 19 считывания, пря- мой 20 и инверсный 21 информационные входы, прямой 22 и инверсный 23 информационные выходы регистра ° 4й

Логические элементы ячеек памяти, кроме первой (фиг.3 4 ), содержат четыре транзистора и-типа 24-27 и пять транзисторов р-типа 28-32, Логический элемент первой ячейки памяти (фиг.2) содержит три транзистора и-типа 24-26 и четыре транзистора р-типа 28-31. Сток четвертого транзистора п-типа 27 логических элементов первой ячейки памяти является управляющим входом 5 ячейки памяти, затвор четвертого транзистора

)494041 р-типа 31 логических элементов каж— дой ячейки плмяти является управляющим входом 6 ячейки памяти, сток третьего т >лнз3>сторл и-тниа 2(> — yll5 р(>вл>3>ощ3<м входом 7, затвор пятого трлнз3<сторл р-типа 32 (3(polie Ilepl>OII ячейки памяти) — управляющим входом

8, затвор второго тр(>33зистора и-тина

25-информациош3ым входом 9, исток первого транзистора и-типа 24 — инверсным информацнош<ым выходом 10, гыход ннвертор,l 4 — прямым 3>нформациnlIiI«IlI выход(>м 11 ячейк33 33лм>3т33.

Асинхрои>3«>й последовательный регистр работает следующим образом.

Состояние ячейкli )+i (значения нл выходах 10, 11, 11, 10) соо>ве>ствуют: ) 010 — в нчс>>3(е з<и>ис >Il >Ióël„

0101 — в ячейке:3;IIII>c.l>í(l е;;>пп>па

1001 — IIII<>op>ill«»I 33 ячейке .i<>c< (рлботЫ РЕГИСтРа В ЯЧЕЙКЕ НЕ ВоЗШ<КЛЕт нз-за наличия перекрестных связей между цепочкам>3 ячейки. 25

Плборы зна<гений нл входах 20, 21 регистра соответствуют: 10 — источник передает нуль. 01 — источник передает единицу, 1) — источник не, передает IIII<3>npllalIIIII в регистр, набор

00 злпре>(<е>3„

Наборы значений 33л выходах 23, 22 соответствуют: )Π— приемник принимает из регистрл нуль, 01 — приемник принимает 3<з регистра «диницу, 11 — приемник не пршшмлеf информлц>ш из регистра, набор 00 запрещен„

Запись в ячейку .i про3<схо>шт тогда, когда и ячейке 1. (i — 1) записа3333формлцин, л в ячейке 1. (3.-2) и

1, (i+1) 3333д>орм(3ц<3>3 либо терта, гп>бо имеет знлчеш>е > прот3>воположное з 33333сываемо Iy. Стирлш>е информации « ячейке 1, 1 ilpollcxagIIIT тогда, когда в ячейке 1.(i+1) записана та же информация.

Пусть В начс>льном состо>13>и33 3п>фо)3мания в регистре отсутствует, f.e. все его ячейки нлхсдятся в состоянии

2001. Пусть также нл входе 19 регистра зафиксировано значение 1, Источник передает в регистр информацию, устанавливая нл его входах 20, 21, например, набор 01, Как толь>(о зтл н><формация запишетс33 з первую ячейку ре55 гистра, на его выходе 23 устлшьвитсн значение 1, Теперь источник может установить на входах 20, 21 регистра набор 1-1 с тем, >тобы затем иередавать новую порцию информации. После этого информация будет записываться во вторую ячейку, л затем — стиряться в первой ° Стирание информации в первой ячейке разрешает ее запись в треть>о н т,д, Клк т(3лько в первой ячейке регистра информация будет. стерта и нл выходе 23 появится значение О, источник может записать в ре-: гистр < slep>I>IIIyl<3 ???????????? ????4>ормации.

Если следующая порция информации имеет значение, отличное от предыдущего, то запись в ячейку 1.(i-1) может осуществляться еще до того, как будет стерта информация в ячейке 1.i.

Если же следующая порция информации

33>>лет то же знл>3ение, что и предыдущая, то такая Запись возможна точько после того, как в ячейке 1.3 информация будет стерта, Таким образом, последовательная передача в регистр порции информации при фиксированном значении 1 на входе 19 прод>олжлется до тех пор, пока не заполнится весь регистр. При этом между двумя ячейками> хранящ>ими соседние порции информации с одинаковьиш значениями, будет находиться одна ячейка, в которой информация стерта, если же значение соседних порций информации различно, то они хранятся в смежных ячейках.

Пусть нл входах 20, Я) регистра зафиксирован набор 11, а в результате запол <ения регистра информацией состояние его последней ячейки—

0101, 11а входах 23, 22 при этом устлно>зится набор 01, Получив эту инф(3рмац33>о, приемник устанавливает нл входе 19 значение О, что вызываеf стирание информации в последней ячейке. В результате, если в последней ячейке и нредгоследней запи<3а ны порц ш >шформл ции с различными значениями, то появляется возмож— ность переписи информации из предпоследней ячейки в последнюю, иначе информация псреписывается из ячейки, предшествующей предпоследней и т.д.

Как только информация в последней ячейке стерта, приемник может установить на входе 19 значение 1, т.е. подготовиться к приему следующей порции информлц ш. Таким образом, последовательный прием информации из регистра при фиксированном наборе 11 нл его входах 20, 21 продолжается до

5 14 тех пор, пока весь регистр не будет очищен, т.е. во всех его ячейках не будет стерта информация, При одновременной работе источника и приемника информации процесс передачи ее протекает аналогично описанному.

Сложность ячейки памяти предложенного регистра составляет 22 КМДПтранзистора, против 28 КМДП-транзисторов в прототипе„ Для хранения одного разряда необходимы в среднем

l,5- ячейки (для чередующихся кодов

1, а для повторяющихся — 2). Периоды работы регистра в режимах записи и считывания составляют соответствен»о 10 и 8 ., где — задержка переключения ЩП-транзистора, 94041

15 второго и четвертого т1 ачзисторов р-тина, а его затвор — с затвором первого транэист6ра и-типа данного логического элемента, сток второго транзистора р-типа которого соединен с истоком третьего транзистора р-типа, сток которого соединен с ис-. током первого транзистора и-типа данного логического элемента и с вхо1 дом соответствующего иннертора данной ячейки памяти и во всех ячейках памяти, кроме первой, — с затвором четвертого, транзистора р-типа соответствующего логического элемента предыдущей ячейки памяти, затворы четвертых транзисторон р-типа первого и . второго логических элементов первой ячейки памяги соединсны с выходами

45

Формула изобретения

Асинхронный последовательный регистр на 1ЛДП-транзисторах, содержащий ячейки памяти, состоящие из двух инверторов и двух логических элементов, причем в каждой ячейке памяти, кроме первой, логические элементы содержат четыре транзистора и-типа и четыре ранэистора р-типа, а в первой ячейке памяти логические элементы содержат три транзистора п-типа ц четыре тра.içèñòîðà р-типа, при этом исток, затвор и сток первого транзистора и-типа логического элемента соединены соответственно с затвором и исток,м первого транзистора и-типа другого логического элемента и с истоком второго транзистора и-типа данного логического элемента, сток которсго во всех ячейках памяти, кроме первой, соединен с истоком четвертого транзистора п-типа данного логического элемента, а затвор — с затвором второго транзистора р-типа данного логического элемента и во всех ячейках памяти, кроме первой, — с выходом соответствующего инвертора предыдущей ячейки памяти, сток четвертого тра..зистора и-типа логического элемента во всех ячейках памяти, кроме первой и второй, соединен со стоком третьего транзистора п-типа, затвор которого соединен с затвором третьего транзистора р-типа данного логического элемента и выходом соответствующего инвертора данной ячейки памяти, исток первого транзистора р-типа логического элемента соединен с ниной питания регистра и с истоками соответствующих инверторон второй ячейки памяти, затворы второго и третьего транзисторов и-типа и второго и третьего тран зисторов р-типа логических элементов первой ячейки памяти и затворы третьих транзисторов и- и р-типов логических элементон, второй ячейки памяти соответственно соединены, отличающийся тем, что, с целью упрощения регистра, он содержит элемент ИЛИ-НЕ и группу иннерторов, а каждый логический элемент каждой ячейки памяти, кроме первой — пятый транзистор pl типа, исток и сток которого соединены

l соответственно с истоком и стоком второго транзистора р-типа, а затвор в -й ячейке памяти (i ) 2) соединен с затвором четвертого транзистора п-типа данного логического элемента и с истоком первого транзистора п-типа соответствующего логического элемента (i-2)-й ячейки памяти, исток третьего транзистора-n-. типа логических элементов каждой ячейки памяти, кроме первой, соединен со стоком перного транзистора и-типа данного логического элемента, стоки перного и четвертого транзисторов р-типа логического элемента соединены с истоком первого транзистора п-типа, а сток его четвертого транзистора и-типа во всех ячейках, кроме первой и послед- . ней, и сток второго транзистора и-типа логических элементов первой ячейки памяти соединены с выходами соответствующих инверторов последующей ячейки памяти, причем входы первого и второГо инверторов группы янляются соответственно прямым и инверсным

1494041 ми четвертых транзисторов и-типа первого и второго логического элементов второй ячейки памяти соответственно, вход третьего инвертора группы является управляющим входом считывашш регистра, а его выход соединен со стоками третьих транзисторов и-типа первого и второго логических элементов последней ячейки памяти, перрый и второй входы элемента Ш1И-11Г сое- .

15 информационными входами регистра, а их выходы соединены с затворами вторых транзисторов п-типа первого второго логических элементов первой

5 ячейки памяти соответственно и стокади Iены соответствеlIHо с выходами инверторов первой ячейки памяти, а его выход является управляющим выходом записи регистра, вторые входы пятого и четвертого инверторов соединены с выходами второго и первого инверторов последней ячейки памяти соответственно, а их выходы являются прямым и инверсным информационными выходами регистра соответственно, входы первого и второго инверторов группы соединены с эатвораьи пятых транзисторов р-типа первого и второгп логических элементов второй ячейки памяти регистра соответственно, 1 494041

1494041

f0

Составитель A.Äåðþãèí

Редактор М,Келемеш Техред Л.Сердюкова Корректор H.ÃoÐ e

Заказ 4))5/47 Тираж 558 Псдписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101