Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение равномерности шага сетки синтезируемых частот. Синтезатор содержит управляемый г-р 1, смеситель 2, умножитель 3 частоты, делители 4 и 5 частоты с переменным коэф. деления, импульсно-фазовый детектор 6 и фильтр 7 нижних частот, образующие кольцо фазовой автоподстройки частоты, а также D - триггер 8, мультиплексор 9 и датчики 10 и 11 кодов. Установка цифровых кодов делителя 4 и датчиков 10 и 11 обеспечивает в синтезаторе равномерную сетку частот при относительно большом количестве синтезируемых частот. Шаг сетки частот можно сделать небольшим с сохранением большой скорости перестройки синтезируемых частот. В выходном сигнале отсутствуют побочные составляющие, связанные с добротностью коэф. деления, т.к. последовательность выходных импульсов делителя 5 строго равномерна. Цель достигается введением делителя 4, D - триггера 8, мультиплексора 9 и датчиков 10 и 11. 1 ил.

СОЮЗ СОВЕТСКИХ

СО1.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 Н 03 Ь 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4335056/24-09 (22) 05.10.87 (46) 15.07.89. Бюл. 1- 26 (72) В.M. Волков, Б.А. Трапезников и А.И, Урьяс (53) 621.373.42(088.8) (5e) Авторское свидетельство СССР

Ф 1018258) кл. Н 03 L 7/16, 1980.

Авторское свидетельство СССР

Р 1058075, кл. Н 03 L 7/16, 1982. (54 ) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение равномерности шага сетки синтезируемых частот. Синтезатор содержит управляемый г-р 1, смеситель 2, умножитель 3 частоты, делители 4 и 5 частоты с переменным коэф. деления, импульсно-фазовый детектор 6 и

„„80„„1494215 А ) 2 фильтр 7 нижних частот, образующие кольцо фазовой автоподстройки частоты, а также D-триггер 8, мультиплексор 9 и датчики 10 и 11 кодов. Установка цифровых кодов делителя 4 и датчиков 10 и 11 обеспечивает в синтезаторе равномерную сетку частот при относительно большом количестве синтезируемых частот. lar сетки частот можно сделать небольшим с сохранением большой скорости перестройки синтезируемых частот. В выходном сигнале отсутствуют побочные составляющие, связанные с добротностью коэф. деления, т.к. последовательность выходных импульсов делителя 5 строго равномерна. Цель достигается введением делителя 4, D-триггера 8, мультиплексора 9 и датчиков 10 и 11.

1 нл.

14942

Изобретение относится к радиотехнике и может использоваться для генерации сетки частот в радиоприемных и радиопередающих устройствах.

Цель изобретения — повышение равномерности шага сетки синтезируемых частот.

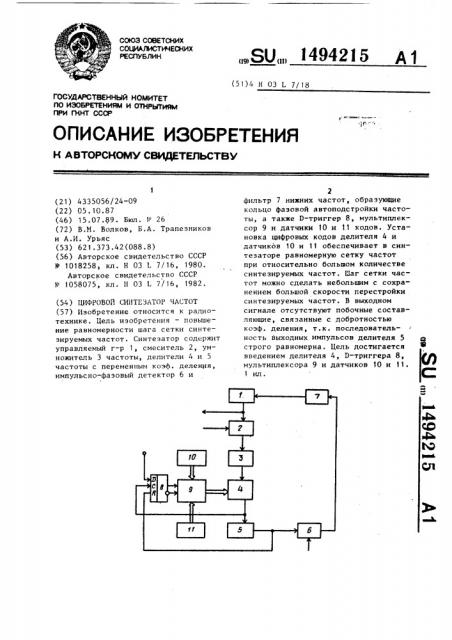

На чертеже представлен цифровой синтезатор частот. 1О

Цифровой синтезатор частот содержит управляемый генератор 1, смеситель 2, умножитель 3 частоты, второй

4 и первый 5 делители частоты с переменным коэффициентом деления 15 (ДПЩ), импульсно-фазовый детектор (ИФД) 6, фильтр 7 нижних частот (ФНЧ) 7, D-триггер 8, мультиплексор

9 и первый 10 и второй 11 датчики кодов. 20

Цифровой синтезатор частот работает следующим образом.

Сигнал с выхода первого ДПКД 5поступает на вход установки в "0"

D-триггера 8 и устанавливает его в нулевое состояние. Сигнал с прямого и инверсного выходов D-триггера 8 устанавливает мультиплексор 9 в положение, при котором на управляющий вход второго ДПКД 4 поступает цифровой код k с выхода первого датчика кодов 10. Через время, равное

Т пч.k — на вход первого ДПКД 5 и и

Тпч1с

+ п

Тдпкд = T nv(N 1) k-n

Т (N + ----) яч и

Поскольку

Т дпнд Э дпкд

1 а Тяч= ! ЬЫХ О1 получают

k-n еык = дпкд(1 +,,--) + где ы„ — выходная частота управляемого генератора 1, f о, — частота смещения.

Так как в установившемся режиме кольца фазовой автоподстройки час готы, образованном управляемым генератором 1, смесителем 2, умножителем

3 частоты, ДПКД 4 и 5, ИФД 6 и

ФНЧ 7, f д якд = f с (где, — опорная частота цифрового синтезатора частот), то

k-n ь п о (+ ) o

4 код на выходе первого датчика 10 кодов ; и — цифровой код на выходе второго датчика 11 кодов; N — цифровой код установки первого ДПКД 5).

Тогда период выходного сигнала первого ДПКД 5 тактовый вход D-триггера 8 с выхода 35 второго ДПКД 4 поступает импульс, который переводит 9-триггер 8 в единичное состояние, а сигнал с прямого и инверсного выходов D-триггера 8 переключает мультиплексор 9 в поло- 40 жение, при котором на управляющий вход второго ДПКД 4 поступает цифровой код и с выхода второго 11 датчика кодов, В этом случае на вход первого ДПК7 5 и тактовый вход 0-триг 45 гера 8 с выхода второго ДПКД 4 поступает периодический сигнал с периоТпч п дом -- †-- Таким образом в течение и одного периода выходной частоты первого ДПКД 5 на его вход поступает

N периодов входной частоты, один иэ

Тпч k которых значение ------, (N-1) пеп

Tp n

55 риодов имеют значение п (где Т „ч — период повторения сигнала на выходе смесителя 2, k — цифровой

Последовательность выходных импульсов первого ДПКД 5 строго равномерна, следовательно, побочные составляющие, связанные с дробностью коэффициента деления в выходном сигнале цифрового синтезатора частот отсутствуют.

Шаг сетки выходных частот равен

k-n (— -)

01 и

При необходимости получения выходной частоты, кратной опорной частоте f, код установки первого датчика 10 кодов k принимают равным п.

При этом выходная частота цифрового синтезатора частот f g,д=Г М+ о,.

Если необходимо получить выходную частоту, не кратную опорной частоте, код Е принимает значение, не кратные значениям кода и. При этом при k < n шаг сетки цифрового синтезатора частот принимает отрицатель ные значения, а при k > n положительные, при k = 0 выходная частота

14 bitt о 1 1)+f формула и з о б р е т е н и я

Цифровой синтезатор частот, содержащий последовательно соединенные первый делитель частоты с переменным коэффициентом деления, импульсно-фаСоставитель А.Мышакин

Техред Л. Олийнык

Редактор Л.Пчелинская

Корректор Т.Малец

Заказ 4 129/55 Тираж 884 .Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина,101

Количество синтезируемых частот при фиксированном значении И и значении 0 с k i п равно (n+1) .

Поскольку на вход умножителя частоты 3 поступает частота равная

Г nv =Г bier — f o< то умножитель частоты 3 может работать при достаточно больших и ограниченных только быстродействием второго ДПКД 4 и диапазоном перестройки выходных частот цифрового синтезатора частот.

Таким образом, цифровой синтезатор частот обеспечивает равномерную сетку частот, при относительно большом количестве синтезируемых частот.

Шаг сетки цифрового синтезатора частот можно сделать небольшим с сохранением большой скорости перестройки синтезируемых частот.

Кроме того, в выходном сигнале цифрового синтезатора частот отсутствуют побочные составляющие, связанные с добротностью коэффициента деления, поскольку последовательность выходных импульсов первого ДПКД 5 строго равномерна.

94215 6 зовый детектор, фильтр нижних частот, управляемый генератор и смесптель, а также умножитель частоты, о т л ич а ю шийся тем, ч",:>, с целью повышения равномерности шага сетки синтезируемых частот, введены мультиплексор, второй делитель частоты с переменным коэффициентом деления, D-триггер, а также первый и второй датчики кодов, причем прямой и инверсный выходы D-триггера подключены соответственно к первому и второму управляющим входам мультиплексора, 15 первый и второй датчики кода подключены соответственно к первому и второму сигнальным входам мультиплексора, выход которого соединен с управляющим входом второго делителя частоты с переменным коэффициентом деления, выход смесителя подключен к входу умножителя часто-.ы, выход которого соединен с входом второго делителя частоты с переменным коэффициентом деления, вход установки в "0

D-триггера соединен с выходом первого делителя частоты с переменным коэффициентом деления, выход второго делителя частоты с переменным коэффициентом деления соединен с входом первого делителя частоты с переменныи коэффициентом деления и тактовым входом D-триггера, D-вход которого является входом сигнала логической единицы, другой вход смесителя явля-; ется входом сигнала частоты смещения.