Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано при контроле динамических параметров высокоразрядных цифроаналоговых преобразователей (ЦАП). Цель изобретения - повышение точности измерения. В процессе измерения фиксируются моменты вхождений сигнала контролируемого ЦАП в две зоны. Интегрируют сигнал ЦАП в течение интервала между вхождениями в первую и вторую зоны. Затем интегрируют эталонный сигнал, пропорциональный разности граничных значений зон. Результат измерения формируют путем кодирования интервала от момента смены входных кодов ЦАП до момента равенства результатов интегрирования. Для осуществления способа в устройство дополнительно введены два ключа, источник эталонного напряжения с управляемой полярностью, интегратор, формирователь импульса и компаратор. 2 с.п.ф-лы, 2 ил.

СОЮЗ СОЕКТСНИХ

СОЦИФЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 Н 03 Г1 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЭОЬРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4332921/24-24 (22) 01.10.87 (46) 15.07.89. Бюл. М 26 (71) Гомельский политехнический институт (72) E.Ã. Абаринов и 1).А. Козусев (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф 1019628, кл. Н 03 К 13!32, 1982.

Авторское свидетельство СССР

И 12989 16, кл. Н 03 М 1/ 10, 1985, (54) СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕНИ УСТАНОВЛЕНИЯ ВЫХОДНОГО СИГНАЛА ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к измерительной технике и может быть использовано при контроле динамических па— раметров высокоразрядных цифроана„„Я0„„1494216 А 1

2 логовых преобразователей (ЦАП) . Цель изобретения — повышение точности измерения. В процессе измерения фиксируются моменты вхождений сигнала контролируемого ЦАП в две зоны. Ин.тегрируют сигнал ЦАП в течение интервала между вхождениями в первую и вторую зоны. Затем интегрируют эталонный сигнал, пропорциональный разности граничных значений зон. Результат измерения формируют путем кодирования интервала от момента смены входных кодов ЦАП до момента равенства результатов интегрирования. Для осуществления способа в устройство дополнительно введены два ключа, источник эталонного напряжения с управляемой полярностью, интегратор, формирователь импульса и компаратор, 2 с.п, ф-лы, 2 ил.

149421

Изобретение относится к электроизмерительной технике и может быть использовано в автоматизированных системах контроля времени установле5 ния цифроаналоговых преобразователей (ЦЛП).

Цель изобретения — повышение точности измерения времени установления выходного сигнала ЦАП.

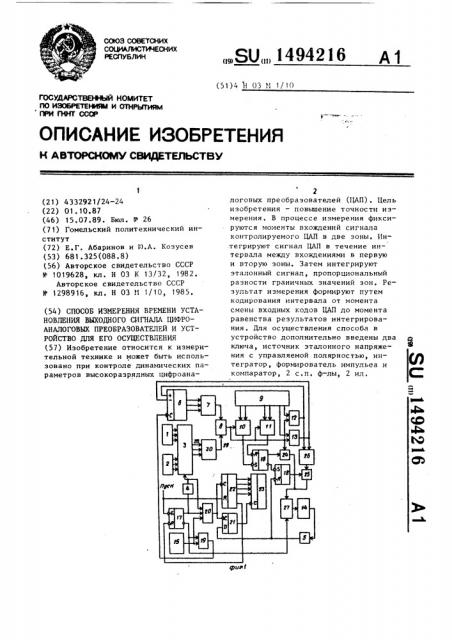

На фиг. 1 представлена функциональная схема устройства; на фиг. 2— временные диаграммы, поясняющие способ.

Устройство содержит задатчики

1 и 2 кодов, коммутатор 3, формирователи 4 и 5 импульсов, реверсивный счетчик 6, ЦАП 7, сумматор 8, формирователь 9 разнополярных пороговых уровней, двухпороговые компара- 20 торы 10 и 11, компараторы 12-14. генератор 15 импульсов, Rf-триггеры

16-18, элементы И 19 и 20, D-триггер

21, счетчики 22 и 23, ключи 24 и 25, источник 26 эталонного напряжения с управляемой полярностью, интегратор 27, выходную шину 28 и входную шину 29 для подключения контролируемого ЦАП 30.

Способ осушествляется следующим образом.

На экспоненциальном конечном участке переходной характеристики выходной сигнал ЦАП аппроксимируется функцией:

Т Тт-t

U(t)=U ехр(— --)=U ехр(†---)=

=0 5h exp(— -„— )

T t (1)

Э

Переходной процесс выходного сиг44 нала ЦАП содержит свободную составляющую и установившийся сигнал. Величиной V(t) обозначена свободная составл.ующая, равная разности сигнала ЦАП и его установившегося значе — 45 ния. Поэтому операция интегрирования разности сигнала ЦАП и его установившегося значения практически означает интегрирование свободной составляющей U(t), которая стремится к нулю U(t= )=О. Для упрощения реализации способа вынужденная составляющая переходного процесса входного сигнала ЦАП компенсируется путем вычитания из сигнала ЦАП предва- 55 рительно запомненного установившегося сигнала. Это позволяет формировать уровни +U и Ш 2 относительно нулевого уровня независимо от значеTf

Т

Т -Т

Т уст 1nU /О, 5h

= e lnU1/Ц (2) (3) (4) Результат интегрирования сигнала

ЦЛП на интерваое Т 2 -Т, Т2

U„„,= у $ u(t)at = о т2, 1 t Т2-t) ехр(- — -. е тт т

С T<-t ехр(— --) I

2 r„

+ - - П ехр(-- — „„— ) — exp О) tî г Т2-Т, -л - U 1 ех р (- — „-- ) — 1 ) . л

Из формулы (4) следует, что

Т вЂ” Т

1п U /U следовательно:

С т 2

11 т

U (-- — 1)

2 (5) нт о (U, U).

С

"о

Величина эталонного напряжения, интегрируемого в течение интервала

Времени T g q = T<> T 2 От МОМеНТВ

Т < до момента Т „, соответствующего равенству интегралов, определяется из соотношения уровней U „U z и 0„5h:

U 1-U1

U (6)

1п U2/0,5»

Результат интегрирования эталонного сигнала для t 7 Т2

11 ннт, рт ()

L ° тdt т2

t-T U i-U g

1п U/0,5h

В момент времени Т„ результаты интегрирования сигнала ЦА11 и U равны

Т Т, 0)тнт. от (Т иом) с

4 ний входных кодов ЦА11, а также усилить свободную составляющую V(t).

Таким образом сигнал ЦАП в данном случае — это его свободная составляющая U(t) с учетом того, что вынужденная составляющая скомпенсирована °

Величина Т, Т, Т„и U, U и 0>5» связаны соотношениями:

1494216 (7) Из формулы (7) б dt — — — — U (ехр(2

Тизм Т2 + 81nu2/0,5h

С учетом формулы (3)

Т иэм Т уст (8) 10

Погрешность времени установления, обусловленную влиянием 40, и d U2 на точность фиксации моментов Т и Т2 находят следующим образом.

Формируемый согласно предлагаемому способу код пропорционален интервалу времени длительностью Т„ + 4T, который равен сумме интервала

Т2+ 4С2 и интервала интегрирования

Т эт — Тцэм+ 4Т- 4 t2.

С учетом погрешностей 4 t1 и

4 2 формулы (2) в (3) и (4) принимают вид:

Т+ 4t = Т ст -б1п - — — (9) 25

U+dU„

0,5h л

Ц1+4Ц 2

+ дт = T -б1п -=- ° (10)

0 5h

Up+du

Т T + 4 t — дс — б 1n — — - -(11)

Если из формулы (9) вычесть формулу (2), из (10)-(3) и из (11) — (4), получают (12) = б Ц Ц2+(4Ц +4Ц21 1п

Ц, -Ц2 (13) Ц2

0,5h (14) 40 (14), Результат измерения с учетом по(15) грешностей 4 t, и d t2.

4t U,+ dU„ ехр (- — -)

U, «4С 2 U«+nu1 ехр (- — — ) Л ц

1 (16) u2+ 4 ц2

Уст 0 5h

=T — б lп — — + (1+

4t2-4t, U2+dU2 ехр (- — — „— — ) е (17) б Ц +4Ц

Результат интегрирования сигнала ЦАП

4Ц2 U2

55 U 0 5h

Э

+ (1+

u(t)dt

HНт йнт ц +лц

Т,41, т1.М2 ь Т„»4, 4ui i-bu 2

+ — — — — ) Ц1 Ц2 ц 2

ln ——

0,5h

Т1-t ехр(— — ) dt б

Т „. — б 1п(1+

U -U б .— — - - — — = --- (Ц -U )

1П ц2/0,5h 1 1 2 ца д t пб1п

U +4Ц, U2

bt2 = б1п —; ——

Ц2МЦ2

U +Щ п t1И ="1n.U +4цэ

Преобразовав формулы (12) получают

Т1а4< 2

Т«1-t

- — u ехр (—;,— )!

0 1T,+4С, Т2-Т -dt» г iТь-Ti

-exp(- — — — -7 = — — — U (ехр(- )n„

dt1 dt — ехр (- †-) exp ()

Используя полученное из (4) раТ2-T i Us венство ехр(- — — ) = -- а такие п ц °

2 формулы (15) и (16), получают

1 Ц2+4Ц2

U +bU — — U б нт инт; 2! ц — — = 1т (U,+nu,-ц -du2 J.(18)

Ua Ц <ОТ б

Время интегрирования эталонного сигнала Т найдем из условия равенства интЕгРалов Цннт+4Ц ннт=Цннт. эт:

Т1 1462 Тэт

1 1

u

l Тэт — — u + bu -ц — du,21 лб Эт

Ц тэ

ЬЬ

U +du -U2-4ц2

Т

m э.т цэт б (1+ — — --) ln U /0,5h.

dU1+d ц1

U 1J2

2 э °

Тнэм+ 4Т = Т2 + dt2 + Т эт

+ )ln T ьт б lп(1+

4u<-4U2 U 2

U1-U2 0,5h

1494216

dVt d Ь Л0. U2

+ — — ) .р 1п

Б„-Ц2 0,5Ь

Погрешность измерения

dUz дТ = — с 1n(1 + — --) +

112

n d Ut dUq. U1

+ 1п ——

U,-U2 0,5h (19) 10

Таким образом, максимальное значение погрешности (в случае Ь U

= -ЛП =dV):

15 дт = — с 1п(1- — — ) + и

dU

Мс кЕ Ц2

2611 П2

+л„— — — - 1n

U, -11 0,5h (20) Устройство работает следующим образом.

В исходном состоянии триггеры 25

16-18 находятся в нулевом состоянии, единичным сигналом с инверсного выхода триггера 17 интегратор 27 обнулен. Под действием потенциала

"1" с выхода формирователя 4 через коммутатор 3 к входам ЦАП 30 подключен код И2 задатчика 2.

На вход сумматора 8 поступает установившийся сигнал ЦАП 30. Через элемент И 19 импульсы генератора 15 поступают на счетный вход счетчика

6, выходной код; которого является управляющим для ЦАП 7. Выходной сигнал ЦАП 7 является компенсирующим по отношению к установившемуся сигналу ЦАП 30. Суммарный сигнал ЦАП 7 и 30 с выхода блока 8 поступает на входы кочпараторов 12 и 13 ° Один из них сравнивает сигнал сумматора с уровнем - Б, а другой — с уровнем

-Uo. В зависимости от положения сум45 марного сигнала относительно уровней

Ю компараторы 12 и 13 вырабатывают сигналы управления счетчиком 6, код в котором изменяется, вызывая уменьшение и увеличение компенсирующего 50 сигнала ЦАП 7. При попадании сигнала сумматора в зону +U оба компаратора

12 и 13 принимают нулевое состояние, счетчик. 6 и ЦАП 7 переходят в режим хранения компенсирующего сигнала. 55

При поступлении импульса запуска счетчик 22 обнуляется, а триггер 17 устанавливается в единичное состояние, запуская формирователь 4 импульсов. Элемент И 19 при этом закрывается. На время действия импульса формирователя 4 элемент И 20 блокируется, а через коммутатор 3 к входам ЦАП 30 подключается код N

1 задатчика 1. В момент окончания импульса формирователя 4 элемент И 20 открывается, а на входах ЦАП 30 происходит смена кодов N - N . В этот момент времени, соответствующий началу контролируемого переходного процесса ЦАП 30, в счетчик ?2 через элемент И 20 начинают поступать счетные импульсы генератора 15.

Из выходного сигнала ЦАП 30 вычитается установившийся сигнал, поэтому на выходе сумматора 8 выделяется свободная составляющая переходного процесса. Фо рмирователь уровней 9 задает пороги срабатывания

fV> для двухпороговог0 компаратора

10 и уровни +U для двухпорогового компаратора 11. При попадании сигнала сумматора 8 в зону >U триггер 16 сигналом компаратора 10 переключается в единичное состояние и обнуляется сигналом компаратора 11 при попадании сигнала сумматора 8 в зону

+U2 (фиг. 2г). На время прохождения сигнала контролируемого ЦАП между уровнями U и U2 (или -11 и

-U2) сигиалом "1" триггера 16 открывается ключ 24, контролируемый сигнал поступает на вход интегратора

27. Предлагаемое устройство характе4 ризуется использованием одного интегратора для интегрирования как сигнала ЦАП, так и эталонного сигнала источника 26, причем полярность U противоположна полярности сигнала

ЦАП. Поэтому момент равенства результатов интегрирования сигнала ЦАП и U, соответствует моменту равенства нулю напряжения Б „ (фиг. 2е).

По сравнению с использованием двух интеграторов такое техническое решение позволяет исключить влияние разброса и дрейфа постоянной времени интегратора. Как видно из приведенных формул постоянная интегрирования,не входит в результат преобразования. При вхождении сигнала ЦАП в зону +V 2 триггер 18 переключается в единичное состояние сигналом с инверсного выхода триггера 16, ключ

25 открывается, к входу интегратора

27 подключается эталонное напояжеэталонного цифроаналогового преобразователя эталонное напряжение, пропорциональное величине входного кода поверяемого цифроаналогого преобразователя, одновременно формируют два пороговых уровня положительного напряжения, расположенных в диапазоне выходного сигнала поверяемого цифроаналогового пресбразавателя, и два пороговых уровня о рицательного напряжения, равных по модулю соответствующим пороговым уровням положительного напряжения, после чего формируют входной сигнал путем подачи входного кода на поверяемый цифроаналоговый преобразователь и с момента подачи входного кода осуществляют непрерывно формирование разностного сигнала, равного текущему отклонению входного сигнала от эталонного напряжения, одновременно начиная с момента подачи входного кода формируют код текущего временного интервала, в течение которого непрерывно осуществляют сравнение разностного сигнала с соответствующими пороговыми-уровнями и формирование соответствующих информационных временных интервалов, каждый из которых равен времени между двумя последовательными моментами равенства разностного сигнала и соответствующим пороговым уровнем положительного или отрицательного напряжения, и осуществляют определение времени уста.новления выходного сигнала поверяемого цифроаналогового преобразователя, отличающийся тем, что, с целью повышения точности, в течение каждого информационного временного интервала интегрируют разностный сигнал и запоминают последний результат интегрирования, после чего формируют вспомогательный сигнал, пропорциональный разности двух пороговых уровней соответствующего напряжения, и интегрируют вспомогательный сигнал, момент равенства которого запомненному результату интегрирования является моментом окончания формирования текущего временного интервала, а опре25

1494216 10 ние U>Ä источника 26. Полярность автоматически устанавливается противоположной полярности свободной составляющей V(t) сигнала ЦАП 30 на интервале Т, (t < T . Для управления

5 полярностью U источника 26 используются сигналы компараторов 12 и 13, с помощью которых замыкается один из двух ключей, содержащихся в источнике 26, и к выходу источника 26 подключается напряжение U » О при

U(t) < О, либо -U я7 при U(t) > О. Момент Тр находится из условия инт(Тимм) = О (фиг. 2е) и выделяется 15 с помощью компаратора 14, изменяющего свое состояние при пересечении напряжения U „„, нулевого уровня.

Поскольку в зависимости от знака

Б напряжение интегратора может под- 20 ходить к нулевому уровню как сверху, так и снизу, комнаратор 14 может в этот момент переключаться как из состояния "1" в состояние "О", так и наоборот. Поэтому формирователь

5 импульсов должен запускаться как фронтом, так и срезом импульсов компаратора 14. Для этого он может содержать, например, формирователь импую ьсов по фронту, формирователь импульсов по срезу, выходы которых объединены с помощью элемента ИЛИ.

Длительность импульса формирователя

5 должна быть больше периода следования импульсов генератора 15 для надежного переключения D-триггера

21 в единичное состояние. Код счетчика 22, соответствующий моменту времени Т, записывается в счетчик с помощью импульса записи D-триггера 21. Такт измерения заканчивается после заполнения счетчика 22, импульс переполнения которого обнуляет триггер 17, устройство переводится в режим компенсации выходного сигнала ЦАП 30 с помощью ЦА11 7. Код, 45 пропорциональный измеряемому времени установления, может быть считан из счетчика 23 в блок индикации (не показан). При других кодовых комбинациях задатчиков 1 и 2 кодов устройство работает аналогично °

Формулаизобретения

1. Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей, заключающийся в том, что формируют с помощью деление времени установления выходного сигнала поверяемого цифроаналогового преобразователя осуществляют по коду сформированного текущего временного интервала.

2. Устройство для измерения времени установления выходного сигнала

149421 цифроаналоговых преобразователей, содержащее формирователь разнополярных пороговых уровней, первый, второй, третий, четвертый, пятый и шес5 той выходы которого соединены соответственно с первым и вторым входами первого двухпорогового компаратора, первыми входами первого и второго компараторов, выход первого двухпорогового компаратора соединен с

S-входом первого RS-триггера, выход второго двухпорогового компаратора соединен с R-входом первого RS-триггера, вторые входы первого и второго компараторов объединены с третьими входами первого и второго двухпороговых компараторов и подключены к выходу сумматора, а выходы первого и второго компараторов соединены с первым и вторым входами управления реверсирования счетчика импульсов, счетный вход которого соединен с выходом первого элемента И, а выходы соединены с соответствующими входами цифроаналогового преобразователя, выход которого соединен с первым входом сумматора, второй вход которого является входной шиной, два задатчика кодов, выходы которых соединены соответственно с информационными входами коммутатора, выходы которого являются выходкой шиной устройства, установочный вход первого счетчика импульсов объединен с

S-входом второго RS-триггера и является шиной "Пуск", R-вход второго

RS-триггера подключен к выходу переполнения первого счетчика импульсов, инверсный выход соединен с первым входом первого элемента И, а прямой выход — с первым входом втоi рого элемента И и входом формирователя импульсов, выход которого сое6

12 динен с управляющим входом коммутатора и вторым входом второго элемента Й, выход второго элемента И соединен с С-входом D-триггера и счетным входом первого счетчика импульсов, выходы которого соединены соответственно с информационными входами второго счетчика импульсов, синхронизирующий вход которого соединен с выходом D-триггера, генератор импульсов, выход которого соединен с третьим входом второго элемента И и вторым входоы первого элемента И, третий RS-триггер, о т л и ч а ющ е е с я тем, что, с целью повышения точности, в него введены второй формирователь импульсов, третий компаратор, интегратор, источник эта-! лонного напряжения с управляемой полярностью и два ключа, управляющий и информационный входы первого ключа соединены соответственно с прямым выходом первого КЯ-триггера и выходом сумматора, управляющий и информационный входы второго ключа соединены соответственно с выходом третьего

RS-триггера и выходом источника эталонного напряжения с управляемой полярностью, управляющие входы которого соединены с выходами первого и второго компараторов выходы ключей соединены с информационным входом интегратора, управляющий вход которого соединен с инверсным выходом второго RS-триггера, а выход интегратора через последовательно соединенные третий компаратор и второй формирователь импульсов соединен с

D-входом D-триггера.и R-входом третьего КЯ-триггера, S-вход которого соединен с инверсным выходом первого RS-триггера.

1494216

Тизи

Составитель В. Смирнов

Техред Л. Олийнык

Редактор Л.Пчолинская

Корректор Т.Малец

Заказ 4 129/55

Тираж 884

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101