Измеритель краевых искажений

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение точности измерения. Измеритель краевых искажений содержит блок 1 согласования, задающий г-р 2, блок 3 формирования значащих моментов, блок 4 счета, блоки 5 и 6 памяти, блоки 7 и 8 сравнения, эл-т НЕ 9, блок 10 установки режимов, дешифратор 11, эл-ты ИЛИ 12 и 13, триггер 14 и эл-ты И 15,16 и 17. Цель достигается путем осуществления раздельной фиксации краевых искажений разных знаков. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) 0I) (У 4 И 04 1. 11/08

/ rr с I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ fKHT СССР

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ. (21) 4339013/24-09 (22) 09.12.87 (46) 15 ° 07 ° 89 Бюл. М 26 (71) Московский институт инженеров гражданской авиации (72) С.Ж.Кишенский, А.Я.Крекер, Г.М.Иванов и В.А.Решетников (53) 621.391.832.44 (088.8) (56) Авторское свидетельство СССР

М 10406 15А, кл . Н 04 L 11/08, 1979.

2 (54) ИЗМЕРИТЕЛЬ КРАЕВЫХ ИСКАЖЕНИЙ (57) Изобретение относится к электросвязи. Цель изобретения — повышение точности измерения. Измеритель краевых искажений содержит блок 1 согласования, задающий г-р 2, блок 3 формирования значащих моментов, блок 4 счета, блоки 5 и 6 памяти, блоки

7 и 8 сравнения, эл-т НЕ 9, блок 10 установки режимов, дешифратор 11, эл-ты ИЛИ 12 и 13, триггер 14 и эл-ты

И 15, 16 и 17. Цель постигается путем осуществления раздельной фиксации краевых искажений разных знаков.

1 ил.

1494239

l! 3< бр< l еш<е 3т1. iclilся к 3лектр«ня lit и может быть llc llo3IE, 3_#_I33fio для измерения крдевых искджешгй Et телеграфных ядндлдх е г3язи.

1!ель и 3<3брете ffft — повышение точности и 331ерения путем рд.<дельной фиксдц3ги краевых искажеш<и разных зндков.

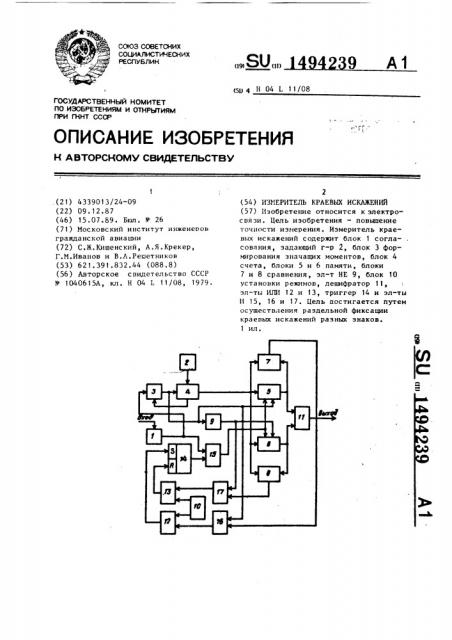

Пд чертеже представлена элект- 10 рическ,3я функционд.<ьндя схема устDolicтв,3 ..

Измеритель краевых искажений содержит блок 1 согласования, задающий roitopa Top 2, блок 3 форм31рова- 15 ния значащих моментов, блок 4 счета, первый и вт< рой блоки 5 и 6 памяти, первый и вт< оой б:1аки 7 и H сравнения, эле»ент !!Е 9, бл«к О установки рехд1к1<3в, дешифрдт<.р 11, первый и второй 20

Зле»енты !1:Д! 2 и 13, тг3иггер 14, «vpE3EiII — третий <3лел1енты И 15 — 17.

Ус тр< исти« работа ет слелуюшим образом.

Рехд<м р<3б<3ты устройства задает 25 блок 10. При измерении и регистрации

13с ех 3 паевых ис кджеш<й на установочные нх "ды тригr

Тдк, нд.lpltrfop, д.<я RS-триггера 14 с

IIPH ff,i fit УпРав I:3I<3I fltrfff входами и поЯмым выходo 1 неос .хо;п»о подать постоянный единичный сигнал на S-вход и

Il

При этом с 1г1<длы, поступающие на вторые входы элементов ИП!! 12 и 13 с зле -f«IITOD 1 16 и 17, не оказывают

40 в-ьиянил нд работу т<3иггера.

С IIpff;ohio» первого после начала сеанса входного сигнала из канала связи блок 1 col;ÄIcoftaitltff запускает блок 3, выполи< н3,III например, в виде 45 триггера, устанавливая его в определенное состояние (»alIp«f fep, единичное) . Ьлок 3 управляет работой блока 4 счета. представляюшего собой

Реверсиный счетчик, т. е. определяет 50 направле1гие счета — сложение или вычитание тактовых импульсов, посту\ павших с задающего генератора 2.

Первоначально блок 4 счета работает на сложение, Отсчитав число тактовых импульсов, соответсгв лощих 50Х длительности элементарной кодовой посылки сигнала, блок 4 счета выдает сигнал переноса, которьп1, поступая нд б. lot< 3, Il<. ðåêëfк 4 счета пег3еключдет блок 3, а в=ледствие этого и свой режим, и пав

I ч.1нает снова работать на сложение, и т.д. Таким образом создается "сетка" э гдлош<ых временных отсчетов внутри дчительности каждой элементарной код эвой посылки входного сигнала.

С приходом ках<лого действительного

<Значащего момента сигнала (иногда он называется действительным характеристическим моментом восстановления) бпок 1 согласования выдает импульс, к<3торьпf через открытый первый элемент

И 15 поступает нд первые управляющие входы первого и второго блоков 5 и 6 памяти, на вт орые управляющие входы которых поступают соответственно гигiiaaff с блока 3 и элемента !!Е 9, спуждцего инвертором, т.е. н любой моме33т времени возможна запись информации только в один из блоков

5 и 6 памяти. В блок S памяти зались возможна только в ин.гервдле. соответствуюцем единичному сосToêнию блока 3 (реха<му сложения блока счеты), т.е. в блоке 5 памя.ги фиксируются положительные значения краевых искажений или, иначе, запаздыв

В соответствующий блок 5 или 6 памяти записывается состояние блока 4 счета.

Информация из блоков памяти дешифрируется дешифратором 11 и выдается

t получателю в требуемом виде.

При измерении максимальных значений краевых искажений триггер 14 управляется по сигналам с элементов

И 16 и 17. Ппи этом блок !O»станавливается в такое состояние, чтобы не оказывать влияние на работу уст1-ойства (в данном случае с его вьжо149 дов долж»»».! поступать иа входы элементов ИЛ»! 12 и 13 нулевые поте;»циалы) .

Расс».»стрим более попробно»>аботу схемы в этом режиме.

Исхолиое состояние узлов устройства: в блоках 5 и 6 памяти записаны нулевые значения искажений, триггер

14 находится в единичном состоянии, блок 3 — то>хе, блок 4 счета начинает работать на сложение от первого с начала иэмере»»ия ДЗМВ °

Предположим, иа начальном участке сеанса ДЗМВ совпадает (в пределах раз. решающей способности измерителя) с эталонным ЭВМ (ЭЗМВ). К моменту поступления этого ДЗМВ блок 3 находится в нулевом состоянии. Блок 4 счета досчитывает до нудя и, поскольку содержимое блока 6 памяти нулевое, срабатывает второй блок 8 сравнения и через третий элемент И 17 и второй элемент ИЛИ 13 устанавливает триггер 14 в нулевое состояние. Одновременно при достижении нуля блоком

4 счета переключается блок 3 и выдает

HMIIvJIbc на чпрэвляющий вход первого блока 5 памяти. С первого блока 7 сравнения также поступает импульс на вход триггера 14 через второй элемент .И 16 и первый элемент ИЛИ 12. Этот импульс устанавливает триггер 14 в единичное состояние. Импульсы первого и второго элементов ИЛИ 12 и 13 поступают либо одновременно, либо импульс с второго элемента ИЛИ 13 запаздывает на пренебрежимо малое время, определяемое распространением сигнала по цепи блоков 3 и 5. В первом случае (при одновременном поступлении сигналов по установочным входам триггера 14) он не соабатывает вообще, во втором слччае время

его нахождения в нулевом состоянии значительно меньше разрешающей способности устройства и не вызывает нарушения его работы.

Предположим, следующий ДЭВМ "отстает" во времени от соответствующего ЭЗВМ. В момент его прихода блок 3 находится в единичном состоянии, блок 4 счета работает на сложение, следовательно, информация с него записывается в пег>вый блок 5 гамяти. фиксирующий положительные краевые искажения (в данном случае зафиксировано + 5 1)..В этом интервале времени соответствующем длительности между 1 239 г: сос» »»!»!r»II ЭЗВМ, пег>вый». 1.

I»e»»»»>» срабатывает дв»1;»".ы. в .. ги»;-т ! равенства нулю сост»»1»ил I"., к,l счета (пока в блоке 5 памяти 31ïèñ i—

НО НУЛЕВОЕ ЗнаЧЕИИЕ) 1 и г»о:!»Т -„РИхода ДЗМВ (oi»c записывается» пл»:-, памяти 5 и автоматически тут же nepB1,1I» блок 7 сравнения 110 совпадению значений блока 4 счета и блока 5 выдает сигнал). Однако этот сигнал не изменяет состояния триггера 14, так как он предназначен для установки его в единичное состояние, а триггер

14 уже находится в нем. Л»»алогичнь»е рассуждения имеют место и при следуюцих ДЗМВ, краевые искажения котооых больше по абсолютной величине и одинаковы по знаку с + 5 1. Если же

2р в дальнейыем краевые искажения данного знака меньше + 1 или отсчтствуют. то, хотя с выхода пеового блока 7 спавне»»ия снимаются два импульса, симметрично расположенные относитель25 но 33МВ (вследствие совпадения значения, записанного в первом блоке 5 памяти. и значения блока 4 счета при счете обратном (вычитание) и прямом (сложеиие) направлениях, на триггер

Зп 14 через второй элемент И !6 поступает только импульс, совпадаю»»в»1» с режимом сложения блока 4 счета, что опоеделяется раэрешаюш>»м сигналом с блока 3 «а второй вход второго элемента И 16. Кроме того, если в даль35 нейшем искажений данного знака меньше зафиксированных в пегвом блоке 5, то в момент их поступле»»>»я триггер 14 находится в нулевом состоянии и за4р прецает их запись в Iiep».b!Ii блок 5 памяти.

Фиксация отрицательных максимальных краевых искажений осуществляется аналогично. Единственное отличие

45 состоит в том что пои появлении но1 вого максимального значения отрицательного краевого искажения нет двойного срабатывания второго блока

8 сравнения, так как при режиме вычи50 тания блокэ 4 счета он сначала достигает нового значения краевого искажения (отрицательного), а потом нулевого (или меньшего по абсолютной величине), при достижении которого

55 соавнение не осуществляется, так как во втовом блоке 6 пагляти уже записано новое, большее по абсолютной величине, значение краевого искаже.ния.

1494239

Составитель Камалягин

Техред Л.Олийнык Корректор Т.Колб

Редактор М .Петрова

Заказ 4 132/57, Тираж 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, 3-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

Таким образом, тоиггер 14„создает запоещенную зону для записи новых значений краевых искажений (как в отрицательную зону относительно ЭЗМВ, так и в положительнчю), если они меньше по абсолютной величине ранее

1эаписанных значений соответствующих знаков.

Формчла изобретения Ъ

Измеритель краевых искажений, содержащий блок установки режимов, задающий генеоатор, первый блок сравне- 15 ни !, последовательно соединенные триггер и первый элемент И и последовательно соединенные блок согласования, блок формирования значащих моментов, блок счета, первый блок па- 20 мяти и дешифратор, выход котооого является выходом устройства, входом которого является вход блока согласования, выход которого подключен к

° другому входу пеового элемента И, 25 выход кЬтооого подключен к второму входу второго блока соавнения, выход задающего генератооа подключен к другому входу блока счета, другой выход которого подключен к другому 30 входу блока формирования значащих моментов, выход блока счета подключен к первому входу первого блока соавнения, втооой BxoII которого с оединен с выходом первого блока памяти, отличающийся тем, что, с иелью повышения точности измерения путем раздельной фиксац.!и краевых искажений разных знаков, введены последовательно соединенные второй элемент И и первый элемент ИЛИ, выход которого подключен к первому входу триггера, и последовательно соединенные элемент НЕ, втооой блок памяти, второй блок сравнения, третий элемент И и второй элемент ИЛИ, выход которого подключен к второму входу триггера, первьпi и BTQDQH Bb! ходы блока чстановки оежимов подключены к другим входам соответственно первого и второго элементов ИЛИ, выход блока формирования вначащих моментов подключен к третьему входч блока памяти, к первому входу второго элемента И и к входу элемента НЕ, выход которого подключен к другому входу третьего элемента И, выход блока счета подключен к другомч входу второго блока сравнения и к второму входу второго блока памяти, третий вход которого соединен с выходом первого элемента И, а выход подключен к доугому входу дешифратора, выход первого блока сравнения подключен к втооому входу второго элемента И.