Устройство для контроля дешифратора

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении запоминающих устройств и многоканальных устройств коммутации. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит элемент И 1, элемент НЕ 2, узел 3 сравнения, триггер 4, второй элемент задержки 5, счетчик 6, первый элемент задержки 7, блок 8 свертки по модулю два, элемент ИЛИ 9, регистр 10 адреса, группу 11 элементов И. На информационный вход контролируемого дешифратора 12 поступает код с регистра 10 адреса. Через элемент ИЛИ 9 происходит опрос контролируемого дешифратора 12, выходы которого соединены с входами блока 8 свертки по модулю два и первыми входами соответствующих элементов И группы 11. Если появляется сигнал на выходе нечетности блока 8, то разрешается прохождение сигналов с выходов дешифратора 12 через элементы И группы 11 на выход устройства и сбрасывается в нулевое состояние триггер 4 (он был установлен в единичное состояние одновременно с опросом дешифратора 12). Если появляется сигнал на выходе четности блока 8, то прибавляется единица к счетчику 6 и происходит повторный опрос дешифратора 12 через второй элемент задержки 5, элемент И 1 и элемент ИЛИ 9. Так продолжится до появления сигнала на выходе четности блока 8 или появления сигнала на выходе узла 3 сравнения, который с помощью элемента НЕ 2 блокирует элемент И 1. 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК .

А1

„„80„„14 5801 (51)4 G 06 F 11/16

ВЖОЯ

ПАТЕНТНЗ it.

j к ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

H ASTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21) 4351420/24-24 (22) 23.11.87 (46) 23,07.89. Бюл. N - 27 (72) Л.О.Беспалов (53) 681. 2 (088. 8) (56 ) Авторское свидетел ьст во СССР

N - 1179343, кл. G 06 F 11/00, 1984.

Авторское свидетельство СССР

Р 1252783, кл. G 06 F 11/16, 1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕНИФРАТОРА (57) Изобретение относится к области автоматики и вычислительной технике и может быть использовано при построении запоминающих устройств и много— канальных устройств коммутации. Цель изобретения — повышение достоверности контроля устройства. Устройство содержит элемент И 1, элемент НЕ 2, узел 3 сравнения, триггер 4, второй элемент задержки.5, счетчик 6, первый элемент задержки 7, блок 8 свертки по модулю два, элемент ИЛИ 9, регистр 10 адреса, группу 11 элементов И. На информационный вход контролируемого дешиф2 ратора 12 поступает код с регистра 10. адреса. Через элемент ИЛИ 9 происходит опрос контролируемого дешифратора 12, выходы которого соединены с входами блока 8 свертки по модулю два и первыми входами соответствующих элементов И группы 11. Если появляется сигнал на выходе нечетности блока 8, то разрешается прохождение сигналов с выходов дешифратора 12 через элементы И группы 11 на выход устройства и сбрасывается в нулевое состояние триггер 4 (он был установлен в единичное состояние одновременно с опросом дешифратора )2). Если появляется сигнал на выходе четности блока 8, то а прибавляется единица к счетчику 6 и происходит повторный опрос дешифратора 12 через второй элемент задержки 5, элемент И 1 и элемент ИЛИ 9. Так про- С должается до появления сигнала на выходе четности блока 8 или появления сигнала на выходе узла 3 сравнения, который с помощью элемента НЕ 2 бло- Д, кирует элемент И 1. 2 ил. й

3 1495801

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении запоминающих устройств и многоканальных уст5 ройств коммутации.

Целью изобретения является повышение достоверности контроля устройства.

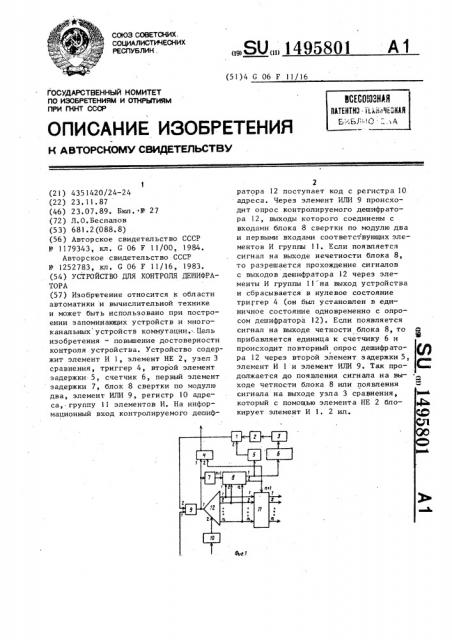

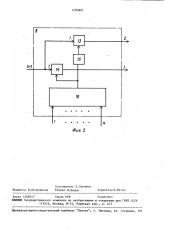

На фиг. 1 приведена функциональная схема устройства; н.а фиг. 2 - функциональная схема одного из вариантов блока свертки по модулю два.

Устройство для контроля дешифратора (фиг. 1) содержит элемент И 1, элемент НЕ 2, узел 3 сравнения, триг- 15 гер 4, второй элемент 5 задержки, счетчик 6, первый элемент 7 задержки, блок 8 свертки по модулю два, элемент ИЛИ 9, регистр 10 адреса, группу 11 элементов И. Кроме того, на 20 фиг. l изображен контролируемый деШифратор 12, который не входит в состав устройства.

Блок 8 свертки по модулю два (фиг. 2),, содержит элементы И 13 25

1» 14, элемент НЕ 15 и узел 16 свертки по модулю два.

Устройство для контроля дешифратора работает следующим образом.

Код, подлежащий,цешифрации, посту- 30 пает на информационный вход регистра

10 адреса и с его .выхода - на инфорМационный вход контролируемого дешифратора 12. Затем на тактовый вход устройства поступает импульс, который 35

»»роходит через элемент ИЛИ 9 на перВый вход контролируемого дешифратора 12. Кроме того, эн поступает на вход первого элемента 7 задержки и на единичный вход триггера 4, в ре- 411 зультате чего последний устанавливается в положение, соответствующее неисправности. Наличие тактового сигна"»а опроса и кода на входе контролируемого цешифратора 12 в случае исправ- 45 ной работы устройства приводит к появленвю на одном из его выходов сигнала дешифрации ..(декодирования

><ода адреса). При неисправной работе устройства, вызванной отказом его элементов.ипи возникновением помех, являющихся следствием воздействия на устройство внешних »»агнитнь»х, или электрических палей, или иных воздейСтв»»Й на ВыхОдах кОнтролируемОгО де 55

Шифратора 12 может появиться .более одного сигнала. Поэтому для классификации исправной или неисправной рабобы дешифратора 12 код с его выхода, наряду с поступлением его на входы элементов И группы 11, подается и на входы блока 8 свертки по модулю два.

В блоке 8 «осуществляется проверка кода на соответствие или несоответствие- наличия в нем одной единицы. В первом случае (или при наличии в анализируемом коде одной единицы) выхода нечетности блока 8 снимается сигнал, которьп» осуществляет "подсветку" элементов И группы 11 (стробирование), в результате чего код с выхода дешифратора 12 поступает на выход устройства. Одновременно этот же сигнал возвращает триггер 4 в исходное состояние или состояние исправности устройства. Триггер 4 устанавливается в единичное и нулевое состояния по поло>кительному перепаду сигналов на его соответствующих входах. Элемент

7 задержки задерживает сигнал опроса на время срабатывания контролируемого дешифратора 12 и блока 8.

При неисправной работе устройства, определяемой блоком 8 как наличие на выходах дешифратора 12 четного количества единиц, соответствующий сигнал появляется на выходе четности блока 8.

С помощью этого сигнала и узлов 1, 2, 3, 5 и 6 организуется повторньп» опрос контролируемого дешифратора 12 и повторный анализ блоком 8 кода на выходе дешифратора 12.

Если в результате выработки внутренними узлами устройства повторного сигнала опроса и повторной дешифрации адреса, хранящегося в регистре 10 адреса, блоком 8 устанавливается факт исправной работы, то соответствующий сигнал появляется на выходе нечетности блока 8. Он осуществляет стробирование элементов И группы 11 (для выдачи кода на выход устройства) и сброс триггера 4 в исходное состояние. (При этом предполагается, что изменение адреса в регистре 10 осуществляется с учетом возмо>хности выработки повторных обращений к дешифратору, например, не более двух, трех, или с учетом анализа состояния триггера 4).

Если при повторном опросе контролируемого дешифратора 12 снова поя— вится сигнал на выходе четности блока 8 свертки по модулю два и через второй элемент 5 задержки, элемент И

1 и эпемент ИЛИ 9 произойдет очередной опрос контролируемого дешифрато149580 ра 12. Одновременно происходит прибавление единицы к счетчику 6.

При неправильной работе контролируемого дешифратора его опрос продол5 жается до тех пор, пока не сработает узел 3, настроенный на код максимального числа повторных опросов. После этого единичный сигнал с выхода узла 3 через элемент НЕ 2 закрывает элемент И 1 для прохождения импульса с выхода второго элемента 5 задержки.

Величина этой линии задержки должна обеспечить задержку сигнала с выхода четности блока 8 свертки по модулю 15 два на время большее времени срабатывания счетчика 6, узла 3 сравнения и элемента НЕ 2, Устройство позволяет отличить неисправность дешифратора от искажения 20 сигналов на его выходах под воздействием помех.

Формул а изобретения

Устройство для контроля дешифрато- 25 ра, содержащее регистр адреса, первый элемент задержки, элемент И, элемент

ИЛИ, триггер, группу элементов И, причем информационный вход регистра адреса является информационным вхо- 30 дом устройства, выход триггера является выходом исправности устройства, выход регистра адреса является выходом устройства для подключения к информационнбму входу контролируемого дешифратора, о т л и ч а ю щ е е с я тем, что, с целью повышения достовер1 6 ности контроля устройства, в него введены второй элемент задержки, счет— чик, элемент НЕ, блок свертки по модулю два и узел сравнения, причем первый вход элемента ИЛИ является тактовым входом устройства, выход элемента ИЛИ соединен с единичным входом триггера и входом первого элемента задержки и является выходом устройства для подключения к тактовому входу контролируемого дешифратора, выход первого элемента задержки соединен с тактовым входом блока свертки по модулю два, выход четности которого соединен с входом второго элемента задержки и счетным входом счетчика, выход которого соединен с информационным входом узла сравнения, выход которого через элемент НЕ соединен с первым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход второго элемента задержки соединен с вторым входом элемента И, первые входы элементов P. группы объединены с соответствующими информационными входами блока свертки по модулю два и образуют группу информационных входов устройства для подключения к группе выходов контролируемого дешифратора, выход нечеткости блока свертки по модулю два соединен с нулевым входом триггера и вторыми входами элементов И группы, выходы которых образуют группу информационных выходов результата контроля устройства.

1495801

Составитель B.Ãðå÷íåâ

Редактор В.Бугренкова Техред М,Дидык Корректор И. Муска

Заказ 1 268/47 Тираж 668 Подпи сно е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101