Устройство управления динамической памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для режима или обмена и регенерации накопителей на динамических запоминающих элементах. Целью изобретения является упрощение устройства. Устройство содержит формирователь 1 сигналов регенерации, элемент 2И, элемент 3НЕ, триггеры 4 и 5, элементы И 6 и 11, триггеры 7,8,9 и одновибратор 10. С выхода формирователя 1 поступают сигналы запроса регенерации на вход триггера 4, по которому на выходе триггера 5 появляется импульс для инкремента адреса регенерации, а на выходе элемента 2И формируется сигнал выборки строки.Импульс одновибратора 10 блокирует возможность нового доступа к устройству на время завершения переходных процессов в накопителе. Запрос на обмен данными с накопителем поступает на вход триггера 7. При этом устройство формирует сигналы управления накопителем на выходах элемента 2И, триггеров 9 и 8 и сигнал ответа для задатчика с выхода элемента ЗНЕ. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 0 11 С 7/00

S<00N фТЕНТНЭ -1

Б115ЛИ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М A BTOPCHOMV СВИДЕТЕЛЬСТВУ

Та тс

Йрли

duyu

&unxz са

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР (21) 4346975/24-24 (22) 21. 12,87 (46) 23. 07. 89. Бюл. 11р 27 (71) Всесоюзный научно-исследовательский институт медицинского приборостроения (72) А.M.Каневский (53) 681.325(088.8) (56) Авторское свидетельство СССР 11 - 1051540, кл. Г 06 F 9/00, 1983.

Winter W. 64 К byte — DRAM mit

unabh%ngigem Refresh. — Radiofernsehenelektronik, ГДР, 1986, N - 12, S. 751-755. (54) УСТРОЙСТВО УПРАВЛЕНИЯ ДИНАМИЧЕСКОЙ ПАМЯТЬЮ (57) Изобретение относится к вычислительной технике и может быть использовано для режима или обмена и регенерации накопителей на динамических запоминающих элементах. Целью изобÄÄSUÄÄ 1495848 А 1

2, ретения является упрощение устройст- ва, Устройство содержит формирователь

1 сигналов регенерации, элемент И 2, элемент HE 3, триггеры 4 и 5, элементы И 6 и 11, триггеры 7, 8, 9 и одновибратор 10. С выхода формирователя 1 поступают сигналы запроса регенерации на вход триггера 4, по которому на выходе триггера 5 появляется импульс для инкремента адреса регенерации, а на выходе элемента И 2 формируется сигнал выборки строки. Импульс одновибратора 10 блокирует возможность нового доступа к устройству на время завершения переходных процессов в накопителе, Запрос на обмен данными с накопителем поступает на вход триггера 7. При этом устройство формирует сигналы управления накопи телем на выходах элемента И 1, тонг- С геров 9 и 8 и сигнал ответа для задатчика с выхода элемента НЕ 3 ° 3 ил.

Верн .3 1495848

Изобретение ОтнОсится к Вычислигсльной технике и может быть испольЗоваио для управления режимами обмена и регенерации накопителей, имеющих 5 ограниченное время хранения информации и выполненных, например, на

ИЦП-НИС.

Цель изобретения — упрощение устройства и повышение надежности. !О

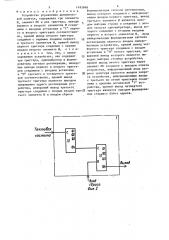

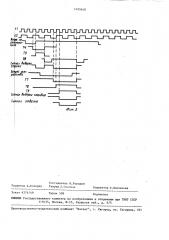

На фиг. представлена функциоальная схема устройства; на фиг. 2 хема формирователя сигналов регене ации; на фиг. 3 — временная диа-! рамма работы устройства.,! 5

Устройство содержит формирователь сигналов регенерации, элемент И 2, лемент НЕ 3, триггеры 4 и 5, элеент И 6, триггеры 7-9, одновибратор

0 и элемент И 11. Формирователь 1 20 одержит два .счетчика 12 и 13.

Устройство работает следующим образом.

Б исходном состоянии на выходе 25 формирователя 1 сигналов регенерации ус7ановлена логическая "1". Через промежуток времени, равный 13,4 мкс, на этом выходе формируется логический "0", что .является запросом на ре- 30 генерацию информации в накопителе.

Этот сигнал логического "0" вызывает срабатывание триггера 4, который своим инверсным выходом снимает блокировку с входа триггера 5, что приводит к срабатыванию этого триггера.

С инверсного выхода триггера 5 через элемент И 2 формируется сигнал выборки строки и одновременно подается сигнал сброса формирователя 1 сигнала 0 регенерации. Формирователь 1 сигнала регенерации приходит в исходное состояние. На его выходе снова устанавливается логическая "1", которая устанавливает в исходное состояние

45 триггер 4, что вызывает установку в исходное состояние триггера 5 и снятие сигнала выборки строки через элемент И 2. Одновременно с прямого выхода триггера 5 формируется перепад

50 из "1" в "0", который инкрементирует счетчик адресов регенерации. Цикл регенерации одной строки закончен, Следующий начинается после поступления нового запроса на регенерацию с

55 формирователя сигналов регенерации.

При поступлении запроса на обмен информации г устройством на входе запрос» ;стройства появляется логический "О", Это вызывает срабатывание триггера 7, который с прямого выхода через элемент И 2 формирует сигнал выборки строки, а с инверсного выхода снимает. блокировку с установочного входа триггера 8. Под установочным входом подразумевается вход триггера на котором появление сигнала логического "0" вызывает установку триггера в "!" или "О". В триггерах

4 и 7 используются установочные Sвходы, так как их исходное состояние — логическая "1". В триггерах

5-9 используются установочные R-входы, так как их исходное состояние

"0". Триггер 8 срабатывает и снимает блокировку с установочного входа триггера 9, а также устанавливает сигнал подачи старшего байта адреса.

Срабатывает триггер 9 и формирует сигнал выборки столбца и сигнал ответа через элемент НЕ 3.

Получив сигнал ответа, эадатчик проводит обмен информацией с накопителем, после чего снимает сигнал с входа запроса устройства, что вызывает переход в исходное состояние цепочки триггеров 7-9 и снятие выходных сигналов выборки строки, подачи старшего байта адреса, выборки столбца и ответа.

В случае одновременного поступления запросов на регенерацию и на обмен срабатывает один из триггеров

4 или 7, которые взаимно блокируются через элементы 11 и 6, Таким образом, при срабатывании триггера 4 осуществляется цикл регенерации, а цикл обмена откладывается до окончания регенерации и наоборот. Для исключения возможности самовозбуждения на цепочке положительной обратной связи и триггерах 4 и 7 эти триггеры должны стробироваться по С-входам от противоположной фазы одной и. той же опорной частоты.

При снятии сигнала выборки сраоатывает одновибратор 10, Одновибратор 10 в течение 250 мс держит на своем выходе сигнал логического "0" и через элементы 6 и 11 блокирует возможность начала нового цикла как обмена, так и регенерации. Это время необходимо для нормального восстановления микросхем накопителя после окончания предыдущего цикла.

7акт

ЧОС/77 сЮроса

Фиг. 2

5 14958 формула изобретения

Устройство управления динамической памятью, содержащее три элемента

И, элемент НЕ и два триггера, выходы

5 первого и второго элементов И соединены с входами установки в "1" первого и второго триггеров соответственно, прямой выход второго триггера соединен с первыми входами первого и третьего элементов И, прямой выход первого триггера соединен с первым входом второго элемента И, о т л ич а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит три триггера, одновибратор и формирователь сигнала регенерации, инверсные выходы первого и второго триггеров соединены с входами установки в "0" третьего и четвертого тригге- 20 ров соответственно, прямой выход третьего триггера является выходом приращения адреса регенерации устройства, инверсный выход третьего триггера соединен с вторым входом тре-25 тьего элемента И и входом сброса

48 6 формирователя сигналя регенерации, выход которого соединен с информационным входом первого триггера, выход третьего элемента И является выходом выборки строки и соединен с входом запуска одновибратОра, выход которого соединен с вторыми входами первого и второго элементов И, вход синхронизации формирователя сигнала регенерации является входом синхронизации устройства, прямой выхбд четвертого триггера соединен с входом установки в "О" пятого триггера, инверсный выход которого является выходом выборки столбца устройства, прямой выход пятого триггера через элемент HF. соединен с выходом ответа устройства, информационный вход вто рого триггера является входом запроса устройства, информационные входы с третьего по пятый триггеров соединены с уровнем логической "1" устройства, прямой выход четвертого триггера является выходом формирования старшего байта адреса.

1495848

Яв

РР ци

08

Си нал Рыйрю с оки

gu рс цщРд Стра

Т7 !

Tg

79

Манал Кы&рки товарца

Гйнал om8emu

Составитель В.Бородин

Редактор А,Козориз Техред Л.Олийнык Корректор Э.Лончакова

Заказ 4274/49

Тираж 558

Подписное

ВНИИПИ Государственного. комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101