Многоканальный преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью расширения диапазона работы в многоканальный преобразователь перемещения в код, содержащий синусно-косинусные датчики (СКД) 1, первый коммутатор 2, аналого-цифровой преобразователь (АЦП) 4, блок 5 памяти и блок 6 управления, введены второй коммутатор 3 и формирователь 7 кода грубого отсчета (ГО), который содержит аналоговый 8 и цифровой 9 компараторы, блок 10 постоянной памяти, блок 11 оперативной памяти, блок 12 сравнения и реверсивный счетчик 13. Блок 6 управления циклически вырабатывает коды адресов подключаемых каналов и последовательности управляющих импульсов. АЦП 4 формирует код точного отсчета (ТО) выбранного канала. Из блока 5 памяти в реверсивный счетчик 13 заносится код ГО выбранного канала. В блоке 12 путем сравнения текущего кода ТО с предыдущим кодом ТО выбранного канала формируются импульсы коррекции, поступающие на счетный вход реверсивного счетчика 13. При поступлении через коммутатор 3 маркерного сигнала, соответствующего нулевому положению вала СКД 1 выбранного канала, цифровой компаратор 9 сбрасывает реверсивный счетчик 13 в "О". В конце цикла код ТО запоминается в блоке 11, а код ГО - в блоке 5. В следующем цикле производится формирование кодов ТО и ГО следующего канала. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ социАлистических

РЕСПУБЛИК (gg 4 H 03 М 1/30

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ пРИ Гннт сссР (21) 4344441/24-24 (22) 15. 12. 87 (46) 23. 07.89. Бюл. Р 27 (72) В,A. Булавский, M. А. Габидулин, И.Д.Лейбович, В.В.Лобко, Ю. Н.Михалев, Г.Д.Панкин и С.В,Титов (53) 681.325(088.8) (56) Вульвет Дж. Датчики в цифровых системах. Пер. с англ. под ред.

А.С.Яроменка. — М.: Энергия, 1981, с. 95-97, 50, рис. 4-4 — 4.7, 2.21.

Авторское свидетельство СССР

1325700, кл. Н 03 М 1/30, 1985.

Авторское свидетельство СССР

Ф 991468, кл. H 03 M 1/48, 1981. (54) МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ПЕРЕМЕЩЕНИЯ В КОД (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, С целью расширения диапазона рабаты в многоканальный преобразователь перемещения в код, содержащий синуснокосинусные датчики (СКД) 1, первый коммутатор 2, аналого-цифровой преобразователь (АЦП) 4, блок 5 памяти 4 блок 6 управления, введены второй

„„SU„„1495994 A 1

2 коммутатор 3 и формирователь 7 кода грубого отсчета (ГО), который содержит аналоговый 8 и цифровой 9 компараторы, блок 10 постоянной памяти, блок 11 оперативной памяти, блок 12 сравнения и реверсивный счетчик 13.

Блок 6 управления циклически вырабатывает коды адресов подключаемых каналов и последовательности управляющих импульсов. АЦП 4 формирует код точного отсчета (ТО) выбранного канала. Из блока 5 памяти в реверсивный счетчик 13 заносится код ГО выбранного канала. В блоке 12 путем сравнения текущего кода ТО с предыдущим кодом ТО выбранного канала формируются импульсы коррекции, постуе пающие на счетный вход реверсивного счетчика 13. При поступлении через коммутатор 3 маркерного сигнала, соответствующего нулевому положению вала СКД 1 выбранного канала, цифровой компаратор 9 сбрасывает реверсивный счетчик 13 в "0". В конце цикла код р

ТО запоминается в блоке 11, а код

ГΠ— в блоке .5. В следующем цикле производится формирование кодов ТО и ГО следующего канала. 1 з.п. ф-лы, 3 ил.

3 !49599

Изобретение относится к автоматиКе и вычислительной технике и может быть использовано для связи аналогоВых источников с цифрровым вычисли5 тельным устройством, Целью изобретения является расши" рение диапазона работы преобразователя путем формирования кода грубого отсчета. !О

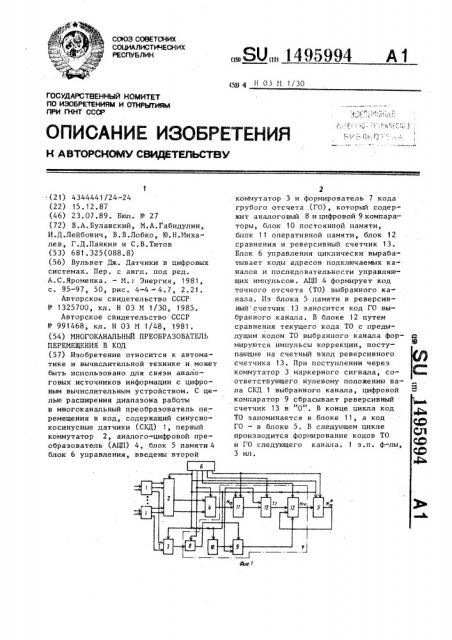

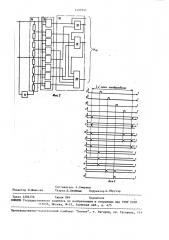

На фиг. 1 приведена структурная схема многоканального преобразовате1 пя, на фиг. 2 - структурная схема аналого-цифрового преобразователя (АЦП); на фиг. 3 — временная диаграм- 15 иа работы многоканального преобразователя.

Многоканальный преобразователь пе ремещения в код (фиг. 1) содержит синусно-косинусные датчики (СКД) коммутаторы 2 и 3, АЦП 4, блок 5 памяти, блок 6 управления и формирователь 7 кода грубого отсчета (ГО), содержащий аналоговый 8 и цифровой 9 ,компараторы, блок 10 постоянной памя- 25 ти, блок 11 оперативной памяти, блок

12 сравнения и реверсивный счетчик 13.

АЦП 4 (фиг. 2) содержит делитель

14 напряжений, блок 15 компараторов, шифратор (6 и фазоинвертор 17. Шифра- 3п тор 16 содержит сумматоры 18 — 20 по модулю два.

Многоканальный преобразователь перемещения в код работает следующим образом.

При.отсутствии выходного сигнала циф рового компаратора 9 сброс в ноль

Блок 6 управления циклически вырабатывает коды адресов подключаемых каналов (фиг. Зд) и может быть выпол- нен, например, в виде последователь- 4О но соединенных генератора импульсов, счетчика и дешифратора. Синусно-косинусные сигналы СКД 1 выбранного канала через коммутатор 2 (фиг. 3e) поступают на входы АЦП 4, где преобра- 45 зуются в код угла точного отсчета (ТО) в пределах полюсного деления.

Фазоинвертор 17 вместе с делителем 14 (фиг. 2) образуют фазорасщепитель, из выходных сигналов которого в бло50 ке 15 компараторов по сигналу блока 6 (фиг. 3a) вырабатывается однопеременный код. При использовании в блоке 15 компараторов типа КР597СА2 с запоминанием сформированный код запоминается и в шифраторе 16, выполненном на сумматорах по модулю 2, и преобразуется в двоичный арифметический код (фиг. Эк).

4 4

Кроме того, на выходах датчиков 1 вырабатываются маркерные сигналы, соответствующие нулевому состоянию вала соответствующего СКД. Маркерный сигнал выбранного канала череэ коммутатор 3 поступает на информационный вход комиаратора 8, где по управляющему импульсу блока 6 запоминается (фиг. Зл) в виде "1" или "О" в зависимости от наличия или отсутствия маркерного сигнала

С выходов АЦП 4 код точного отсчета поступает на информационные входы записи блока 11 оперативной памяти, а ll 1и п2 старших разрядов этого кода И, И т поступают на первые группы входов блока 12 сравнения и цифрового компаратора 9 соответственно. В блоке 12 по выходному сигналу блока 6 .(рис. Эв) производится сравнение кода N „, текущего отсчета с кодом N1 д предыдущего от счета с выходов блока 11 оперативной памяти и вырабатываются. импульсы +! коррекции кода ГО, которые поступают на счетные входы реверсивного счетчика 13 (фиг. 3o).

Одновременно в цифровом компараторе 9 производится сравнение кода

N., „ с выходным кодом блока 10 (фиг, Зи) постоянной памяти, в который при регулировке преобразователя для каждого СКД 1 заносятся коды положения маркерного сигнала в диапазоне кода ТО, При совпадении входных кодов цифрового компаратора 9 и наличии единичного маркерного сигнала с выхода аналогового компаратора 8 (в нулевом периоде ТО) выходной сигнал цифрового компаратора 9 сбрасывает в ноль реверсивный счетчик 13 (фиг.Зм). реверсивного счетчика 13 не производится.

Одновременно с подключением выходных сигналов СКД выбранного канала на выходах блока 5 формируется код ГО предыдущего измерения в данном качале (фиг. Зз), который поступает на установочные входы реверсивного счетчика 13 и заносится в него пс сигналу блока 6 (фиг. Зб,н). Код предыдущего цикла измерения в данном канале корректируется выходными импульсами блока 12 в текущем цикле измерения. В результате в реверсивном счетчике 13 формируется текущий код ГО (фиг.Зн), 1495994 который ио адресу подключенного кана-ла и выходному импульсу блока 6 (фиг. 3r) записывается в блок 5 памяти (фиг. Зз). По этому же импульсу блока 6 (фиг. Зг) в блок 11 памяти записывается текущий код N, (фиг.Зж)

На этом преобразование в текущем цикле с выбранным СКД 1 заканчивается и блок 6 вырабатывает адрес подключения следующего СКД 1, и цикл преобразования со следующим СКД 1 повторяется.

Формула изобретения

1. Многоканальный преобразователь перемещения в код, содержащий синусно-косинусные датчики, синусный и косинусный выходы которых соединены с информационными входами первого коммутатора, выходы первого коммутатора соединены с информационными входами аналого-цифрового преобразователя, блок памяти, блок управления, группа выходов которого соединена с группой управляющих входов первого коммутатора и группой управляющих входов блока памяти, первый выход блока управления соединен с управляющим входом аналого-цифрового преобразователя, отличающийся тем, что, с целью расширения диапазона работы преобразователя, в него введены второй коммутатор и формирователь кода грубого отсчета, дополнительные выходы синусно-косинусных датчиков соединены с информационными входами второго коммутатора, управляющие входы которого подключены к группе выходов блока управления, а выход соединен с информационным входом формирователя кода грубого отсчета, выходы аналого-цифрового преобразователя и выходы блока памяти соединены соответственно с первой и второй группами информационных входов формирователя кода грубого отсчета, группа выходов и выходы с первого по четвертый блока управления соединены соответственно с группой

5 в

l0 !

50 управляющих входов и с управляющими входами с первого по четвертый формирователя кодов грубого отсчета, выходы которого соединены с информационными входами блока памяти, а четвертый выход блока управления соединен с управляющим входом блока памяти.

2. Преобразователь по и. 1, о тл и ч а ю шийся тем, что формирователь кода грубого отсчета содержит аналоговый компаратор, цифровой компаратор, блок постоянной памяти, блок оперативной памяти, блок сравнения и реверсивный счетчик, информационный вход аналогового компаратора, информационные входы блока оперативной памяти и установочные входы реверсивного счетчика являются соответственно информационным входом, первой и второй группой информационных входов формирователя кода грубого отсчета, группа управляющих входов блока оперативной памяти, управляющие входы аналогового компаратора, реверсивного счетчика, блока сравнения и блока оперативной памяти являются соответственно группой управляющих входов и управляющими входами с первого по четвертый формирователя кода грубого отсчета, первая и вторая группы информационных входов блока оперативной памяти соединены с первыми группами входов .соответственно блока сравнения и цифрового компаратора, выходы блока оперативной памяти соединены с второй группой информационных входов блока сравнения, выходы которого соединены со счетными входами реверсивного счетчика, группа управляющих входов блока оперативной памяти через блок постоянной памяти соединена с второй группой информационных входов цифрового компаратора, управляющий вход которого подключен к выходу аналогового компаратора, а выход соединен с входом сброса реверсивного счетчика, выходы которого являются выходами формирователя кода грубого отсчета.

i 495994

Составитель А.Смирнов

Техред Л.Олийнык Корректор А-Обручар

Редактор И.Шмакова

Заказ 428б/56 Тираж 884 Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Гаушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101