Устройство избирательного вызова

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Устр-во содержит переключатель 1, преобразователь 2 сигнала, блок сравнения 3, интегратор 4, блок индикации 5, блок синхронизации 6, генератор-делитель 7, управляющий регистр 8, дешифратор 9, таймер 10 и анализатор 11 сигналов. Принцип работы устр-ва избирательного вызова основывается на осуществлении анализа элементарных посылок кодовой вызывной последовательности и использовании временного различия истинных и ложных синхроимпульсов. При этом временной интервал для анализа синхроимпульсов задается таймером 10. В устр-ве используется синхронный метод обработки сигналов и применяется способ фазирования по рабочим импульсам. Это обеспечивает надежное подключение устр-ва к вызывному каналу на все время его анализа. Повышение помехоустойчивости к воздействию импульсных помех и посторонних сигналов достигается за счет исключения накопления ложных импульсов и сокращения времени анализа вызывных каналов при наличии в них помех. 2 ил.

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg 4 Н 04 Я 5/04 Ю И3

П%ТЕЧТНО - ЧлРИЧЕьИЯ

Б ББИЗТЕ А

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPGHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4231813/24-09 (22) 04.03.87 (46) 23.07.89. Бюл. Р 27 (72) Г.И.Азаров и В.П.Новиков (53) 621.395.63 (088.8) (56) Авторское свидетельство СССР

Р 809666, кл. Н 04 Q 5/04, 1979. (54) УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА (57) Изобретение относится к технике связи. Цель изобретения — повышение помехоустойчивости. Устр-во содержит переключатель 1, преобразователь 2 сигнала, блок сравнения 3, интегратор 4, блок индикации 5, блок синхронизации 6, генератор-делитель 7, управляющий регистр 8, дешифратор

9, таймер 10 и анализатор 11 сигналов. Принцип работы устр-ва избира„„SU„„1496014 А 1 тельного вызова основывается на осуществлении анализа элементарных посылок кодовой вызывной последовательности и использовании временного различия истинных и ложных синхроимпульсов. При этом временной интервал для анализа синхряимпульсов задается таймером 10. В устр-ве используется синхронный метод обработки сигналов и применяется способ фазирования по рабочим импульсам. Это обеспечивает надежное подключение устр-ва к вызывному каналу на все время его анализа. Повышение помехоустойчивости к воздействию импульсных помех и посторонних сигналов достигается эа счет исключения накопления ложных импульсов и сокращения времени анализа вызывных каналов при наличии в них помех. 2 ил.

149601

Изобретение относится к технике связи и может быть использовано в составе многоканальных систем приема и обработки избирательных сигна25 ку каждому каналу соответствует своя вызывная кодовая последовательность, то одновременно с переключением кана-50 лов происходит и смена кодовых последовательностей, записанных в дешифраторе 9 и используемых для анализа принимаемых сигналов. Управление работой переключателя 1 и смена кодовых55 последовательностей в дешифраторе 9 обеспечиваются с помощью управляющего регистра 8, тактовые импульсы для которoI" о формируются с помощью генелов.

Цель изобретения — повышение помехоустойчивости.

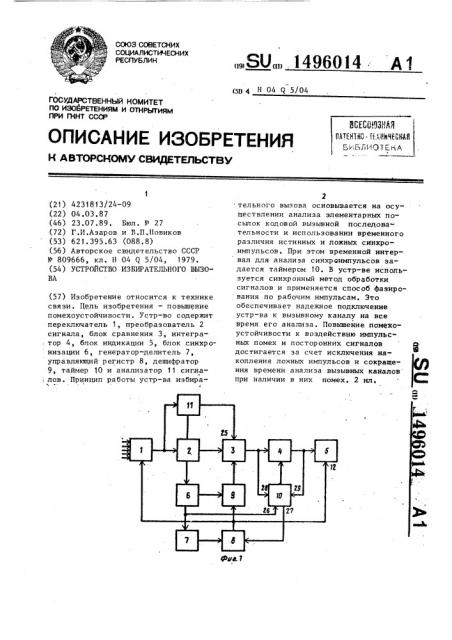

На фиг. 1 приведена блок-схема устройства избирательного вызова; на фиг. 2 — возможная схемотехническая реализация анализатора сигналов.

Устройство избирательного вызова содержит переключатель i, преобразователь 2 сигнала, блок 3 сравнения, 15 интегратор 4„ блок 5 индикации, блок 6 синхронизации, генератор-де литель 7, управляющий регистр 8, дешифратор 9, таймер 10, анализатор

11 сигналов, вход 12 блока 5, элемен- 20 ты ИЛИ-НЕ 13 и 14, инвертор 15, счетчик 16, элемент ИЛИ-HE 17, счетчик 18, регистр 19, элементы И вЂ” НГ

20, 21 и 22; дешифратор 23, элемент

ИЛИ 24, вход 25 блока 3, вход 26 таймера 10, выход 27 таймера 10, вход 28 таймера 10 и вход 29 таймера

10.

Принцип работы устройства избирательного вызова основывается на осуществлении анализа элементарных посылок кодовой вызывной последовательности и использовании временного различия .истинных и ложных синхроимпульсов, причем временной интервал 35 для анализа синхроимпульсов задается таймером 10.

Устройство работает следующим образом.

В исходном состоянии, когда сигналы 40 вызова не поступают ни по одному из каналов на входы устройства избирательного вызова, переключатель 1 осу- ществляет поочередное подключение каждого канала к входу преобразова- 45 теля 2 на время, необходимое для анализа наличия сигнала вызова. Посколь4 4

/ ратора-делителя 7. Кроме того, одновременно со сменой канала информация о его номере с выхода управляющего регистра 8 подается на вход 12 блока 5.

При наличии в каком-либо канале сигнала вызова, который представлен кодовой последовательностью двух тональных частот, этот сигнал через переключатель 1 поступает на.вход преобразователя 2, формирующего соответствующие импульсные последовательности. Сформированные импульсные последовательности поступают на вход блока 3 сравнения и на вход блока 6 синхронизации, который вырабатывает тактовые импульсы для дешифратора 9.

Кроме того, последовательность двух тональных частот - с выхода переключателя 1 поступает на вход анализатора 11, который представляет собой следящий частотомер, анализирующий наличие или .отсутствие в канале сигналов требуемой частоты. Принцип действия анализатора 11 основан .на подсчете числа импульсов за образцовый интервал времени, который составляет 0,8-0,9 длительности эле" ментарной посылки.

Анализатор 11 работает следующим образом.

Генератор образцовой частоты, вы- полненный на элементах ИЛИ-НЕ 13 и

14, вырабатывает последовательность импульсов, поступающую через инвертор 15 на счетчик 16. Пока на его выходе напряжение логического нуля, элемент ИЛИ-НЕ 17 пропускает последовательность выходных импульсов на счетчик 18. По окончании интервала счета фронтом импульса с выхода счетчика 16 происходят блокировка элемента ИЛИ-HE 17 и одновременная запись в регистр 19 информации с выходов счетчика 18. Положительным перепадом импульса с выхода элемента

ИЛИ-НЕ 14 элементами 20 и 21 формируется импульс сброса счетчиков 16 и 18. Аналогичный импульс сброса но без записи в регистр 19, вырабатывается узлом защиты от переполнения, выполненным на элементах И-НЕ .22 и 21. Это происходит при переполнении счетчика 18, когда на входах элемента И-,НЕ 22 одновременно появляется сигнал логической единицы.

Узел защиты исключает появление ложной команды на выходе дешифратора

5 14

23. Последний преобразует сигналы, поступающие из регистра 19, в десятичную форму представления. При этом на двух соответствующих выходах дешифратора 23 появляются сигналы, соответствующие приему двух тональных частот. Эти сигналы через элемент ИЛИ 24 подаются на вход 25 блока 3 сравнения, обеспечивая в дальнейшем выдачу сигналов с его выхода (например, открывая электронный ключ).

В устройстве избирательного вызова используется синхронный метод обработки сигналов. При этом применяется способ фазирования по рабочим импульсам, заключающийся в том, что блок 6 из всей кодовой последовательности выделяет моменты смены полярности рабочих импульсов (моменты перехода "1" в "О" и "О" в "1") и формирует в эти моменты импульсы синхронизации. Эти импульсы обеспечивают подстройку фазы тактовых импульсов дешифратора 9. Кроме того, импульсы синхронизации на вход 26 таймера 10, который представляет собой ждущий мультивибратор. Первым синхроимпульсом таймер 10 запускается и вырабатывает импульс, длительност которого выбирается в 1,5-2 раза больше длительности одной посылки в импульсной последовательности вызывного сигнала.

Этот импульс с выхода 27 таймера

10 поступает на вход управляющего регистра 8, блокируя его и препятствуя выдаче им сигналов на переключение каналов и дешифратора 9 (например, разрывая связь с помощью электронного ключа между генераторомделителем 7 и управляющим регистром

8). Хаким образом, устройство избирательного вызова остается подключенным к тому каналу, по которому поступает кодовая последовательность.

Анализ поступающей кодовой импульсной последовательности осуществляется в блоке 3 сравнения, который сопоставля. ет ее с эталонной адресной последовательностью, записанной в дешифраторе 9. Сравнение кодовых последовательностей производится поимпульсно.

Совпадение каждой пары импульсов (при Наличии разрешающего сигнала с анализатора 11) фиксируется в ин- теграторе 4, представляющем собой десятичный счетчик. Кроме того, им96014 пульсы совпадения поступают на вход

28 таймера 10 и перезапускают его.

Тем самым обеспечивается надежное подключение устройства избирательного вызова к вызывному каналу на все время его анализа. При поступлении подряд импульсов совпадения (величина N определяет порог срабатывания интегратора 4 и выбирается исходя из допустимой вероятности ложного приема кодовой комбинации длиной

N элементов) с выхода интегратора 4 поступает сигнал в блок 5 индикации, который фиксирует как факт наличия вызова, так и номер канала, по которому вызов поступил (по сигналу с управляющего регистра 8) °

Этим же сигналом по входу 29 бло20 кируется таймер 10 (разрывается связЬ от блока 3 сравнения) . Вследствие этого снимается блокирующий сигнал с входа управляющего регистра

8 и он (с очередным тактовым иипуль25 сом) переводит переключатель 1 и дешифратор 9 на анаЛиз следующего канала. Кроме того, задним фронтом импульса таймера 10 интегратор 4 сбрасывается в исходное состояние

30 (счетчик обнуляется).

Таким образом, устройство избирательного вызова обладает. высокой помехозащищенностью.. Так как формирование импульсов синхронизации происхо35 дич ч олько в моменч ы смены полярности рабочих импульсов, то при наличии в анализируемом канале помех (шумовых, широкополосных) и отсутствии вызывных сигналов импульсы синхрони40 зации с выхода блока 6 не поступают и таймер 10 находится в исходном состоянии. Кроме того, осуществляется трехступенчатый параллельный анализ принимаемого сигнала: анализ

45 частоты и длительности посылкй в анализаторе 11 сигналов и анализ структуры сигнала в блоке 3 сравнения.

Т.е. для того, чтобы помеха воздействовала на устройство избирательного

50 вызова, необходимо совпадение трех условий: ее длительность должна быть не менее 0,8-0,9 длительности элементарной посылки, она должна иметь соответствующее частотное заполнение

55 и ее логическое представление (О или 1) должно совпасть с записанным в дешифраторе 9. Вероятность совпадения трех взаимонезависимых событий крайне мала. Голи вследствие воэдей1496014

Формула изобретения

Устройство избирательного вызова, содержащее последовательно соединен; ные переключатель, преобразователь сигнала, блок сравнения, интегратор и блок индикации, последовательно соединенные блок синхронизации, .reСоставитель Г Корсаков

Техред М.,яндык Корректор О.Ципле

Редактор И. Горная

Заказ 4288/57 Тираж 626 Подписное

ВНИИПИ Государственногб комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5 ю

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ствия импульсной помехи или сигналов пос тор онних корр еспондентов ложный синхроимпульс все же будет выработан, то произойдет только кратковременное срабатывание таймера 10, который, не получая сигналов с выхода блока 3, быстро вернется в исходное состояние. При этом задним фронтом импульса таймера 10 происходит дополнительное обнуление интегратора 4, что исключает накопление ложных импульсов и повышает надежность работы.

Таким образом, преимущества устройства избирательного вшзова состоят в повышении его помехоустойчивости к воздействию импульсных помех и посторонних сигналов, а также в сокращении времени анализа вызывных каналов при наличии в них помех. нератор-делитель, управляющий регистр и дешифратор, при этом второй выход преобразователя сигнала подключен к входу блока синхронизации, второй выход которого подключен к второму входу дешифратора, выход которого подключен к второму входу блока сравнения, а выход управляющего регистра-к управляющему входу переключателя, М информационных входов которого являются соответственно

M входами устройства избирательного вызова, о т л и ч а ю щ е е с я

15 тем, что, с целью повышения помехоустойчивости, введены таймер и анализатор сигналов, вход и выход которого подключены соответственно к вы-.

1 ходу переключателя и третьему входу

20 блока сравнения, выход которого подключен к первому входу таймера, второй и третий входы которого подключены соответственно к входу генератора-делителя делителя частоты и вы1 ходу интегратора, второй вход которого йодключен к, первому выходу таймера, второй выход которого подключен к, второму входу управляющего регистра, въ1ход которого подключен к второму

З0 входу блока индикации.