Устройство для регенерации динамической памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к динамическим запоминающим устройствам и может быть использовано для передачи данных в устройствах автоматики и вычислительной техники с синхронной произвольно-последовательной выборкой. Цель изобретения - повышение быстродействия. Устройство содержит коммутатор , два регистра, компаратор, триггер, адресные и управляющие входы и выходы. Триггер задает режим работы устройства. В первом регистре запоминается последний строчный адрес внешнего обращения в текущем периоде регенерации, во втором регистре - адрес последнего обращения в предыдущем периоде. Из цикла регенерации исключаются адреса, прорегенерированные в текущем периоде регенерации. 1 ил.

СОЮЗ СОВЕТСНИХ . СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (511 4 G 11 С 21/00

g. РГ ;" 11 11 1-„-и 5

/ 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY С8ИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ .СССР (21) 4323013/24-24 (22) 02.11.87 (46) 30.07.89. Бюп. Р 28 (71) Львовский политехнический институт им. Ленинского комсомола (72) П.А.Кондратов и И.Б.Боженко (53) 681.327 (088.8) (56) Полупроводниковые ГИС запоминающих устройств. Справочник под ред.

А.И.Гордонова и И.Н.Дьякова. М.: Радио и связь, 1987, с. 87-90, рис ° 5,9.

Авторское свидетельство СССР

Р 691925, кл. G 11 С 11/34, 1979. (54) УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ (57) Изобретение относится к динамическим запоминающим устройствам и моИзобретение относится к запоминающим устройствам и может быть исполь» зовано для передачи данных в устройствах автоматики и вычислительной техники с синхронной произвольно последовательной выборкой.

Цель изобретения — повышение быстродействия устройства.

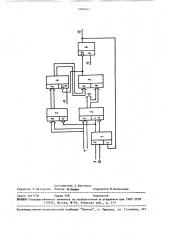

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит коммутатор 1, первый регистр 2, счетчик 3, второй регистр 4, блок 5 сравнения, триггер

6 адресные входы 7 и выходы 8, вход

9 импульсов записи адресов, вход 10 . импульсов регенерации, вход 11 сброса вход 12 регенерации и выход 13, режима.

„,SU„„1497637 А1

2 жет быть использовано для передачи данных в устройствах автоматики и вычислительной техники с синхронной произвольно последовательной выборкой. Цель изобретения — повышение быстродействия. Устройство содержит коммутатор, два регистра, компаратор, триггер, адресные и управляищие входы и выходы. Триггер задает режим работы устройстна. В первом регистре запоминается последний строчный адрес внешнего обращения в текущем периоде регенерации, но нтором регистре - адрес последнего обращения в предыдущем периоде. Из цикла регенерации исключаются адреса, прорегенерированные в текущем периоде регенерации. I ил .

По входу 7 поступают строчные адреса внешних обращений, по входу 9их стробы.

Устройство работает следующим образом.

После подачи питающего напряжения регистры и счетчик устанавливаются произвольно, а для перевода динамической памяти н нормальный режим

Ъ функционирования необходимо произвести несколько циклов регенерации. Для этого по входу 11 на регистр 4 и по входу 12 на триггер 6 подаются импульсы сброса. Устройство перенодится в режим регенераиии. JIo нулевому состоянию триггера 6 коммутатор 1

1 блокирует подачу сигиалон установки

l 49 7637 на счетчик 3 и ра. реиает поступление на еro счетньп1 вход импульсов регенерации со входа 10. Счетчик 3 начинает генерировать строчные адреса, которые 5 с выхода 8 пос тупают на адре сные шины. По установке счетчика в нулевое состояние блок 5 сравнения вырабатъ вает иипульс, который своим задним фронтом устанавливает триггер 6 и устройство переводится в режим внешнего обращения, которое определяется по состоянию выхода 13. Операция повторяется до перехода динамической памяти в режим нормального функциони- 15 рования.

В режиме внешнего обращения коммутатор I блокирует поступление импульсов регенерации и разрешает прохождение сигналов внешнеro обращения 20 со входами 9. По ним строчные адреса внешнего обращения заносятся в регистр 2 и счетчик 3 и с выхода последнего поступают на адресные шины.

По истечен и периода регенерации 25 памяти Т со входа l2 поступает импульс сброса триггера 6. Устройство переводится в режим регенерации, начинается следующий Т„ „. С началом цикла регенерации в регистре 2 и 30 счетчике 3 хранится последний строчный адрес, поступивший в предыдущем (i-том) Т„ -A;. При этом в регистре

4 хранится А

С поступлением импульсов регенерации на счетный вход счетчика 3 он начинает генерировать строчные адреса, начиная с Л;. При совпадении состояния счетчика со значением А;, блок 5 вырабатывает импульс, по кото- 40 рому во второй регистр 4 переэаписывается значение А; и устанавливается триггер 6 — начинается следующий цикл внешнего обращения, в конце которого в первый регистр 2 и счетчик 3 эано- 45 сится А,, . Условием выполнения pere нерации будет 2TRE„ < TREF макс где

1 Ксг м кс макс!1малы(о ло !gс 1 имьГЙ пp риод регенерации и длительность загрузки памяти Т ) T

Таким образом, иэ цикла регенерации исключаются адреса, по которым в текущем Т„ производились внешние обращения, (то сокращает длительность этого цикла и тем самым повышает быстродействие устройства.

Формула и э обретения

Устройство для регенерации динамической памяти, содержащее коммутатор, первый регистр и счетчик, выходы которого являются адресными выходами устройства, информационные входы счетчика являются адресными входами устройства и подключены к информационным входаи первого регистра, синхронход которого подключен к первому выходу комиутатора и входу установки счетчика, с 1етный вход которого подключен к второму входу коммутатора, первый и второй информационные входы которого являются соответственно входом импульсов записи адресов и входом импульсов регенерации устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит второй регистр, блок сравнения и триггер, выход которого является выходом режима устройства и подключен к управляющему входу коммутатора, вход сброса триггера является входом регенерации устройства, вход установки триггера подключен к выходу блока сравнения и синхровходу второго регистра, вход сброса которо.— го является соответствующим входои устройства, выходы второго регистра подключены к входам первой группы блока сравнения, входы второй группы которого подключены к выходам счетчика, выходы первого регистра подключе." ны к информационным входам второго регистра.

l 4g163 у

Составитель С.В1устенко

Редактор Т.Лазоренко Техред М,Дидык Корректор М.Васильева

Заказ 4447/50 Тирам 558 Подписное.

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", r. Умгород, ул. Гагарина, 101