Преобразователь напряжения для кварцевых наручных часов

Иллюстрации

Показать всеРеферат

Изобретение относится к преобразованию электрической энергии и может быть использовано для создания преобразователей постоянного напряжения в постоянное для кварцевых наручных часов. Целью изобретения является улучшение качества напряжения на выходе устройства путем уменьшения пульсаций и времени нарастания при увеличении нагрузки. Преобразователь напряжения содержит конденсаторную ячейку умножения, выполненную на четырех МОП-транзисторах 1-4, преобразователь уровней, кольцевой генератор, дополнительный МОП-транзистор 5, включенный параллельно выходному МОП-транзистору 2 ячейки, детектор 33 изменения нагрузки и формирователь на элементах 19-21. 3 з.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1497695 А 1 (11 4 Н 02 М 3/335

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4385007/24-07 (22) 26.01.88 (46) 30.07.89. Бюл. М 28 (71) Научно-исследовательский институт часовой промышленности.и Производственное объединение "Минский часовой завод" (72) F..А.Занис, В.А.Обухович, 3,Д. Свиридов, С. П.111ацов и А.П.Невьев (53) 621.314.57 (088.8) (56) Авторское свидетельство СССР

11(771817, кл . Н 02 М 3/155, 1978.

Патент С1ЧА !!(4.344 ° 003, кл. Н.02 М 3/155, 1982. (54) ПРЕОБРАЯОВАТЕЛЬ НАПРЯЖЕНИЯ ДЛЯ

КВАРЦЕВЫХ НАРУЧНЫХ ЧАСОВ (57) Изобретение относится к преобра2 зованию электрической энергии и может быть использовано для создания преобразователей постоянного напряжения в постоянное для кварцевых наручных часов. Целью изобретения является улучшение качества напряжения на выходе устройства путем уменьшения пульсаций и времени нарастания при увеличении нагрузки. Преобразователь напряжения содержит конденсаторную ячейку умножения, выполненную на четырех МОП-транзисторах

1-4, преобразователь уровней, .кольцевой генератор,,дополнительный МОПтранзистор 5, включенный параллельно выходному МОП-транзистору 2 ячейки, детектор 33 изменения нагрузки и формирователь на элементах 19-21.

3 э.п.ф-лы, 3 ил., 3 !497695 4

Изобретение от«осится к преобра- ОтношенИе W/I. д эонлник1 электрической энергии и рон 1-4 выбирается может быть использовано для создания до 40, а для МОП-т преобразователей постоянного напряже- пределах от 4 до 8

5 ния в постоянное для кварцевых наруч- ся существенное ра ных часов, работающих от серебряно- времени разряда ко цинковых элементов с ЭДС 1,55 В. включении MOII-тран

Целью изобретения является улучше- временном включени ние качества напряжения на выходе !О 5 и 2. устройства путем уменьшения пульса- Детектор измене ций и времени нарастания при увеличе- (фиг.2) содержит р нии нагрузки. пдлненный на D-три

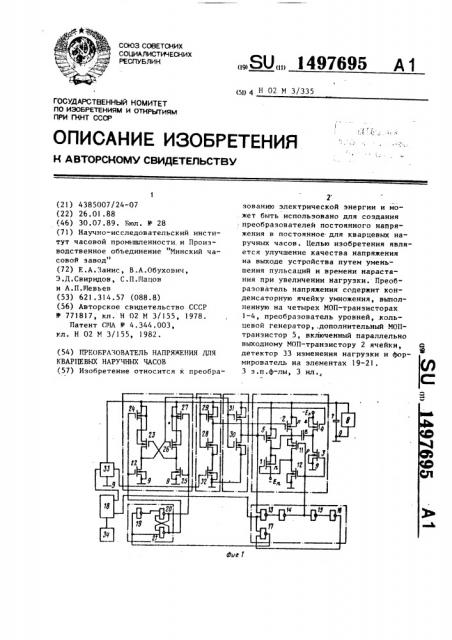

На фиг.1 изображена принципиальная D-триггера 39,40, схема устройства; на фиг.2 — вариант !5 элементы И 43,44 и выполнения детектора изменения наг- уровней, ныполненн руэки; на фиг.3 — временные диаграм = эисторах 45-50, нк мы работы преобразователя. триггера.

Преобрлэонатель напряжения (фиг.1) Преобразователь содержит ячейку умножения, образован- 20 ет следующим обра ную четырьмя основными МОП-транзисто- Кварцевый генер рами 1 — 4 и дополнительным MOII-тран- вает нремязадающие эистором 5 и конденсатором 6. Сгла- той, составляющей живающий конденсатор 7 включен парал- ручных часов 32 76 лельно нагрузке 8 между общей 9 и 25 образуются в делит выходной 10, шинами. Затвор МОП-тран- довательности импу зистора 1 соединен с выходом иннерто- частотой п Гц на 1 ра, образованного YOII-транзисторами тавляет 32-1000. П

11,12, вход иннертора соединен с ценой генератор ме затнором МОП-транзистора 3 и выходом 30 Il Гц преобразуется кольцевого генератора, выполненного тельности импульсо на инверторах И-HE 13 — 16 и элемен- на выходах логичес те ИЛИ-HE !7. Вход элемента ИЛИ-HE 18, которые смещен

17 соединен с первым выходом делителя определяемое задер

18, на котором формируется меандр с 35 ния сигнала. МОП-т частотой следования импульсов от 32 которые во включен до 1000 Гц, л выход элемента ИЛИ-НЕ отделены электриче !

7 соединен с входом формирователя, шины 10 закрытыми выполненного в виде триггера на ин- 2,4,5 управляются нерторах 19-21, выходы которого сое- 40 ра 14: MOII-транзис динены с входами преобразователя уров- венно, à MOII-транз ней, выполненного в виде триггера инвертор на MOII-тр на МОП-транзисторах 22-27. который обеспечива

Выход преобразователя соединен со 45 входами иннерторов, выполненных на

MOH-трлнзисторлх 28-31, исток MOIIтранзистора 28 соединен с общей шиной 9 через ключевой элемент, выполненный н виде МОП-транзистора 32, затвор кот>pnro соединен с выходом детекторл 33 изменения нагрузки.

Вход детектора изменения нагрузки соединен с вторым выходом делителя

18,на котором формируется меандр с частотой следования импульсов Гц.

Нл вход пел«тели подаются стабилизировлнные «о члстоте импульсы от кнлр- левого ге«ер, тора 34. ля МОП-транзистов пределах от 20 ранзистора 5 — в что обеспечиваетзличие постоянных нденсатора 7 и при зистора 5 и однои МОП-транзисторов ния нагрузки егистр сдвига, выггерах 35-38, два инверторы 41,42, преобразователь

ый на МОП-транлюченньж по схеме напряжения работазом. атор 34 вырабатыимпульсы с частодля кварцевых на8 Гц, которые пре-r. еле 18 н две послельсов — меандры с

Гц, где и сосоступающий на кольандр с частотой в две последовав, вырабатываемых ких элементов 14,, и на некоторое dt, жкой распространеранзисторы 1 и 3, ном состоянии ски от выходной

МОП-транзисторами с выходом инвертотор 3 непосредстистор I â€, через анзисторах 11,12, ет смещение отрицательного уроння на затворе МОПтранзистора 1 до напряжения на его стоке, которое в установившемся режиме колеблется в пределах -1,5 +

+ -2,8 В. МОП-транзисторы 2,4 и 5, связанные электрически с выходйой шиной 10, управляются через преобразователь уровней, выполненный йа

МОП-транзисторах 22-25. Формирователь выполненный на логических элементах

19-21, разделяет снимаемые с выхода элемента ИЛИ-НЕ 17 cHrHaJIbl Ha две последовательности импульсов, находящихся н противофазе, необходимые для работы преобразователя .уровней. На выходе преобразователя урон5 149 ней включены инверторы на МОЛ-транзисторах 28-31, обеспечивающие усиление сигнала по току.

Допустим схема находится в состоянии, при котором MOIL-транзисторы 1,3 включены, а 2,4,5 — выключены. В этом состоянии конденсатор 6 эаряжается через открытые транзисторы 1,3, а конденсатор 7 разряжается через нагрузку 8. В конце стадии заряда конденсатор оказывается заряженным до напряжения — F.1,, а конденсатор 7 разряженным до некоторого напряжения U „„. В следующем состоянии схемы

МОП-транзисторы 1,3 выключены, а

2,4 или 2,4,5 — включены. В этом состоянии схемы конденсатор 6 разряжается через MOII-транзисторы 2,4 или

2,4,5 на конденсатор 7 и нагрузку 8, а конденсатор 7 — заряжается. По окончании стадии разряда напряжение на конденсаторе 6 уменьшается до не) которого значения U», а напряжение на конденсаторе 7 — увеличивается до значения П

В установившемся режиме (интервал

1Г времени t - t g) величины 11„1!мин

U„«фиксируются на постоянном уровне, определяемом внутренним сопротивлением нагрузки 8, частотой следования импульсов п и параметрами элементов схемы.

Таким образом, в процессе работы преобразователя на выходной шине 10 вырабатывается напряжение, меняющееся эа время одного цикла (1/п с) в пределах 1 „„= 11„,„„— U„«,.

Изменение нагрузки 8 происходит в моменты времени t,,t z — синхронно с появлением секундного импульса °

Детектор изменения нагрузки 33 (фиг.21 обеспечивает формирование иэ последовательностей импульсов пГц и I Гц сигналов, синхронных с сигналом 1 Гц и длительностью К/п с, где

К вЂ” число триггеров в регистре сдвига; для варианта схемы, изображенного на фиг.2 К 4. Регистр сдвига на триггерах 35-38 осуществляет задержку в схеме на 4 такта, а на триггерах 39,40 вместе с комбинационной логикой, выполненной на логических элементах 41-44, обеспечивают формирование на выходах триггера 40 импульсов длительностью 4/п с, синхронных с сигналом I Гц. Преобразователь уровня, выполненный на 1 1ОП-транзисторах 45 — 50 осуществляет смеще7695 6

55 ние уровня лог.I от 1,5 В до потенциала на шине IO около — 2,88 В.

Появление потенциала низкого уровня на выходе детектора изменения нагрузки 33 приводит к открыванию 11ОП-транзистора 32, благодаря чему на выходе инвертора на МОП-транзисторах 28,29 формируются перепады напряжения, обеспечивающие включение MOll-транзистора 2 синхронно с MOII-транзистором

5 (фиг.3). Поключение МОП-транзистора 2 с большим отношением 11/L уменьшает постоянную времени заряда конденсатора 7.

Сочетание в предлагаемом преобразователе малого уровня пульсаций С малой инерционностью открывает возможность создания на его основе кварцевых наручных часов, обладающих большим сроком службы и хорошей читаемостью жидкокристаллического индикатора, что обеспечит повышение технических -и потребительских качеств кварцевых наручных часов.

Формула изобретения

1. Преобразователь напряжения для кварцевых наручных часов, содержащий ячейку умножения, состоящую из четырех MOII-транзисторов и конденсатора, исток первого МОП-транзистора соединен с шиной источника питания, сток с первой обкладкой конденсатора и . стоком второго MOIL-транзистора, исток которого соединен с выходной шиной,исток третьего МОП-транзистора соединеной с общей шиной, второй обкладкой конденсатора и стоком четвертого МОП-транзистора, исток которого соединен с шиной источника питания, преобразователь уровней, на выходе которого включен пер" вый инвертор, выход которого соединен с затвором второго MOII-транзистора, цепь питания соединена с выходной шиной, и кбльцевой генератор, выполненный в виде цепочки из четырех последовательно соединенных инверторов, включенных между выходом и первым входом элемента ИЛИ-HF, второй вход которого соединен с первым выходом делителя частоты, к входу которого подключен выход кварцевого генератора, а также сглаживающий конденсатор, который включен между выходной и общей шинами, отличающийся тем, что, с целью улучшения качества

1497695 напряжения на выходе устройства путем уменьшения пульсаций и времени нарастания при увели ении нагрузки, в него введены .детектор изменения нагрузки, ключевой элемент, формиро5 ватель, щестой и седьмой инверторы и дополнительный M0Il-транзистор, сток которого соединен со стоком, исток с истоком второго МОП-транзистора, а затвор — с выходом шестого инвертора, вход которого соединен с выходом преобразователя уровней, первый инвертор соединен с общей шиной через ключевой элемент, вход которого 15 соединен с выходом детектора изменения нагрузки, седьмой инвертор вклю-1 чен между первой обкладкой конденсатора и общей шиной, его вход соединен с с затвором третьего МОП-транзисто20 ра и точкой соединения второго и третьего инверторов кольцевого генератора, а выход соединен с затвором первого МОП-транзистора, выход элемента ИЛИ-НЕ соединен через формирователь с выходами преобразователя уровней, а первый инвертор кольцевого генератора имеет второй вход, который соединен с затвором дополнительного МОП-транзистора.

2. Преобразователь по п.1, о т л и ч а ю шийся тем, что преобразователь уровней выполнен в виде триггера.

3. Преобразователь по п.1, о т л ич а ю шийся тем, что формирова35 тель выполнен в виде триггера.

4, Преобразователь по п.1, о т— л и ч а ю шийся тем, что детек тор изменения нагрузки содержит ре гистр сдвига, который выполнен на

D-триггерах, два D-триггера, для инвертора, два элемента И и преобразователь уровней, тактовый вход триггеров регистра сдвига соединен с выходом первого элемента И, первый вход которого соединен с инверсным выходом последнего триггера и D-входом первого триггера регистра сдвига, второй вход через первый инвертор соединен с первым выходом делителя, а третий вход соединен с вторым выходом делителя и через второй инвертор — с первым входом второго элемента И, второй вход которого соединен с вторым входом первого элемента И, тре1ий вход — с прямым влжодом последнего триггера регистра, а вижод соединен с тактовым входом первого D-триггера, D-вход которого соединен с третьим входом второго элемента И, R-вход — с первым входом первого элемента И, а прямой выход — с R-входами триггеров регистра сдвига, инверсный выход предпоследнего триггера регистра сдвига соединен с D-входом второго

D-триггера, тактовый вход которого соединен с выходом первого элемента

И, а выходы — с входами преобразователя уровней.

1497695 дк юченнов состояиое

Составитель И.Войтович

Редактор А.Долинич Техрец M.Ходанич

Корректор M.éàðîøè

Заказ 4453/53 Тираж 646 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

Состаюное

НОП Np-р0 2

nC moue

ФП тр-рИ4 Я

Cdстояюе

ПОП ер-рв1 13

Выход деаеквора

ИЗНВНВНУЯ нагрузки Я

2 йгЩ доителя Э

У= 1tu

1 дылд делителя 6

/ и/а г г ЫА 4 1 5 4=2 С3 ф У

Фиг.ю