Амплитудный селектор наложенных импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и предназначено для амплитудного анализа исследуемого сигнала. Целью изобретения является повышение точности дискриминации по амплитуде наложенных импульсов. Цель достигается тем, что в амплитудный селектор, содержащий амплитудный анализатор с распределителем, шифратором и подключенными к ним мультиплексором и источниками опорного напряжения, введены элемент задержки, компаратор и формирователь заднего фронта. С их помощью производится дополнительный анализ исследуемого сигнала, на основании чего формируется дополнительный импульс, корректирующий амплитуду выходного сигнала источника опорного напряжения в момент наложения отклика "хвоста" предыдущего импульса на последующий. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

Ы1 4 " "3 К 5/-"

ВСЕСОЮЗНАЯ

ПАТЕНТНе- ТЕ *NECiiAH

БИБЛИО I:

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1(21) 4326413/24-21 (22) 12.11.87 (46) 30.07,89. Бил ° N 28 (7I) Специальное конструкторско-технологическое бюро Физико-механического института АН УССР (72) И.В.Кедровский, О.К.Куценко и 10,В.Минеев (53) 621 .318 (088.8) (56) Авторское свидетельство СССР

N - 1420562, кл. Н 03 К 5/24, 24.04.87.

Авторское свидетельство СССР

М 790228, кл. Н 03 К 5/22, 29.04.87. (54) АМПЛИТУДНЫ 1 СЕЛЕКТОР НАЛОЖЕННЫХ

ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и предназначено для

Изобретение относится к автоматике и телемеханике и касается, в частности, задачи построения специализированных анализаторов импульсных сигналов.

Целью изобретения является повышение точности дискриминации по амплитуде наложенных импульсов.

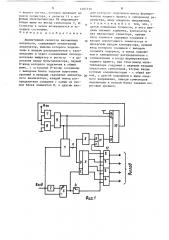

На фиг.! представлена блок-схема селектора; на фиг.2 — временные зависимости его основных сигналов.

Амплитудный селектор наложенных импульсов содержит амплитудный анализатор 1, элемент 2 задержки, компаратор 3, формирователь 4 заднего фронта, распределитель 5 с запомии нанием,шифратор 6 2 -п, аналоговые

„„SU„„1497730 А 1. амплитудного анализа исследуемого сигнала. Целью изобретения является повышение точности дискриминации по амплитуде наложенных импульсов. Цель достигается тем, что в амплитудный селектор, содержащий амплитудный анализатор с распределителем, шифратором и подключенными к ним мультиплексором и источниками опорного напряжения, введены элемент задержки, компаратор .и формирователь заднего фронта.

С их псмощью производится дополни— тельный анализ исследуемого сигнала, на основании чего формируется дополнительный импульс, корректирующий амплитуду выходного сигнала источни- О

® ка опорного напряжения в момент наложения отклика "хвоста предыдущего импульса на последующий. 2 ил. сумматоры 7, 8, блок 9 задания пороговых уровней, мультиплексор 10, регистр ll, блок 12 элементов И.

Входы амплитудного анализатора 1 образуют шину, подключенную на распределитель 5 с запоминанием и— через ши*ратор 6 2 -п — íà D-входы в регистра 11, выход которого соединен с адресным входом мультиплексора 10; первый D-вход мультиплексора 10 подключен к общей шине, остальные D-входы соединены с выходами блока 9 задания пороговых уровней и входами сравнения анализатора 1; каждый выход распределителя 5 соединен с одним из входов блока 12 элементов И.

Вход элемента 2 задержки соединен с

149773 нх дом lиализяторя 1 и одним из нходон компярят<>ря 3, выход которого соединен <: синхровходом распределителя 5 с запоминанием, а чере форми5 ронятель 4 зяднего фронта — с синхронходом регистра ll и всеми другими входами блока 12 элементов И; выход элемента 2 задержки подключен к другому входу компяратора 3; выход мультиплексора 1О соединен с одними из входов аналоговых сумматоров 7, 8, ня другой вход сумматора 7 подключено опорное напряжение, а другой вход уммяторя 8 подсоединен к общей шине; выходы блока 12 элементов И являются нь<ходами селектора н целом.

Распределитель 5 с запоминанием может быть устройством, состоящим из последовательно соединеннь<х тактируе- 20 мого параллельного регистра, шифря« тора 2 -II и с бстненно распределителя.

Назначением блока 5 является запоминание унитарного кода íà выходе анализатора, преобразование н определен- 25

tl <1 ный момент времени этого кода н 1 иэ п для управления блоком 12 элементов И.

Входная импульсная последовательность, состоящая из сигналов с крутым ЗР передниМ фронтом и пологим задним срезом, называемым хвостом", поступает на вход анализатора 1. При больших интенсивностях потоков таких импульсов возникает эффект наложения, 35 когда амплитуда очередного импульса складывается с "хвостами редыдуших импульсов, служащих н этом случае своеобрязнь(м пьедесталом. Несмотря на я э, что величина хвоста до- 40 вольно быстро спадает, при соответствую<чих интенсивностях потока оня может заметно увеличить амплитуду наложеннь(х импульсов, что н ряде случаен приводит к существенному иска- 45 жанию ямчлиту7 ного распределения.

Анализатор 1 состоит из набора компараторон, уровень срабатывания которых выбран нярастающ<им и определяется блоком 9 задяния пороговых уровней.

Сумматор 8 необходим для физической реализуемости селектора и служит для обеспечения прохождения тока по цепи.

Селектор работает Следующим образом.

Входной сигнал (фиг.2) поступает одновременно на анализатор l, элео 4 мент 2 задержки, компярятор 3. Когда напряжение на выходе элемента 2 задержки превысит входное, срабатывает компяратор 3, передний фронт которого записывает выходное состояние анализатора 1 в распределитель 5. Выходной сигнал распределителя 5 откры нает только тот элемент И блока 12, который соответствует старшему сработаншему компарятору анализатора 1. .Затем входной сигнал спадает фиг.2).

Если н этот момент появляется новый импульс, то он накладывается на хвост предь(дущего. Коь(паратор 3 возвращается н перноначяльное состояние, я формирователь 4 заднего фронта генерирует импульс, который через соответствующий открытый элемент

И блока 12 поступает на выход селектора. Одновременно импульс формирователя 4 заносит в регистр 11 преобразованное шифратором 6 в двоичный позиционный код значение выходного унитарного кода анализатора

l. По выходному коду регистра 11 мультиплексор 10 подключает напряжение порогового уровня того старшего компарятора, который еш< не отключился н момент наложения очередного импульса, на выходы аналогoBhlx суиматорон 7,8. Сумматор 7 складывает напряжение Ц„„ с опорным и подает

:ммиронанное значение ня один вход блока 9, а сумматор З повторяет выходное напряжение U мультиплексора 10 и подключает его на другой вход блока 9, скомпенсировав тем самым величину пьедестала . Теперь анализатор 1 будет аналиэиронать очередной импульс с учетом наложения °

Лальнейшая работа протекает так, как было описано ныше. Компаратор 3 выделяет момент перегиба входного импульса, распределитель 5 вь(бирает соответствующий элемент блока 12. Если опять происходит на- ложение, то формирователь 4 вновь генерирует импульс, который проходит через открытый элемент И блока !

2 и записывает соответствующий код в регистр 11, а мультиплексор 10, сумматоры 7,8 и блок 9 компенсируют новое значение «хвоста« в момент наложения. Если же наложения не происходит, то компаратор 3 сбрасывается, когда напряжение с выхода элемента 2 задержки сравняется с входным, близким к нулевому. Формирователь

l497730

4 выдает сигнал, который проходит на выход селектора, а регистр ll с поощью мультиплексора IO подключает общую шину на выход сумматоров 7, 8.

Селектор в целом возвращается в исходное состояние.

Р и у л а и з о б р е т е н и я

Амплитудный селектор наложенных импульсов, содержащий амплитудный анализатор, выходы которого подключены к входам распределителя с запоминанием и через соединенные последовательно шифратор и регистр — к адресному входу мультиплексора, первый

D-вход которого подключен к общей шине, а остальные Р-входы соединены с выходами блока задания пороговых уровней и входами сравнения амплитудного анализатора, каждый выход распределителя соединен с одним иэ входов блока элементов И, к другим входам которого подключен выход формирователя заднего фронта и синхровход ререгистра, шину опорного напряжения, 5 отличающийся тем что с

1 Ф целью повышения точности, в него введены элемент задержки, компаратор и два аналоговых сумматора, причем вход элемента задержки соединен с б входом амплитудного анализатора и инверсным входом компаратора, прямой вход которого соединен с выходом элемента задержки, а выход подключен к синхровходу распределителя с

)5 запоминанием и входу формирователя заднего фронта, при этом выход мультиплексора соединен с первыми входами аналоговых сумматоров, вторые входы которых соединены: один — с общей шиэп ной, а другой подключен к шине опорного напряжения, выходы сумматоров подключены к входам блока задания пороговых уровней. 497730

О и, О

Цс

u „

О

Qg

Це

О

Мр

Фиг. 2

Составитель F..Ìàðêèí

Редактор А.Маковская Техред А.Кравчук

Корректор И.Горная чаказ 4456/55 Тираж 884 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

11303 5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент", г.ужгород, ул. Гагарина,101