Способ контроля логических схем

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для контроля и диагностики логических схем. Способ реализован в устройстве. Цель изобретения - расширение функциональных возможностей и повышение достоверности контроля за счет возможности обнаружения отклонения логических уровней и времени срабатывания объекта контроля от допустимых значений, для чего объединяют электрически все контролируемые входы и выходы объекта контроля через разнономинальные емкости, к общей точке которых подключают суммирующий резистор, снимаемое напряжение которого принимают за информативный параметр. Сравнивают его с эталоном и при их совпадении считают контролируемую схему исправной. 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 01 R 31/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ FIGHT СССР (21) 4243945/24-21 (22) 11.05.87 (46) 07.08.89. Бюл.М 29 (71) Рязанский радиотехнический институт (72) В.А.Линьков и Г.А.Филин (53) 621.317.799(088.8) (56) Гордон, Надиг. Локализация неис- правностей в микропроцессорных системах при помощи шестнадцатиричных ключевых кодов. Электроника. — М.:

Мир, М 5, 1977, с.23-33. (54) СПОСОБ КОНТРОЛИ ЛОГИЧЕСКИХ СХЕМ (57) Изобретение может быть исполь зовано для контроля и диагностики логических схем. Способ реализован в

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля и диагностики логических схем, Цель изобретения — расширение функциональных возможностей и повышение достоверности контроля за счет возможности обнаружения отклонения логических уровней и времени срабатывания объекта контроля от допустимых значений.

Способ контроля логических схем осуществляется следующим образом.

Объединяют электрически все контролируемые входы и выходы объекта контроля через разнономинальные емкости, к общей точке которых подключают суммирующий резистор. Подают тестовые воздействия непосредственно на входы объекта контроля ° Напряжение

„„SU„„! 499287 А 1

2 устройстве. Цель изобретения — расши" рение функциональных возможностей и повьппение достоверности контроля за счет возможности обнаружения отклонения логических уровней и времени срабатывания объекта контроля от допустимых значений, для чего объединяют электрически все контролируемые входы и выходы объекта контроля через разнономинальные емкости, к общей точке которых подключают суммирующий резистор, снимаемое напряжение которого принимают за информативный параметр, Сравнивают его с эталоном и при их совпадении считают контролируемую схему исправной. 2 ил. на суммирующем резисторе, представляющее сумму преобразованных входных и выходных сигналов объекта контроля принимают за информативный параметр.

Сравнивают получаемый информативный параметр с эталоном и при их совпаде- © нии считают контролируемую схему ис- © правной. 00

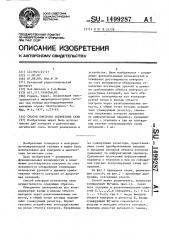

На фиг.l приведена схема, реализую- «й щая способ; на фиг.2 — временные диаграммы, поясняющие способ.

Способ можно реализовать, используя суммирующую RC-цепь (фиг.l). Такая цепь содержит и разнономинальных емко стей С.l,...,С.п (например, С.l ) С.2

) C.ï), где и — число. выводов объекта контроля и резистор R, Входы . суммирующей RC-цепи соединяются с входами и выходами объекта контроля.

Величины емкостей выбираются такими, 3 149928 чтобы они не оказывали отрицательного влияния на работу объекта контроля, Суммарный .сигнал, принимаемый за информативный параметр, снимается с резистора R, Так как С,1 > С ° 2 0 . ° 2 С.п, то и постоянные времени С; С.i R соответствующие каждому вЫводу объекта контроля различные и 1;,)2q 7... 7 c „..,1 О

Следовательно, сигналы, проходящие по каждому выводу объекта контроля, преобразовываются по экспоненциальному закону е с разными постоянными / ° времени У, Этим достигается однознач-g

1 ное соответствие получаемого одноканального сигнала, снимаемого с резис" тора R первоначальной многоканальной дискретной информации, снимаемой с входов и выходов логических схем, что ð исключает потерю первоначальной инфор-. мации. °

Анализ получаемого сигнала на наличие ошибок, а также уменьшения быстродействия или выхода амплитуды логи- 5 ческих "1" и "О" из допусковых: эон можно осуществить как наложением его на эталонный на экране осциллографа при ручном контроле, так и преобразовав этот сигнал в код с последую- 1О щей его обработкой любым из существующих методов (например, сравнив с эталонным кодом) °

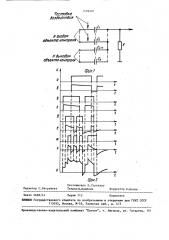

На фиг.2 .приведены временные диаграммы, поясняющие способ, для случая,15 когда информация снимается, например, с контролируемой схемы, имеющей четыре вывода.

На диаграммах показаны: а, в, д, ж — сигналы, снимаемые с 1, 2, 3 и 4- 4р го выводов схемы; б, г, е, з — сигналы, получаемые в результате преобра-зования сигналов а, в, д, ж с посто- .

7 4 янными времени соответственно 8, 0

rt гi 1 п

3t 4 ° rIPH"eM 1 Э = + и " суммарный сигнал, снимаемый с ре" зистора R.

Предлагаемый способ обладает большей чувствительностью к изменению параметров логических схем. Применение способа позволяет не только констатировать факт сбоя илн отказа логических элементов, но и заранее предвидеть воэможность отказа, что позволяет заблаговременно предупредить аварию, выявить от-. клонение логических уровней и быстродействия от допустимых значений как отдельных логических элементов, так и устройства в целом.

Формула изобретения

Способ контроля логических схем, в соответствии с которым подают тестовые воздействия непосредственно на входы объекта контроля, преобразуют вьмодные реакции, сравнивают полученный информативный параметр с эталоном, отличающийся тем, что, с целью расширения функциональных возможностей и повышения достоверности контроля эа. счет воэможности обнаружения отклонения логических уровней и времени срабатывания объекта контроля от допустимык значений, объединяют электрически все контролируемые входы и выходы объекта контроля через разнономинальные емкости, к общей точке которых подключают суммирующий резистор, снимаемое напряжение на суммирующем резисторе принимают за информативный параметр.

1499287

TecmoAie

6оздеостдоя

t(Node обэетлаконл рол л дьиййж одъеитаконтрол

Щог.2

Составитель Е. Строкань

Техред Л. Олийнык Корректор О.Ципле

Редактор С.11атрушева

Заказ 4688/45 Тираж 7)3 Подписное

ВНИИПИ Государственного Комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101