Устройство для проверки работоспособности блоков эвм

Иллюстрации

Показать всеРеферат

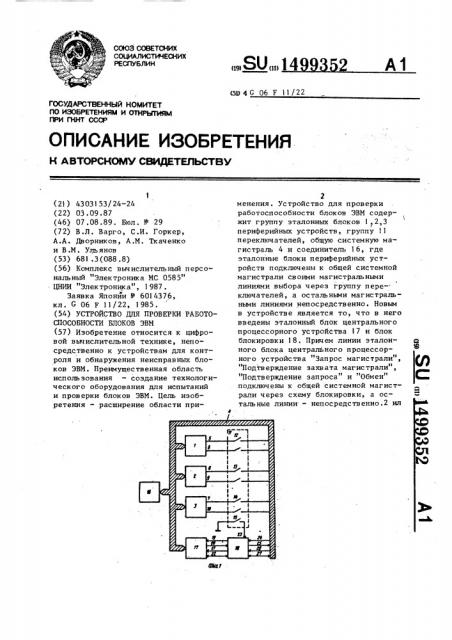

Изобретение относится к цифровой вычислительной технике, непосредственно к устройствам для контроля и обнаружения неисправных блоков ЭВМ. Преимущественная область использования - создание технологического оборудования для испытаний и проверки блоков ЭВМ. Цель изобретения - расширение области применения. Устройство для проверки работоспособности блоков ЭВМ содержит группу эталонных блоков 1,2,3 периферийных устройств, группу 11 переключателей, общую системную магистраль 4 и соединитель 16, где эталонные блоки периферийных устройств подключены к общей системной магистрали своими магистральными линиями выбора через группу переключателей, а остальными магистральными линиями непосредственно. Новым в устройстве является то, что в него введены эталонный блок центрального процессорного устройства 17 и блок блокировки 18. Причем линии эталонного блока центрального процессорного устройства "Запрос магистрали", "Подтверждение захвата магистрали", "Подтверждение запроса" и "Обмен" подключены к общей системной магистрали через схему блокировки, а остальные линии - непосредственно. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) (51) 4 G 06 F 11/22

ОПИСйНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCXOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (2 I ) 43031 53/ 24-24 (22) 03.09.87 (46) 07.08.89. Бюл. У 29 (72) В,Л, Варго, С.И. Горкер, А.А. Дворников, А.М. Ткаченко и В.М. Ульянов (53) 681,3(088 .8) (56) Комплекс вычислительный персональный "Электроника МС 0585"

ЦНИИ "Электроника", 1987.

Заявка Японйи У 6014376, кл. (06 F 11/22, 1985. (54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ БЛОКОВ ЭВМ (57) Изобретение относится к цифровой вычислительной технике, непосредственно к устройствам для контроля и обнаружения неисправных блоков ЭВМ. Преимущественная область использования — создание технологического оборудования для испытаний и проверки блоков ЭВМ. Цель изобретения — расширение области при2 менения. Устройство для проверки работоспособности блоков ЭВМ содер1 жит группу эталонных блоков 1 2,3 периферийных устройств, группу 11 переключателей, общую системную магистраль 4 и соединитель 16, где эталонные блоки периферийных устройств подключены к общей системной магистрали своими магистральными линиями выбора через группу пере-" ключателей, а остальными магистральными линиями непосредственно. Новым в устройстве является то, что в него введены эталонный блок центрального процессорного устройства 17 и блок блокировки 1 8. Причем линии эталонного блока центрального процессорного устройства "Запрос магистрали", "Подтверждение захвата магистрали", "Подтверждение запроса" и "Обмен" подключены к общей системной магистрали через схему блокировки, а остальные линии — непосредственно.2 ил

Устройство для проверки работоспособности блоков ЭВМ содержит группу эталонных периферийных блоков, в качестве которых применены стандартные из состава "Электроника MC0585": контроллер 1 видеотерминала, контроллер 2 накопителя на жестких магнитных дисках, контроллер 3 накопителя на гибких магнитных дисках, подключенные к общей системной магис;трали 4 магистральньии линиями 5 "Позиция 1 магистрали 30 выбрана", 6 "Позиция 2 магистрали выбрана", 7 "Позиция 3 магистрали выбрана", 8 "Модуль установлен в позицию 1", 9 "Модуль установлен в позицию 2", 10 "Модуль установлен в 35 позицию 3", через группу переключателей I 1,1содержащую переключатели

12-14 и переключатель 15, соединитель 16, выполненный в виде набора разъемов и подключенный к общей ма- 4О гистрали 4, эталонный центральный процессор 17,в качестве которого применен, стандартный модуль системный из состава "Электроника MC0585" подключенный к блоку 18 блокировки 45 своими магистральньии линиями 1 9

"Запрос магистрали", 20 "Разрешение захвата магистрали", 2! "Подтверждение запроса", 22 "Обмен", а остальньии магистральньии линиями — к об50 щей магистрали 4.

Блок 18 блокировки подключен к неподвижному контакту переключателя

15 входом 23 управления,к общей магистрали 4 линиями 24 "Запрос магистрали", 25 "Разрешение захвата магистрали", 26 "Подтверждение запро са" и 27 "Обмен". Блок 18 блокиров3 1499352

Изобретение относится к цифровой вычислительной технике, а именно к устройствам для контроля и обнаружения неисправных блоков ЭВМ и преУ

5 имущественно может быть использовано при создании технологического оборудования для испытаний и проверки блоков ЭВМ, Целью изобретения является расширение области применения путем обеспечения возможности проверки работоспособности периферийных уст-: ройс тв ЭВМ.

На фиг. 1 изображена функциональная схема устройства, на фиг.2схема блока блокировки.

4 ки (фиг ° 2) содержит времязадающую

RC-цепь 28, формирователи 29 и 30, первый 31 и второй 32 триггеры, резистор 33 подачи уровня логической единицы на входы раз решения п риемопередатчиков: первого 34 с инверсией и второго 36 и третьего 36 без инверсии магистральных сигналов "Запрос маг ис трали", "Подтв ержд ение запроса ", 1т и

Обмен, выполненных на микросхемах формирователей с тремя состояниями на выходе, инверторы 37 и 38, элементы

И-НЕ 39 и 40.

Устройство работает следующим образом .

При проверке блока центрального процессорного устройства, подключенного к соединителю 16, переключатели

12-15 должны быть замкнуты. В этом случае эталонные блоки 1-3 периферийных устройств ЭВМ подключены к общей системной магистрали 4 всеми магистральными линиями, а линия 23

"Включение эталонного блока центрального процессорного устройства" подключена к общей шине устройства через переключатель 15. При включе нии блоков питания и при подаче напряжения питания на устройство узел формирования протокола прямого доступа к памяти, выполненный на элементах 28-33, подключается через приемопередатчик 34, работа которого разрешена по входу "Выбор кристалла", к магистральньи линиям эталонного блока центрального процессорного устройства 1 9 "Запрос магистрали", 20 "Разрешение захвата магистрали" и 21 "Подтверждение запроса", на входы 9 установки в единицу триггеров 31 и 32 поступает импульс длительностью, определяемой величинами элементов R и С времязадающей цепи

28, под действием которого на инверсном выходе Q триггера 32 устанавливается уровень логического нуля, а на прямом выходе Q триггера 31— уровень логической единицы, которьй, поступая затем через приемопередатчик 34 с инверсией на линию 19 "Запрос магистрали", приводит к появлению в последней сигнала с активньи уровнем (уровень логического нуля).

Эталонный блок 17 центрального процессорного устройства по получении сигнала "Зайрос магистрали" с линии 1 9 устанавливает на линии 20

9352

6 отв етс тв енно .

55

5 149

"Разрешение захвата магистрали" сигнал низкого уровня (активный), который, п ос тупая ч е ре з п риемоп е реда тчик 34 на тактовый вход С триггера

32 устанавливает на его инверсном выходе g сиг нал с уров нем лог ич еской единицы, который, поступая затем на тактовый вход С триггера 31 и третий вход приемопередатчика 34, приводит к появлению на линии 21

"Подтверждение запроса" сигнала низкого уровня (активного) и к появлению на линии 19 "Запрос магистрали" сигнала высокого уровня (временные диаграммы соответствуют требованиям ГОСТ).

Магистральные приемопередатчики эталонного блока 17 центрального процессорного устройства переключаются в третье состояние, и блок

17 отключается от общей системной магистрали 4. Сигнал "Обмен" из общей системной магистрали 4 в оперативное запоминающее устройство, размещенное в эталонном блоке 17 центрального процессорного устройства, не поступает, так как формирователь

36 находится в третьем состоянии (отключен по входам "Выбор кристалла") . Проверяемый блок центрального процессорного устройства, подключенный через соединитель 1 6 к общей системной магистрали 4, организует все виды обмена с периферийными блоками 1 -3. Дальнейшая проверка испытуемого блока центрального процессорного устройства осуществляется обычным образом с использованием стандартного программного обеспечения.

При проверке блоков периферийных устройств работа устройства происхо-. дит следующим образом .

При проверке периферийного устройства, идентичного блоку 1 и подключенного к соединителю 16, размыкают переключатели 12 и 15, остальные пе- реключатели замыкают. При этом к общей системной магистрали 4 полностью подключаются эталонные блоки 2 и 3 периферийных устройств. Эталонный блок 1 подключен к общей магистрали

4 не полностью, а именно магистральные сигналы выбора этого блока "Модуль установлен в позицыо1" и "Позиция 1 магистрали выбрана" к нему не поступают и обмен с ним невозможен. При

Е5

35 включении блоков питания и подаче напряжений питания на схему блокировки работа приемопередатчиков (по входам "Выбор кристалла") 35 и 36 разрешена, а приемопередатчика 34 (соответственно элементов 28-32) запрещена. При этом сигналы Запрос магистрали" и "Подтверждение запроса" поступают из общей системной магистрали 4 на эталонный блок 17 центрального процессорного устройства, а сигналы Подтверждение захвата и Обмен" от указанного блока— в общую системную магистраль 4 через приемопередатчики 35 и 36, т.е. эталонный блок 1 7 централь ног о процессорного устройства организует все виды обмена в общей магистрали 4, к которой через соединитель. 16 подключен проверяемый периферийный блок, идентичный эталонному периферийному блоку 1 (последний, присутствуя в общей системной магистрали, активным устройством не определяется и обмену не мешает).

Дальнейшая проверка испытуемого блока и ериферийног о устройств а, и одключенного к соединителю 1 6, происходит обычным образом с использованием стандартного программного обеспечения. Проверка периферийных блоков ЭВМ, идентичных эталонным блокам 2 и 3, происходит аналогичным образом, только при этом размыкают переключатели 13, 15 или 14, 15 соПрименение предлагаемого устройства в составе технологического оборудования для производства ЭВМ позволяет проводить проверку и испытания блоков ЭВМ в условиях сохранения конфигурации и взаимосвязей реальной ЭВМ с использованием реальных пользовательской и тестовой операционных систем при изменении питающих напряжений и температур в заданных пределах, а также в условиях воздействия вибрации для обеспечения высокого качества выпускаемых 3BM .

Формула и з о б р е т е н и я

Устройство для проверки работоспособности блоков 3ВМ, содержащее группу эталонных периферийных блоков и группу переключателей, причем магистральные входы и выходы выбора каждого эталонного периферийного бло! 499352 ка группы соединены через переключатели группы с соответствующими входами и выходами выбора устройства для подключения к общей системной магистрали ЭВМ, остальные магистральные

5 входы и выходы каждого эталонного. периферийного блока группы соединены непосредственно с соответствующими входами и выходами устройства для подключения к общей системной магистрали ЭВМ, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения путем обеспе" чения возможности проверки работоспо- 15 собности периферийных устройств ЭВМ, оно содержит эталонный центральный процессор, переключатель и блок блокировки, содержащий времязадающую

RC-цепь, формирователь импульсов, 20 два триггера, три приемопередатчика, два элемента НЕ и два элемента И-НЕ, причем инверсный вход разрешения первого приемопередатчика, вход разрешения второго,прйемопередатчика и пер- 25 вые входы первого и второго элементов И-НЕ подключены к.шине единичного потенциала устройства и через переключатель к шине нулевого потенциала устройства, выход времяза- 30 дающей RC-цепи через формирователь импульсов соединен с S-входами первого и второго триггеров, Э-входы которых подключены к шине нулевого потенциала устройства. выход первого 35 триггера соединен с первым информационным входом первого приемопередатчика, первый инверсный выход которого и первый выход второго приемопередатчика подключены к входу запро- 40 са магистрали эталонного центрального процессора, первый информацион-, ный вход второго приемопередатчика подключен к входу запроса магистрали устройства для подключения к общей 45 системной магистрали ЭВМ, вторые информационные входы первого и второго приемопередатчиков подключены к выходу разрешения захвата магистрали эталонного центрального процессора, инверсный выход второго триггера соединен с С-входом первого триггера и третьим информационным входом первого приемопередатчика, :второй инверсный выход первого приемопередатчика соединен с С-входом второго триггера, второй выход второго приемопередатчика подключен к выходу разрешения захвата магистрали устройства для подключения к общей системной магистрали ЭВМ, третий инверсный выход первого и третий выход второго приемопередатчиков подключены к входу подтверждения запроса эталонного центрального процессора, третий информационный вход второго приемопередатчика, второй вход перв or о элем ен та И-НЕ и в ход п ерв or o элемента НЕ подключены к входу подтверждения запроса устройства для подключения к общей системной магистрали ЭВМ, выход первого элемента НЕ соединен с вторым входом второго элемента И-НЕ, вход-выход обмена эталонного центрального процессора подключен к. первому информационному входу и первому выходу третьего приемопередатчика, второй информационный вход и второй выход которого подключены к входу-выходу обмена устройства для подключения к общей системной магистрали ЭВМ, выход первого элемента И-НЕ соединен с инверсньм входом разрешения третьего приемопередатчика, прямой вход разрешения которого через второй элемент НЕ соединен с выходом второго элемента И"НЕ, остальные входы и выходы эталонного центрального процессора соединены непосредственно с соответствующими входами и выходами устройства для подключения к общей системной магистрали ЭВМ.

1 499352

Составитель Д. Ванюхин

Редактор В. Петраш Техред N.Xoäàíö÷ Корректор Т. Колб

Заказ 4695/48 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4