Устройство для формирования информации о полноте тестирования программ

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для проверки полноты тестирования управляющих программ, функционирующих в режиме реального времени. Цель изобретения - повышение быстродействия устройства путем совмещения во времени операций суммирования (счета числа обращений) значения по текущему адресу с записью сохраняемого значения по предыдущему адресу. Устройство содержит блок 3 памяти, сумматор 5, первый 7 и второй 8 элементы задержки, первый 1 и второй 4 буферные регистры, коммутатор 2 и одновибратор 6. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК аю П11 (5D4С 06F 1! 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 43 406 20/ 24-24 (22) 08 ° 1 2. 87 (46) 07, 08. 89, Бюл. N1 29 (71) Киевское проектно-конструкторское бюро автоматизированных систем управления (72) В.В. Галкин (53) 681 .3(088.8) (56) Авторское свидетельство СССР

Р 879592, кл. Н 03 М 1 2/02, 1 975.

Авторское свидетельство СССР В 1136171, кл. С 06 F 11/28, 1983. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ИНФОРМАЦИИ О ПОЛНОТЕ ТЕСТИРОВАНИЯ . ПРОГРАММ

2 (57) Изобретение относится к области вычислительной техники и предназначено для проверки полноты тестирования управляющих программ, функционирующих в режиме реального времени.

Цель изобретения — повьппение быстродействия устройства путем совмещения во времени операций суммирования (счета числа обращений) значения по текущему адресу с записью сохраняемого значения по предыдущему адресу. Устройство содержит блок 3 памяти, сумматор 5, первый 7 и второй 8 элементы задержки, первый 1 и второй 4 буферные регистры, коммутатор 2 и одновибратор 6. 2 ил.

3 1 49935

Изобретение относится к вычислительной технике и может использоваться для проверки полноты тестирования управляющих программ, функционирующих в режиме реального времени.

Целью изобретения является повышение быстродействия устройства .

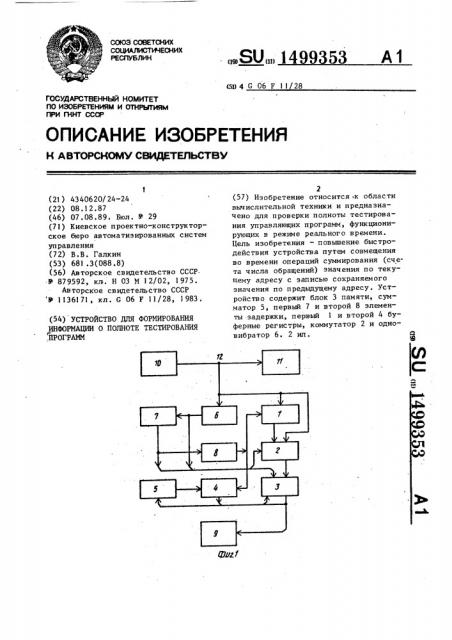

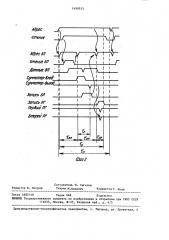

На фиг . 1 представлена структурная схема устройства, на фиг . 2— временная диаграмма.

Устройство содержит первый буферный регистр 1, коммутатор 2, блок 3 памяти, второй буферный .регистр 4, сумматор. 5, одновибратор 6, первый 7 и второй 8 элементы задержки, инструментальную ЭВМ 9, процессор 10, блок 11 памяти ЭВМ, интерфейс 12 тестируемой ЭВМ.

Устройство подключается к интер- 20 фейсу 12 тестируемой ЭВМ для получения .текущих адресов и необходимых сигналов управления типа "Чтение" при выполнении тестируемой программы в процессоре 10. Блок 3 памяти 25 устройства по своему объему равен объему блока 11 памяти и включает в себя схемы организации двухвходовых двунаправленньщ шин данных. Одновибратор обеспечивает формирование сиг- 30 нала "Чтение" необходимой длительности (зависящей от типа микросхем, ис пользуемых при построении блока 3 памяти). Первый элемент 7 задержки обеспечивает необходимую задержку сигнала "Чтение" для получения сигнала "Запись". Второй элемент 8 задержки выдает сигнал, разрешающий запись в буферные регистры новой информации после окончания записи данных в 40 блок 3 памяти.

В исходном состоянии второй регистр 4 обнулен, поэтому в цикл записи в блок 3 памяти записывается 0". Коммутатор разрешает прохождение на блок 3 памяти адреса с интерфейса 12 тестируемой ЭВМ. Сброс сигнала "Чтение" переключает коммутатор

2, на блок 3 памяти поступает адрес с первого регистра 1 во время поступления сигнала "Запись". Сброс сигнала "Запись" переводит коммутатор 2 в первоначальное состояние.

Цикл работы устройства состоит из трех тактов: чтение содержимого ячейки блонп ка 3 памяти по адресу, выставленному на интерфейс 121

3 4 запись 8 содержимого второго бу п ферного регистра 4 в блок 3 памяти по адресу, хранящемуся в Ьуферном регистре 1, полученному устройством в предыдущем цикле, и суммирование содержимого считанной ячейки блока 3 памяти с "1" на сумматоре 5", запись à результата суммирования во второй буферный регистр 4, текущего адреса в первый буферный регистр .

Таким образом, устройство позволяет производить запись в блок 3 памяти независимо от наличия сигнала

"Чтение" на интерфейсе 1 2 при повышении его быстродействия благодаря тому, что i > („

Устройство работает следующим образом.

Первоначально в блоке 3 памяти обнуляются все ячейки с помощью инструментальной ЭВМ 9. Ячейки блока 3 памяти работают как счетчики числа обращений процессора 10 к ячейке с этим же адресом блока 1 I памяти. Затем запускается тестируемая программа, при этом в цикле обращения к блоку 11 памяти на интерфейс 12 выставляется определенный адрес, который поступает на входы первого регистра

1 и через коммутатор на вход адреса блока 3 памяти. Сигнал "Чтение" с интерфейса поступает в одновибратор

6, который формирует импульс необходимой длительности для выполнения операции чтения на блок 6 памяти. Содержимое ячейки блока 3 памяти, считанное по поступившему адресу, поступает на первый вход сумматора 5, где к нему прибавляется "1 ", постоянно подаваемая на второй вход сумматора 5.

Во время выполнения операции суммирования с элемента 7 задержки на вход блока 3 памяти поступает сигнал

"Зались", коммутатор 2 разрешает прохождение предыдущего адреса с регистра 1 на адресный вход блока 3 памяти, который осуществляет запись содержимого регистра 4, хранящего результат предыдущей операции (в первоначальный момент времени "0") . .По окончании записи в памяти коммутатор переключается в предыдущее состояние, а элемент 8 вырабатывает сигнал, разрешающий запись результата суммирования с сумматора 5 во второй регистр

4 и текущего адреса в первый регистр 1, Формула изобретения

Устройство для формирования информации о полноте тестирования программ, содержащее сумматор, первый элемент задержки и блок памяти, причем информационный выход блока памяти является выходом устройства и соединен с информационным входом

1 сумматора, выход первого элемента задержки соединен с входом записи блока памяти, о т л и ч а ю щ е— е с я тем, что, с целью повышения быстродействия, в устройство введен одновибратор, второй элемент задержки, коммутатор, первый и второй буферные регистры, причем вход чтения устройства через одновибратор соединен с входом чтения блока памяти, управляющим входом коммутатора и с входом первого элемента задержки, выход которого через второй элемент задержки соединен с входами записи первого и второго буферных регистров, адресный вход устройства соединен с информационньм входом первого буферного регистра и первым информационным входом коммутатора, выход первого буферного регистра соединен с вторым информационньм входом коммутатора, выход которого соединен с адресным входом блока памяти, выход сумматора соединен с информационным входом второго буферного регистра, выход которого соединен с информационным входом блока памяти.

5 149935

Поступающий с интерфейса 12 адрес через коммутатор 2 поступает на адресный вход блока 3 памяти, при поступлении сигнала "Чтение" одновибратором 6 формируется сигнал "Чтение" блока памяти, и в дальнейшем цикл работы устройства повторяется.

С помощью предлагаемого устройства, подключаемого к тестируемой ЭВМ, обеспечивается получение необходимой информации без вмешательства в работу тестируемых программ. Тестируемые программы функционируют без изменений и вмешательств вспомогательных средств, Программное обеспечение инструментальной ЭВМ обеспечивает анализ полученной информации и ее обработку с целью реализации таких функций, как подсчет. числа выполнений каждого оператора, выявления невытолнившихся операторов или ветвей и выдачу соответствующих сообщений оператору, что дает возможность оценить эффективность проведенных тесто- 25 вых испытаний программ .

Программная независимость позволяет использовать устройство для широкого класса мини- и микро-ЭВМ, работающих в системах реального времени и различных языков программирования.

Возможность, оценки качества тестирования программ реального времени» позволит сократить расход труда и времени за счет. автоматизации и опти мизации этого процесса (сокращение объема тестов в 2-3 раза), Повышение качсства тестирования программ реаль3 6 ного времени (обнаружение до 70Х ошибок) позволит повысить уровень надежности всей системы в целом.

1499353

Адрес

Яаиние,бй

Редактор В. Петраш

Заказ 4695/48 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

47рес Ю

4mwue бЛ

Сучюл р-йяУ

Сумюлар-йлаУ

3олцсь Ю

3drruea Р/

7ephru Р/

Составитель И. Сигалов

Техред М.Ходанич . Корректор Т. Колб