Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации. Цель изобретения - повышение достоверности работы устройства путем использования однофазной синхронизации, уменьшения числа контролируемых сигналов при определении состояний заполнения и освобождения накопителя. Для достижения поставленной цели в устройство, содержащее накопитель, регистр, коммутатор, четыре элемента И-НЕ, счетчик адреса записи, счетчик адреса считывания, четыре триггера, введены генератор, четыре триггера, элемент ИЛИ, схема сравнения и элемент И-НЕ. В устройстве осуществляется логическое сравнение содержимого счетчика записи и считывания с формированием сигналов блокирования при достижении состояний переполнения и освобождения буфера. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„14993 (51) 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4351690/24-24 (22) 28. 1 2. 88 (46) 07.08.89. Бюл. У 29 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) Н.О. Собкевич и С.10. Шелестов (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф 1309032, кл. G 06 F 13/00, 1985.

Авторское свидетельство СССР

У 1 290339, кл. G 06 F 13/00, 1 985. (54) .УСТРОЙСТВО ДПЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации.

Изобретение относится к вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации.

Цель изобретения — повьппение достоверности работы устройства путем ис пользования однофазной синхронизации, уменьшения числа контролируемых сиг.налов при определении состояний заполнения и освобождения накопителя.

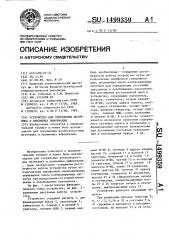

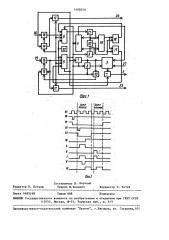

На фиг. 1 представлена функцио-.. нальная схема устройства; на фиг. 21 временные диаграммы работы устройства.

Устройство содержит регистр 1, информационный выход 2, накопитель 3, каимутатор 4, первый 5 и второй 6 триггеры, элемент ИЛИ 7, первый элеЦель изобретения — повышение достоверности работы устройства путем использования однофазной синхронизации> уменьшения числа контролируемых сигналов при определении состояний заполнения и освобождения накопителя.

Для достижения поставленной цели в устройство, содержащее накопитель, регистр, коммутатор, четыре элемента И-НЕ, счетчик адреса записи, счетчик адреса считывания, четыре триггера, введены генератор, четыре триггера, элемент ИЛИ, схема сравнения и элемент И вЂ” НЕ. В устройстве осуществляется логическое сравнение содержимого счетчика записи и считывания с формированием сигналов блокирования при достижении состояний переполнения и освобождения буфера. 2 ил. мент И-HE 8, счегчик 9 адреса записи, гамп шестой 10, седьмой 11 и восьмой 12 1 ф триггеры, четвертый 13 и пятый 14 элементы И-НЕ, третий 15 и четвертый р

16 триггеры, второй 17 и третий 18 элементы И-НЕ, схему 19 сравнения, 1 р пятый триггер 20, счетчик 21 адреса считывания, генератор 22 импульсов, выходы 23 и 24 синхронизации записи и считывания, синхронизирующие входы 25 и 26 запросов записи и считывания, информационный вход 27.

Устройство работает следующим об- Ь разом.

При включении питания триггеры 5, 6, 11,12,15,16 и 20 и счетчики 9 и

21 сброшены и находятся в исходном состоянии. На выходах 23 и 24 уста3 1 4993 59 навливаются с)п налы готовности к вьптолнению операций записи и считывания . Содержимое сч етч иков 9 и 21 равно нулю, схема 19 сравнения выдает сигнал "Равно", и элемент И-HE

18 вырабатывает сигнал "Буфер пуст", который подается на вход триггера 6 и блокирует его срабатывание. При поступлении с входа 26 запроса на считывание переключается триггер 1 6,. сигнал которого поступает на вход триггера 12, переключает его в состояние "Лог. l ". Вследствие этого сигнал на выходе 24 устройства переходит в !5 пассивное состояние, указывая на прием запроса считывания ° Выходной сигнал триггера 1 6 поступает также на вход триггера 8, однако срабатывания этого триггера не происходит, 20 так как на управляющем входе присутствует блокирующий сигнал элемента

И-НЕ 18.

При поступлении с входа 25 сигнала записи взводится триггер 1 5, выходной сигнал которого вызывает установку триггера 11. На выходе 23 сигнал принимает пассивное значение, указывая, что запрос записи принят. Одновременно выходной сигнал триггера 30

15 поступает на вход триггера 6, и по заднему фронту . сигнала генератора 22 происходит его срабатывание.

Выходной сигнал триггера 5 поступает на вход триггера 6, блокируя его 35 переключением, и на вход элемента

ИЛИ 7. Выходной сигнал элемента ИЛИ

7 поступает на вход выборки накопителя 3, на вход элемента И-НЕ 8 и вход триггера 10. 40

С приходом уровня "Лог.l" синхросигнала генератора 22 элемент И-НЕ

8 вырабатывает сигнал записи, поступающий на вход записи накопителя 3, 45 и происходит запись информации, присутствующей на информационном входе

27 устройства . С приходом отрицательной полуволны синхросерии генератора

22 элемент И-НЕ 8 снимает сигнал за50 писи, а по заднему фронту синхросигнала срабатывает триггер 1 О. Выходной сигнал триггера 1 Q поступает на входы сброса триггеров 5 и 6 и переводит их (в данном случае триггер 5) в нулевое 55 состояние. Одновременно сигнал триггера О через элемент И-НЕ 13 устанавливает триггер 15 в исходное состояние.

После установки триггера 5 элемент ИЛИ 7 прекращает выработку сигнала выборки накопителя 3 . Возврат триггера 1 О в исходное состояние происходит по следующему заднему фронту синхросерии генератора 22.

До этого момента запросы на запись и считывание не обрабатываются. После установки триггера 5 производится также инкрементирование счетчика 9 адреса записи. Схема 1 9 сравнения формирует сигнал неравенства содержимого счетчиков 9 и 21 . Этот сигнал поступает на входы элементов И-НЕ 17 и 18, и элемент И-НЕ

18 снимает блокирующий сигнал с входа триггера 6. Вследствие этого по очередному переднему фронту синхросерии генератора 22 происходит взведение триггера 6 и запускается цикл считывания из накопителя 3. Отличие от цикла записи состоит в данном случае в том, что не происходит формирование сигнала записи элементом

И-НЕ 8. После срабатывания триггера

10 происходит установка триггера 6 в исходное состояние. Выходным сигналом этог о тригг ера и роизв одится стробирование занесения считанной информации в регистр 1 и ее выдача на информационный выход 2 устройства.

В процессе работы п ериодич ески происходит переполнение, счетчики 9 и 21 используются для управления триг.—. гером 20 и устанавливают его в состояния "Лог,l" и"Лог.О".

Равенство содержимого счетчиков

9 и 21 в состоянии триггера 20

"Лог.1" соответствует переполнению накопителя 3, в противном случае это свидетельствует о том, что накопитель 3 пуст. Если адресуемое счетчиками 9 и 21 пространство больше емкости накопителя 3, для управления триггером 20 могут использоваться дифференцирующие цепи, срабатывающие по заднему фронту переключения старшего разряда счетчиков.

При переполнении накопителя 3 элемент И-НЕ 17 вырабатывает сигнал, блокирующий срабать!ванне триггера 5, и, таким образом, не может быть выполнена зап ись в как оп итель 3 .

Формула изобретения

Устройство для сопря кения н<.-rc«â€” ника и приемника информации, сояi-рч:i

5 l4 щее накопитель, выходом соединенный с информационным входом регистра,коммутатор, первый и второй информационные входы которого соединены соот-, ветственно с информационными выходами счетчиков адреса записи и считывания, счетными входами соединенных соответственно с выходами первого и второго триггеров, информационные входы которых соединены соответственно с выходами третьего и четверто1 го триггеров, и четыре элемента

И-НЕ, причем выход и первый вход первого элемента И-НЕ соединены соответственно с входом записи накопителя и и выходом первого триггера, выходы второго и третьего элементов

И-НЕ подключены соответственно к первым синхронизирующим входам первого и второго триггеров, вторые синхронизирующие входы которых соединены соответственно с выходами второго и первого триггеров, адресный вход накопителя соединен с выходом коммутатора, управляющий вход которого подключен к выходу первого триггера, информационный вход накопителя и установочный вход третьего триггера являются соответствующими входами устройства для подключения информационного и синхронизирующего выходов источника информации, выход регистра и установочный вход четвер-" того триггера являются соответствующими выходом и входом устройства для подключения к информационному входу и синхронизирующему выходу приемника инфо.рмации, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности работы устройства, в него введены генератор импульсов, схема сравнения, четыре триггера, элемент ИЛИ

993 59

10

40 и пятый элемент И-НЕ, причем первый и второй входы схемы сравнения соединены соответственно с информационными выходами счетчиков адреса записи и считывания, а выход схемы сравнения подключен к первым входам второго и третьего элементов Й-НЕ, вторыми входами соединенных соответственно с инверсным и прямым выходами пятого триггера, входы установки и сброса которого соединены соответственно с выходами переполнения счетчиков адреса записи и счетчика адреФ са считывания, выход генератора HM пульсов соединен с синхровыходами первого, второго и шестого триггеров и вторым входом первого элемента

И-НЕ, третьйк входом подключенного к выходу элемента ИЛИ, входу выборки накопителя и информационному входу шестого тригrера, выход которого соединен с входами сброса первого, седьмого и восьмого триггеров и первыми входами четвертого и пятого элементов И-НЕ, вторые входы и выходы которых подключены соответственно к выходам и входам сброса третьего и четвертого триггеров, а третьи входы — соответственно к выходам первого и второго триггеров, установочные входы седьмого и восьмого триггеров соединены соответственно с выходами третьего и четвертого триггеров, а выходы являются соответствующими выходами устройства для подключения к синхронизирующим входам залиси и считывания источника и приемника информации, выход . первого триггера соединен с первьм входом элемента ИЛИ, второй вход которого подключен к выходу второго триггера и синхровходу регистра.

1499359

guzZ

Составитель В. Вертлиб

Техред И.Ходанич

Редактор В. Петраш

Корректор Л. Патай

Заказ 4695/48 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðîä, ул. Гагарина,101

Й

4uzrt 1 1 цу жижи 1 Мжу1